简介:Linux环境下,高效管理多个源文件编译构建的关键在于熟练运用Makefile。本教程面向初学者,系统性地讲述了Makefile的基础结构、变量与模式规则、隐含规则、条件语句和函数等核心概念,同时介绍了清理目标、递归Make、最佳实践和调试技巧。通过学习Makefile,开发者能够自动化构建过程,提升开发效率和项目质量。

1. Makefile基础结构介绍

1.1 Makefile的定义与作用

Makefile是一个自动化构建文件,它指明了如何根据源代码文件生成可执行程序。它使用一种特定的语法来描述文件之间的依赖关系,并通过调用编译器和其他工具来自动化编译过程。

1.2 Makefile的基本构成

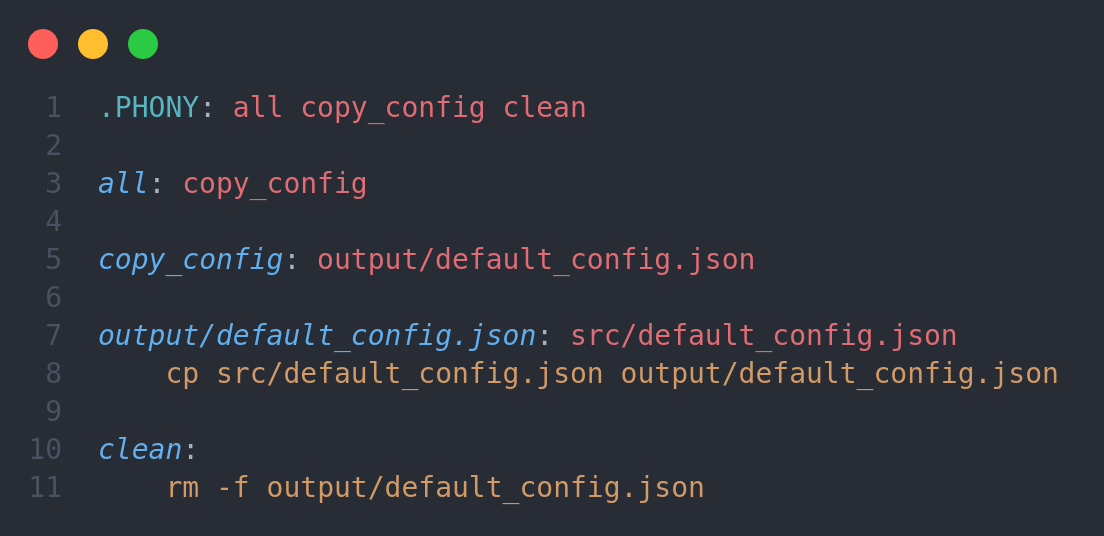

Makefile通常包含三个主要部分:目标(target)、依赖(dependencies)和命令(commands)。目标通常是编译出的文件名,依赖项列出了目标文件生成所需的源文件和头文件,命令则是一系列用于更新目标文件的shell指令。

# 示例代码块

target: dependencies

command1

command2

...

1.3 编写Makefile的基本步骤

- 定义目标和依赖:将需要生成的可执行文件或中间文件作为目标,并列出生成它们所需的源文件和头文件作为依赖项。

- 添加编译规则:在每个目标后添加一系列命令,用于执行实际的编译过程。

- 使用伪目标和模式规则:为了提高Makefile的灵活性和可重用性,可以使用伪目标和模式规则。

通过以上步骤,可以构建出一个简单的Makefile,它能够帮助开发者自动化编译和链接过程,节省重复操作的时间,并在项目中保持构建的一致性。

2. 变量与模式规则的应用

2.1 变量的定义和使用

2.1.1 简单变量的定义和引用

在Makefile中,变量提供了一种方便的方式来存储和引用文件名、编译选项、路径等信息。简单变量的定义通常遵循这样的格式:

VARIABLE_NAME = value

定义好变量后,在Makefile中可以使用 $(VARIABLE_NAME) 或 ${VARIABLE_NAME} 的方式来引用变量的值。

例如,假设有以下代码段:

CFLAGS = -Wall -g

SRC = file1.c file2.c

OBJ = $(SRC:.c=.o)

在这里, CFLAGS 是一个简单变量,包含了编译选项 -Wall 和 -g 。当编译程序时,这些选项会被自动添加到编译命令中。通过引用 $(CFLAGS) ,Makefile将自动替换为 -Wall -g 。

2.1.2 自动变量和特殊变量

Makefile中还有一些特殊的预定义变量,它们在规则执行时自动获取不同的值。这些变量通常被称为自动变量。以下是一些常用的自动变量:

-

$@:当前规则中的目标文件名。 -

$<:当前规则中的第一个依赖文件名。 -

$^:当前规则中的所有依赖文件名。 -

$*:当前规则中的模式目标(%)部分。

例如:

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

在这个例子中, $< 会自动替换为 %.c 规则中的第一个依赖文件名,而 $@ 会自动替换为对应的目标文件名。

特殊变量包括:

-

$$:在Makefile中,$$是转义字符,用于生成实际的$字符。 -

$?:当前目标的所有依赖文件中,比目标文件更新的依赖文件列表。 -

$@D和$@F:分别表示目标文件的目录部分和文件名部分。

通过理解这些自动变量的使用,可以进一步简化Makefile的编写,减少重复的代码量,使整个文件更加清晰易读。

2.2 模式规则的编写和理解

2.2.1 模式规则的概念和作用

模式规则是一种特殊的规则,用于描述如何为一组目标文件生成依赖关系和构建命令。它们使用 % 这个特殊字符来匹配一个或多个字符,使得一个规则可以适用于多个目标。

举个简单的例子:

%.o : %.c

$(CC) -c $(CFLAGS) $< -o $@

在这个模式规则中,任何以 .c 结尾的文件都会被编译成以 .o 结尾的对象文件。 $< 代表第一个依赖文件( .c 文件),而 $@ 代表对应的目标文件( .o 文件)。这样,只要提供 .c 文件列表,Makefile就可以自动应用这条规则生成相应的 .o 文件。

模式规则在大型项目中非常有用,因为它大大减少了需要显式定义规则的数量,从而提高了Makefile的可维护性。

2.2.2 模式规则的高级应用

模式规则可以进行更高级的应用,包括定义模式目标和模式依赖,以及使用模式来匹配目录和文件名中的模式。

一个典型的高级应用是在规则中嵌入条件判断,根据不同的条件应用不同的编译选项或者执行不同的命令:

%.o : %.c

ifeq ($(DEBUG), 1)

$(CC) -c $(CFLAGS) -g $< -o $@

else

$(CC) -c $(CFLAGS) -O2 $< -o $@

endif

在这个例子中,根据 DEBUG 变量的值决定是否添加 -g 选项以生成调试信息。

模式规则还可以与自动变量结合,实现更复杂的功能,例如自动删除所有由 .c 生成的 .o 文件:

clean:

rm -f *.o

这里, clean 规则的目标并不依赖于任何文件,而是一个伪目标,通常用于清除编译生成的文件。使用 rm -f *.o 命令,可以删除当前目录下所有 .o 文件。

总结来说,模式规则通过匹配特定的模式,大幅提高了Makefile的灵活性和表达力。正确地理解和应用模式规则,可以使Makefile的编写更为高效和优雅。

3. 隐含规则和覆盖方法

3.1 隐含规则的使用和理解

3.1.1 常见的隐含规则

隐含规则是Makefile中预设的规则,它能够自动处理常见的编译、链接等任务。隐含规则的存在,减少了用户需要编写和维护的规则数量,提高了工作效率。在常见的Makefile工具中,例如GNU Make,预定义了多种隐含规则,可以处理如C、C++、Fortran、Pascal等语言的编译。

一个典型的例子是C语言的编译过程。GNU Make默认认为所有的 .c 文件应该使用 cc -c 命令进行编译,生成 .o 文件。如果Makefile中没有显式定义编译规则,当需要编译 .c 文件时,Make会自动使用这条隐含规则。

# 隐含规则示例

.PHONY: all

all: myprogram

myprogram: main.o utils.o

$(CC) -o $@ $^

在这个简单的Makefile中,我们没有定义 main.c 到 main.o 的编译规则,Make会自动寻找隐含规则来编译 main.c 。

3.1.2 如何自定义隐含规则

尽管Make提供了许多有用的预定义隐含规则,但有时候默认的规则可能不符合特定项目的需求。在这种情况下,我们可以自定义隐含规则,以便更精确地控制构建过程。

自定义隐含规则需要使用 .DEFAULT_GOAL 和 .PRECIOUS 伪目标。 .DEFAULT_GOAL 用于指定make的默认目标,而 .PRECIOUS 用于声明在构建过程中不应删除的中间文件。

下面是一个自定义隐含规则的例子,其中定义了一个将 .cpp 文件编译为 .obj 文件的规则,这与默认规则编译为 .o 文件不同。

# 自定义隐含规则示例

.PHONY: all

all: myprogram

myprogram: main.obj utils.obj

g++ -o $@ $^

# 自定义编译规则,生成.obj而非.o文件

%.obj: %.cpp

g++ -c -o $@ $<

# 自定义链接规则,使用.obj文件而非.o文件

%.exe: %.obj

g++ -o $@ $^

在这个Makefile中,我们自定义了如何将 .cpp 文件编译为 .obj 文件,并指定了相应的链接规则。这样,当运行 make myprogram 时,Make会使用我们定义的规则来构建 main.obj 和 utils.obj ,然后链接它们生成 myprogram.exe 。

3.2 覆盖方法的使用和理解

3.2.1 覆盖方法的定义

覆盖方法是一种在Makefile中优先使用指定规则来替代隐含规则的方式。在某些情况下,我们需要对特定文件或文件类型应用特殊的编译选项或命令,这时可以通过覆盖方法来实现。

通过在Makefile中指定具体的命令序列来覆盖默认的隐含规则,这种做法被称为显式规则。显式规则提供了对构建过程更细致的控制。

3.2.2 如何使用覆盖方法

使用覆盖方法需要明确指定目标文件和它的依赖关系,并提供必要的命令序列。这样,即使存在隐含规则,Make也会优先使用显式定义的规则。

例如,我们想为一个特定的 .c 文件使用不同的编译选项,可以这样做:

# 使用覆盖方法示例

.PHONY: all

all: myprogram

myprogram: main.o utils.o

g++ -o $@ $^

# 显式规则覆盖隐含规则

main.o: main.c

gcc -c main.c -o main.o -O2 # -O2表示启用编译器的优化选项

在这个例子中, main.o 的生成不再依赖于隐含规则,而是由显式定义的规则来控制。使用 -O2 选项是为了让编译器进行代码优化。这样, main.c 在编译成 main.o 的过程中会应用这个优化选项,而其他 .c 文件则不受影响,仍然可以使用默认的隐含规则编译。

通过覆盖方法,我们可以为不同的文件制定不同的构建策略,这为项目的优化提供了极大的灵活性。

4. 条件语句和内置函数使用

4.1 条件语句的使用和理解

4.1.1 条件语句的定义和类型

条件语句在Makefile中扮演着重要的角色,它允许根据特定的条件来执行或者跳过Makefile中的特定规则。这种机制可以用来处理不同的编译环境,或者根据文件的存在与否来决定是否执行特定的目标。

在Makefile中,主要的条件语句是ifeq和ifneq。ifeq用来检查两个字符串是否相等,如果相等,则执行接下来的命令。ifneq正好相反,检查两个字符串是否不相等,如果不同,则执行接下来的命令。此外,还有一种条件语句if,它需要搭配make的-e参数使用,用于检查make变量是否已定义。

例如,以下是一个简单的ifeq条件语句的使用案例:

# 检查变量是否有定义

ifneq ($(FOO),)

echo "FOO is defined"

else

echo "FOO is not defined"

endif

在这个例子中,如果FOO变量被定义了,则输出”FOO is defined”;如果没有被定义,则输出”FOO is not defined”。

4.1.2 如何使用条件语句

在Makefile中使用条件语句可以使构建过程更加灵活。下面是一个在构建过程中根据系统类型选择不同编译参数的示例。

# 检查平台类型

ifeq ($(.Platform), Windows)

CFLAGS += -DWIN32

else ifeq ($(Platform), Linux)

CFLAGS += -DLINUX

endif

# 编译程序

all: program

program: main.o

$(CC) $(CFLAGS) main.o -o program

在上面的Makefile中,首先通过ifeq检查宏.Platform的值,并根据该值的定义来添加相应的编译标志。接下来根据平台设置的编译标志,调用编译器来编译目标文件。

使用条件语句可以简化复杂的构建流程,并允许Makefile在不同环境间轻松切换,提升构建脚本的可移植性和易用性。

4.2 内置函数的使用和理解

4.2.1 常见的内置函数

GNU Make提供了很多内置函数,它们极大地扩展了Makefile的功能。常见的内置函数有以下几个:

-

wildcard:用于获取匹配特定模式的文件列表。 -

patsubst:用于替换字符串中的模式。 -

notdir:用于去除路径中的目录部分。 -

dir:用于提取文件的目录路径。 -

suffix:用于提取文件的后缀名。 -

basename:用于获取不带后缀的文件名。 -

addprefix:用于在文件名前添加前缀。

下面是一个使用 wildcard 和 patsubst 函数的示例。

# 获取当前目录下所有的.c文件,并将.c后缀替换成.o后缀

SRC_FILES := $(wildcard *.c)

OBJ_FILES := $(patsubst %.c, %.o, $(SRC_FILES))

all: $(OBJ_FILES)

%.o: %.c

$(CC) -c $< -o $@

在这个例子中, wildcard *.c 会匹配当前目录下的所有 .c 文件,而 patsubst %.c, %.o, $(SRC_FILES) 则会把匹配到的文件名从 .c 后缀换成 .o 后缀。

4.2.2 如何使用内置函数

内置函数可以极大地增强Makefile的灵活性和功能性。下面通过一个示例展示如何使用内置函数 addprefix 来为一组目标文件添加统一的前缀。

# 假设我们有多个.o文件,但我们想将它们作为不同的目标重新命名

OBJ_FILES := file1.o file2.o file3.o

# 使用addprefix来添加前缀"mylib-"到每个文件名

NEW_OBJ_FILES := $(addprefix mylib-, $(OBJ_FILES))

# 创建一个新的目标"mylibrary"来链接这些文件

mylibrary: $(NEW_OBJ_FILES)

$(CC) -o $@ $^

%.o: %.c

$(CC) -c $< -o $@

在这个Makefile中, addprefix mylib-, $(OBJ_FILES) 将 mylib- 前缀添加到每个对象文件之前,生成新的目标文件列表。然后定义一个名为 mylibrary 的伪目标来链接这些文件,这样就形成了一个库文件。

使用内置函数可以简化Makefile中的字符串和文件名操作,使构建规则更加清晰易懂。正确使用内置函数能够有效提升Makefile的维护性以及构建效率。

5. Makefile高级应用和调试技巧

随着软件项目的复杂度增加,Makefile的高级应用和调试技巧变得尤为重要。这不仅能提高构建效率,还能帮助开发者更好地控制构建过程,并快速定位问题所在。

5.1 清理目标的定义和作用

在软件开发过程中,清理构建生成的中间文件和最终的可执行文件是一个常见需求,尤其是为了防止未来的构建被旧的文件干扰。这就是清理目标的用武之地。

5.1.1 清理目标的定义

清理目标是一个特殊的伪目标,在Makefile中用 .PHONY 声明。它通常定义了一系列删除文件的规则,这些文件可能是编译过程中产生的目标文件(.o)或最终的执行文件。

.PHONY: clean

clean:

rm -f *.o myprogram

在上面的Makefile示例中, clean 是一个清理目标,用于删除所有的 .o 文件和名为 myprogram 的程序文件。

5.1.2 清理目标的作用

清理目标的主要作用是让构建过程从一个干净的状态开始。这样可以确保不会因为旧的目标文件而引入未预期的行为。同时,当开发者决定更改构建配置或引入新的编译器标志时,清理目标能够帮助清除可能由旧的标志生成的文件。

5.2 递归Make的调用和层次化构建

当一个项目非常庞大,包含多个子目录,每个子目录都有自己的Makefile时,如何组织这些Makefile以高效地构建整个项目就成为了问题。

5.2.1 递归Make的调用

递归Make涉及到在主Makefile中调用子目录的Makefile。这通常通过 make -C 命令实现,该命令允许Makefile在指定的目录中执行。

SUBDIRS = src utils doc

all: myprogram

myprogram: $(SUBDIRS)

for dir in $(SUBDIRS); do \

$(MAKE) -C $$dir; \

done

.PHONY: myprogram

在上述Makefile示例中, SUBDIRS 变量包含了子目录列表。主目标 myprogram 依赖于所有子目录的构建,使用 for 循环和 make -C 命令递归地调用每个子目录中的Makefile。

5.2.2 层次化构建的理解和应用

层次化构建允许开发者通过分解大型项目为多个模块来管理复杂性。每个模块都有自己的Makefile,这些Makefile共同协作以构建整个项目。主Makefile负责协调这些模块的构建顺序,并确保所有依赖关系都被满足。

5.3 Makefile编写最佳实践

编写高效且可维护的Makefile是开发者的必备技能之一。以下是一些最佳实践建议。

5.3.1 编写Makefile的技巧

- 使用变量来存储编译器标志、路径和文件名等重复使用的元素。

- 为频繁使用的命令创建缩写,以减少重复代码。

- 避免在Makefile中硬编码路径和特定的系统信息。

5.3.2 Makefile的维护和优化

- 定期审查和清理不再需要的规则和变量。

- 使用

include指令来共享通用的Makefile片段,提高可维护性。 - 为复杂的构建步骤编写文档,以便团队成员理解。

5.4 Makefile调试技巧

当Makefile的构建过程出现错误时,快速定位并解决问题显得尤为重要。

5.4.1 Makefile的调试方法

- 使用

make -n命令来打印将要执行的命令,而不是实际执行它们,以检查Makefile的逻辑。 - 使用

make --debug选项可以获取详细的调试信息。 - 当指定目标不存在时,Makefile不会报错。可以使用

.DEFAULT_GOAL变量设置默认目标,来强制Makefile显示错误信息。

5.4.2 Makefile的常见问题及解决方法

- 问题:目标文件比依赖文件还新,导致不重新构建。

解决:检查时间戳,使用make -B强制重建所有目标。 - 问题:变量作用域导致的问题。

解决:使用:=代替=来确保变量值在当前行就被评估,避免后续的变量扩展影响当前变量值。 - 问题:依赖关系不正确或不完整。

解决:使用make --dry-run和make --print-data-base检查依赖关系,确保每个目标都正确地列出了所有依赖项。

通过上述的高级应用和调试技巧,开发者可以更有效地管理复杂的构建环境,从而提高工作效率和项目的构建质量。

简介:Linux环境下,高效管理多个源文件编译构建的关键在于熟练运用Makefile。本教程面向初学者,系统性地讲述了Makefile的基础结构、变量与模式规则、隐含规则、条件语句和函数等核心概念,同时介绍了清理目标、递归Make、最佳实践和调试技巧。通过学习Makefile,开发者能够自动化构建过程,提升开发效率和项目质量。

4231

4231

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?