简介:PCI Express(PCIe)是高速计算机设备间通信的关键接口标准,用于显卡、网卡和硬盘等。作为现代计算平台的核心部分,它提供远超传统PCI总线的带宽和更低延迟。本文详细解读了PCIe体系结构的基础、分层结构、速度等级、电压和信号规范、拓扑结构、中断和流控制、热插拔和功率管理,以及存储应用和未来发展。深入理解PCIe对于计算机系统设计和性能优化至关重要。

1. PCIe总线基础

PCI Express(PCIe)是一种高性能的串行总线接口标准,用于连接主板和高速外围设备。它是PCI(外围组件互连)标准的继任者,拥有更高的传输速率和更低的资源占用。本章将从基础层面介绍PCIe总线的核心概念和特点,为读者构建一个初步的理解框架。

PCIe总线的核心特征

- 串行通信 :PCIe采用串行通信方式,区别于PCI的并行通信方式,有效提升了数据传输的效率和距离。

- 点对点连接 :PCIe总线的每个设备都通过独立的链接直接与根复合体连接,这使得数据传输更为直接和高效。

- 可扩展的带宽 :PCIe通过增加通道(lane)数量来线性扩展带宽,允许不同级别的带宽需求与设备相匹配。

这些核心特征构成了PCIe总线技术的基础,并影响了整个计算机系统的设计与性能优化。随着PCIe技术的不断发展和应用,对这些基础概念的深入理解显得尤为重要。接下来的章节将逐步深入探讨PCIe的各个方面,从而为IT专业人员提供实用的参考和洞察。

2. PCIe与传统PCI的区别

2.1 历史发展对比

2.1.1 PCI的发展历程

PCI(Peripheral Component Interconnect)总线技术自从20世纪90年代初问世以来,一直是个人电脑和其他计算机系统中连接外围设备的标准接口之一。其设计初衷是为了替代老旧的ISA总线,提供了更高的数据传输速率和更好的系统扩展性。在发展历程中,PCI经历了多个版本的迭代,每个版本都伴随着性能的提升和功能的增强。例如,PCI 2.0标准将总线频率从33MHz提升至66MHz,而PCI 3.0(通常称为PCI-X)更是将性能提升至一个全新的水平,其速度最高可达133MHz。尽管PCI在当时代表了技术进步,但随着计算机硬件性能的不断提高,尤其是图形处理单元(GPU)对高带宽需求的日益增长,PCI总线逐渐暴露出了它的局限性。

2.1.2 PCIe的出现和创新点

为了满足新一代计算环境对高速、高带宽的迫切要求,PCIe(PCI Express)技术应运而生。PCIe基于串行通信技术,相较于传统PCI的并行通信,大大提高了数据传输效率,减少了信号线的数量,并且在本质上更易于扩展。与PCI技术不同,PCIe不仅可以用于主板上,也可以用于服务器、工作站以及各种嵌入式系统。它的出现标志着计算机互连技术的一次重大飞跃。创新点主要体现在:

- 高带宽:PCIe 1.0版本就提供了2.5 GT/s(Giga Transfer per Second)的数据传输速率,远超过PCI-X的133 MT/s(Mega Transfer per Second)。

- 可扩展性:利用Lane的概念,PCIe可以轻松扩展至x2, x4, x8, x16等不同通道配置,以满足不同设备对带宽的需求。

- 点对点连接:每一设备都有一个独立的专用通道,可以实现更高的吞吐量和更佳的性能表现。

2.2 技术层面的差异

2.2.1 总线架构的变革

在PCI时代,计算机内部的总线架构基本上是共享的并行架构,所有连接到总线上的设备共同使用同一条信号线进行数据传输。这种架构虽然简单,但在多设备同时传输数据时会产生冲突,影响性能。PCIe则采取了创新的点对点串行架构,每个设备都拥有独立的通道。这种架构消除了总线共享的瓶颈,并且使得数据传输的速率得到了极大的提升。

PCIe的架构还支持虚拟通道技术,这意味着在同一个物理连接上可以同时存在多个独立的数据流。每个设备和其对应的端口可以建立多个虚拟通道,进一步优化了资源的使用效率和数据传输的性能。此外,由于PCIe使用了高速串行通信,它能够更好地适应未来的扩展需求,支持更高的传输速率和更远的传输距离。

2.2.2 数据传输机制的演进

在数据传输机制方面,PCIe采用了基于包的传输机制,每个数据包包含了地址、控制以及实际的数据内容。这种机制支持了更有效的数据封装与传输,同时也带来了更好的错误检测和恢复能力。与传统PCI总线依赖于连续信号传输不同,PCIe的数据传输是基于“事务”的概念,即数据包的发送和接收是独立的事务,每个事务都包含请求和响应两个阶段。这种分离的事务机制不仅提高了数据传输的灵活性,还允许系统内部的硬件可以并行处理多个事务,大大提高了系统的整体性能。

PCIe还引入了流量控制机制,确保发送端和接收端能够有效地匹配速率,避免数据丢失。流量控制和错误检测机制是PCIe能够在高速传输的同时保持高可靠性的关键。随着技术的演进,PCIe已经从最初的支持点对点连接,发展到了支持多层交换网络,这种灵活性为PCle技术在多领域应用提供了坚实的技术基础。

3. PCIe的分层结构介绍

PCI Express (PCIe) 是一种高速串行计算机扩展总线标准,它的分层结构允许它在不同的硬件和软件层面上进行操作和通信。深入了解PCIe的分层结构可以帮助我们更好地理解其工作原理和优化方法。

3.1 物理层概述

3.1.1 链路结构和信号定义

物理层是PCIe通信链路的最低层,负责数据的实际传输。链路由一组差分信号线组成,称为lane。每个lane包括一对发送器(Tx)和接收器(Rx)进行点对点通信。基本的PCIe连接通常包括x1, x4, x8, 和x16等不同数量的lane配置,以支持不同带宽的需求。

信号定义方面,主要信号包括:

- Transmitter Output (TXP/N): 发送差分对。

- Receiver Input (RXP/N): 接收差分对。

- Common Mode Termination: 共模终端电阻,用于减少EMI和维持信号完整性。

- Supply Voltage and Ground: 电源和地线。

3.1.2 电气特性和物理层协议

电气特性主要包括信号的传输速率、电压水平以及信号质量。PCIe使用的是低压差分信号(LVDS),这种信号方式可以提高数据传输速度并降低功耗。物理层协议定义了信号的电气特性,例如,标准PCIe 3.0的传输速度是8 GT/s(Giga Transfers per second),使用的电压为0.8V。

PCIe物理层协议还包括了对链路初始化和训练的描述,它确保设备间通信的同步和稳定性。物理层也负责处理物理编码子层(PCS)的信号编码和解码工作。

3.2 数据链路层详解

3.2.1 帧的构建和传输

数据链路层位于物理层之上,它负责确保数据包的正确传输。在PCIe中,它通过构建和传输帧来实现这一点。每个帧都是由一个16字节的Header和0到4096字节的数据(包含在Payload内)组成。Header包含了序列号、地址信息、传输类型和其他控制信息。

数据链路层利用序列号对数据包进行排序,确保数据包的顺序,同时它也负责确认和重传机制。该层通过序列号跟踪和管理数据包的传输,如果接收端检测到数据包丢失或错误,它可以请求发送端重发该数据包。

3.2.2 流量控制和错误检测

流量控制机制用于防止接收端缓冲区溢出。每个数据包都会在传输前检查接收端的可用缓冲空间,并等待足够空间可用时才发送。这避免了数据包丢失,并确保了链路的高效使用。

错误检测是数据链路层的另一个重要功能。PCIe使用一个32位的循环冗余校验(CRC)来检测数据包在传输中是否发生了错误。如果数据链路层检测到错误,它将丢弃该数据包并请求重发。

3.3 事务层解析

3.3.1 请求和完成事务的流程

事务层位于数据链路层之上,它定义了如何通过PCIe总线进行请求和完成事务。事务可以分为三种类型:Configuration,I/O,和Memory。其中Memory事务又包括Memory Read和Memory Write两种。

请求事务从一个设备开始,通过发送一个包含请求类型、地址和其他控制信息的请求包到目标设备。目标设备根据请求类型执行相应的操作,并使用完成事务将结果发送回请求设备。完成事务通常包括状态码,指示请求是否成功执行。

3.3.2 事务层包的类型和功能

事务层包(TLPs)是PCIe事务层的传输单元。TLPs包括了:

- 请求事务包(Requester TLPs):例如配置读、I/O读、内存读写请求。

- 完成事务包(Completer TLPs):响应请求事务包的完成消息。

- 消息事务包(Message TLPs):用于发送错误、中断和其他信息。

TLPs的结构包括头部信息和可选的有效载荷。头部信息包含了TLP的类型、长度、地址以及传输控制信息,而有效载荷则包含实际传输的数据。

3.3.2.1 配置事务

配置事务用于配置设备的控制和状态寄存器。这种事务特别适用于系统启动或设备添加到总线上的情况,此时系统需要了解设备的能力和配置需求。

3.3.2.2 I/O事务

I/O事务涉及到与设备I/O端口的交互。当需要从设备读取或向设备写入数据时,就会进行I/O事务。由于I/O地址空间是有限的,因此这类事务的使用比较谨慎。

3.3.2.3 内存事务

内存事务是最常见的一种事务类型,用于读写设备的内存空间。内存事务可以是单周期也可以是多周期,单周期事务只需要一个TLP完成数据传输,而多周期事务需要多个TLP。多周期事务允许设备进行较大的数据传输。

事务层在PCIe架构中发挥着关键作用,它不仅定义了事务的类型和格式,还通过事务ID跟踪事务的顺序和状态。这样可以确保事务的完整性和可靠性,使得PCIe总线可以在各种复杂的应用中稳定运行。

在下一章节中,我们将继续深入探讨PCIe的其他重要方面,包括速度等级、电压和信号规范、拓扑结构、中断和流控制机制,以及PCIe在存储领域的应用等。这些内容将为读者提供对PCIe技术更全面的了解,并揭示其在现代计算环境中的核心地位。

4. PCIe速度等级详述

4.1 速度等级标准

4.1.1 PCIe各个版本的速率介绍

PCI Express(PCIe)是一种高速串行计算机扩展总线标准,它定义了不同版本的速度等级。从最初的PCIe 1.0到现在广泛采用的PCIe 3.0,以及即将普及的PCIe 4.0,每一代都提供了更高的带宽和更低的延迟。各个版本的速率如下:

- PCIe 1.0 :最初版本的PCIe提供单通道2.5 GT/s(千兆传输/秒)的速率,从而达到250 MB/s的带宽。

- PCIe 2.0 :其标准翻倍增加了传输速率,即5 GT/s,相应地,单通道的带宽可达500 MB/s。

- PCIe 3.0 :再次翻倍,达到了8 GT/s的传输速率,单通道带宽提升至1 GB/s。

- PCIe 4.0 :进一步提升至16 GT/s,单通道带宽可达到2 GB/s,几乎是PCIe 3.0的两倍。

以表格形式详细对比各个版本的特性:

| 版本 | 速率(GT/s) | 单通道带宽(MB/s) | 通道数 | |------|---------------|---------------------|--------| | PCIe 1.0 | 2.5 | 250 | 最多16 | | PCIe 2.0 | 5 | 500 | 最多16 | | PCIe 3.0 | 8 | 1000 | 最多16 | | PCIe 4.0 | 16 | 2000 | 最多16 |

4.1.2 速率升级的硬件要求

为了实现PCIe标准的升级,硬件组件(如CPU、主板、接口卡等)必须支持新版本的协议。从PCIe 1.0到PCIe 4.0的升级涉及到硬件设计的多个方面,包括:

- 物理层 :信号传输频率提升需要更高质量的电路设计。

- 协议控制逻辑 :需要更复杂的状态机和协议控制逻辑来处理更高的速率。

- 电源和散热 :高速率可能导致更高的功耗和热量产生,硬件需要更好的电源设计和散热系统。

例如,要实现PCIe 4.0的支持,主板上的PCIe插槽必须使用高速率的信号芯片,并且处理器和芯片组也必须提供相应的支持。此外,设备本身(比如SSD、网卡)也必须设计为兼容新速率。

4.2 性能优化策略

4.2.1 高速通信下的瓶颈分析

随着PCIe版本的升级,总线的带宽得到了极大提升,但也带来了一系列挑战,尤其是在数据通信过程中可能遇到的瓶颈:

- CPU负载 :高带宽的PCIe设备可能会造成CPU数据处理的瓶颈。

- 内存带宽 :高带宽设备可能需要高速的数据交换能力,对系统内存的带宽和延迟提出了更高要求。

- 存储I/O :与高带宽的PCIe设备相连的存储设备可能无法提供足够的数据读写速度。

4.2.2 优化配置以提升性能

为了在使用高速PCIe设备时获得最佳性能,可以采取以下策略:

- CPU亲和性 :将高带宽设备与特定的CPU核心绑定,减少跨核心的通信和调度开销。

- 内存子系统优化 :利用双通道、四通道甚至八通道的内存配置来提供更大的内存带宽。

- 使用高速缓存机制 :利用高速缓存来减少对主内存的直接读写,提高数据处理效率。

- 智能I/O调度 :操作系统级别的I/O调度优化,如使用高性能的文件系统,合理分配和管理I/O资源。

优化配置的代码示例:

# 以下命令用于绑定特定进程到CPU核心,以减少调度开销。

taskset -c <核心编号> <进程ID>

# 使用cpupower工具来调整CPU频率,确保提供足够的计算能力。

cpupower frequency-set --governor performance

# 开启大页面支持,减少内存访问延迟。

echo 1 > /proc/sys/vm/nr_hugepages

通过上述策略的实施,可以大幅提升高速PCIe设备的数据处理性能,减少瓶颈的负面影响。

5. PCIe电压和信号规范

PCI Express (PCIe) 作为高性能的总线标准,其电压和信号规范对确保稳定性和兼容性至关重要。本章将详细介绍PCIe的电源管理、电压需求以及如何保证信号质量。

5.1 电源管理和电压需求

电源管理是确保PCIe设备运行稳定的基础,而电压范围和兼容性则是电源设计中必须考虑的关键因素。

5.1.1 电源设计原则

PCIe设备在设计时,首先要考虑电源设计原则。这包括了对电源质量的要求、电压稳定性、电流供应能力等。例如,对于高速的PCIe设备,电源噪声必须控制在规定范围内,以避免数据传输过程中的错误。为此,工程师通常会在电路设计中加入滤波电容和稳压模块。

// 伪代码:电源管理模块初始化

void power_manager_init() {

// 初始化稳压器模块

voltage_regulator_init();

// 添加滤波电容,减少电源噪声

add_capacitor();

// 设置电源管理策略,如关闭不必要的设备以节省电能

set_power_management_policy();

}

在上述伪代码中,初始化过程包括了稳压器模块的配置、滤波电容的添加和电源管理策略的设置。这样的设计有助于维持电压稳定性并降低设备功耗。

5.1.2 电压范围和兼容性

根据PCIe标准,不同的版本有不同的电压要求。例如,PCIe 3.0标准支持8.0V和12.0V两种输入电压。因此,设计兼容多版本的PCIe设备时,必须确保电源管理模块能够适应不同的输入电压。

| PCIe版本 | 输入电压(V) |

|----------|--------------|

| PCIe 1.x | 3.3V |

| PCIe 2.x | 3.3V |

| PCIe 3.x | 8.0V / 12.0V |

设计时还需要考虑设备的最大功率需求,确保电源系统能提供足够的电流。电源设计不仅需要满足当前设备需求,还要有余量以适应未来可能的升级。

5.2 信号质量控制

信号质量直接关系到PCIe总线的传输效率和数据准确性,因此控制信号质量是至关重要的。

5.2.1 信号完整性的保证方法

为了保证信号完整性,PCIe标准中规定了信号的电气参数。这些参数包括上升时间、下降时间和最小信号摆幅。为了满足这些参数,设计者需要选用合适的传输介质和终端匹配技术。

| 参数 | 规格值 |

|------------------|-----------------|

| 上升时间 | < 20% UI |

| 下降时间 | < 20% UI |

| 最小信号摆幅 | > 800mV (典型值)|

上述表格列出了保证信号完整性的一些关键电气参数。除了硬件设计,信号完整性还与布线长度、传输介质和端接电阻等因素有关。在设计过程中,通过仿真和测试来优化这些参数是十分必要的。

5.2.2 信号失真的影响与对策

信号失真是高速传输中的常见问题,可能会导致数据传输错误。失真的原因有很多,例如串扰、反射和抖动等。为此,设计者必须采取一系列措施来减少这些影响。

graph LR

A[开始传输信号] -->|可能产生失真| B[串扰]

A -->|信号衰减| C[反射]

A -->|随机变化| D[抖动]

B -->|采用差分信号| E[减少相互干扰]

C -->|适当匹配阻抗| F[避免信号反射]

D -->|提高信号同步精度| G[降低随机误差]

在上图中,我们通过mermaid流程图展示了信号失真的可能原因以及解决方法。使用差分信号、适当匹配阻抗和提高信号同步精度都是减少信号失真影响的有效策略。

通过上述各节的分析,我们可以看出PCIe电压和信号规范对于设备性能的重要性。接下来,我们将在下一章节继续深入探讨PCIe的拓扑结构。

6. PCIe拓扑结构说明

6.1 点对点连接方式

PCIe的点对点拓扑结构是其核心特性之一,它允许每个设备拥有专用的数据通道,而不是像传统PCI那样在多个设备间共享总线。这种设计显著提高了数据传输的效率和带宽利用率。

6.1.1 端口和插槽的连接机制

在PCIe中,每个设备通过一个特定的端口连接到系统。端口通常位于主板上的插槽内,可容纳各种PCIe扩展卡。这种连接方式保证了设备之间的独立通信,避免了数据拥堵。

一个PCIe设备端口(也称为下游端口)连接到一个根端口(位于CPU或芯片组内),形成点对点的连接。这种连接提供了专用的上行和下行数据路径,支持全双工操作。这允许数据在任何给定时间以双向流动,最大化带宽利用率。

6.1.2 独立和共享带宽的差异

在点对点的连接方式中,每个设备连接都有独立的带宽。这意味着每个设备都有专属于它的链接,避免了在多个设备间共享带宽导致的性能下降。相比之下,共享带宽的设备必须在访问总线时竞争,这会导致延迟增加和带宽利用不充分。

6.2 多端口扩展应用

多端口扩展应用允许在单个系统中增加更多的PCIe设备,扩展系统功能并提供更大的灵活性。

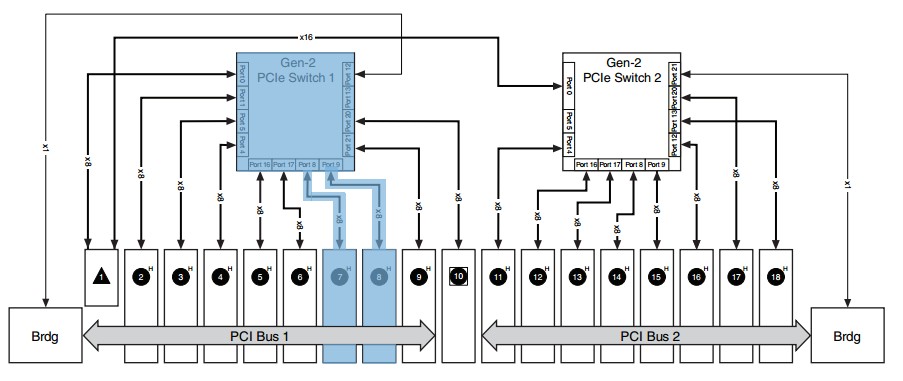

6.2.1 多级交换结构的设计

在多端口扩展中,交换结构用于管理多个PCIe端口间的通信。交换结构可以是多个独立交换器组成,也可以是一个集成到系统中(如集成在主板上的)的多端口交换器。

为了设计一个有效的多级交换结构,设计者需要考虑如何有效地路由请求和数据包,以减少延迟并优化带宽使用。这通常涉及到复杂的数据包调度算法,以及对多个端口间的仲裁和流控制逻辑的设计。

6.2.2 扩展系统的兼容性和性能

扩展PCIe系统时,兼容性是一个重要的考虑因素。设计者需要确保所有设备和扩展卡都遵循相同的PCIe标准,以保证互操作性。性能考量包括扩展卡对总线带宽的需求,以及它们如何在系统内有效共享带宽。

此外,扩展系统时还必须考虑供电和冷却要求,因为更多的设备和扩展卡可能会导致功耗和发热量增加。

在本章节中,我们详细探讨了PCIe的拓扑结构,包括点对点连接方式以及多端口扩展应用的设计和实现。这种结构对于理解和优化PCIe系统设计至关重要,尤其在高速数据传输和大型系统集成中显得尤为重要。在后续章节中,我们还将进一步探讨PCIe的技术细节和高级应用。

简介:PCI Express(PCIe)是高速计算机设备间通信的关键接口标准,用于显卡、网卡和硬盘等。作为现代计算平台的核心部分,它提供远超传统PCI总线的带宽和更低延迟。本文详细解读了PCIe体系结构的基础、分层结构、速度等级、电压和信号规范、拓扑结构、中断和流控制、热插拔和功率管理,以及存储应用和未来发展。深入理解PCIe对于计算机系统设计和性能优化至关重要。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?