notice : 这篇文章仅仅具有上机实验的参考作用,并且需要配套的文件

Logisim学习

隧道

相当于局部变量

复用器-Bit-Selector

把(West edge)输入数据从最低位开始,平均分成n组,n由输出位宽决定;

另一个输入(South egde)决定选择第i组数据

用到的组件总结

Wiring→Bit Extender,Constant,Tunnel,Probe

Gates→…

Plexers→Multiplexer,Decoder,Bit Selector

Arithmetic→Adder/Substractor*,Multiplier,Divider,Comparator,Shifter

Anchor

构建 32 位运算器。利用封装好的 32 位加法器以及 logisim 平台中现有运算部件(禁用系统自带的加法器,减法器)构建一个32 位运算器,可支持算术加、减、乘、除,逻辑与、或、非、异或运算、逻辑左移、逻辑右移,算术右移运算,支持常用程序状态标志(有符号溢出OF、无符号溢出 CF,结果相等 Equal),运算器功能以及输入输出引脚见下表,在主电路中详细测试自己封装的运算器,在报告中分析该运算器的优缺点。

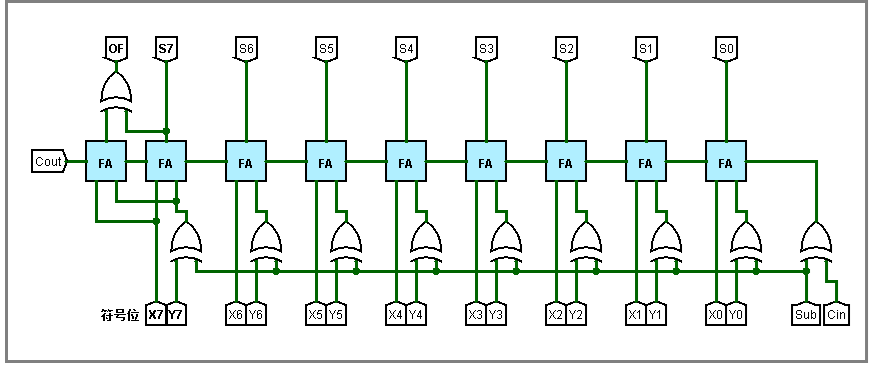

8位串行可控加法器

见课本P69,不同之处就是这里有cin

eg. X + Y

Sub=0时,Cin 就是进位

Sub=1时

,Cin=0 时, Sub xor Cin = 1,表示对Y的补码运算

,Cin=1 时,Sub xor Cin = 0,Cin表示借位,因此Y-1,与补码的+1抵消

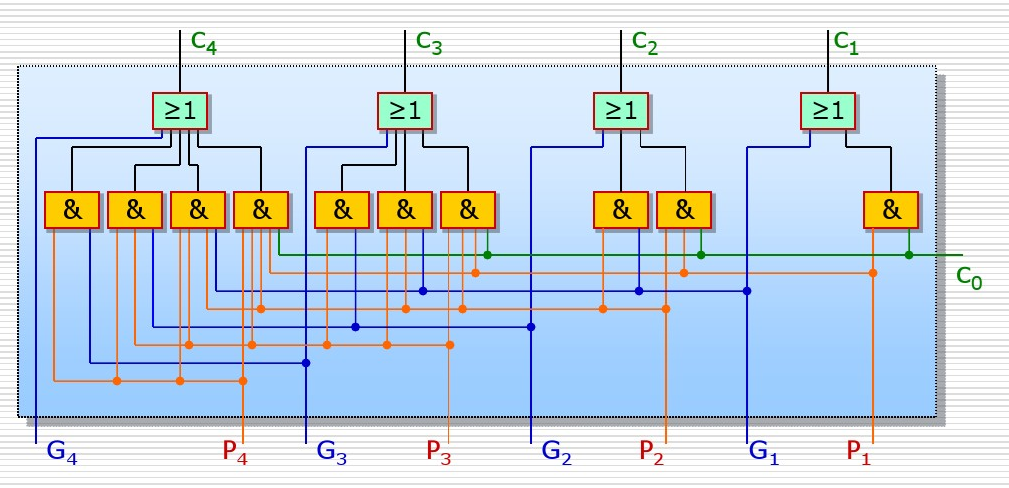

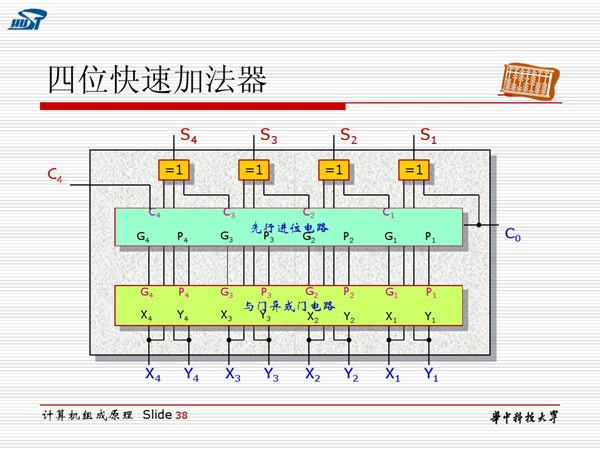

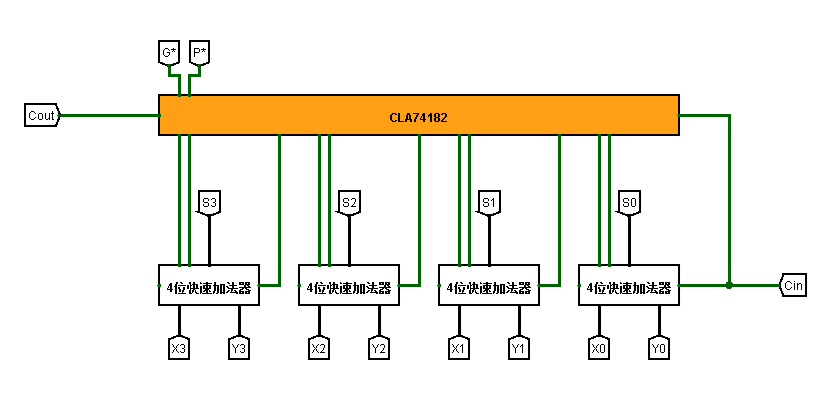

CLA74182先行进位电路

串行进位加法器一级一级的进位延迟大,

所以可以想办法提前得到当前位的进位输入

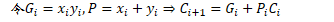

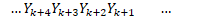

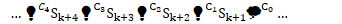

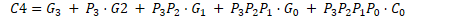

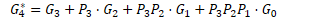

以4位为例,设二进制加法器第i位输入为xi,yi,输出为si,进位输入是ci,进位输出Ci+1

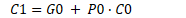

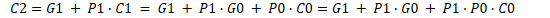

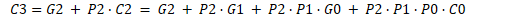

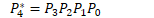

递归的展开有

这里可以发现各级的进位与其他进位无关

G*,P*再按 "文件" 所给提示连接即可

G*,P*作用

到下面会提到

CLA..作用

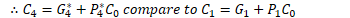

部分1:由以上产生的Gi,Pi,输入到CLA,G*,P*

部分2:由Gi,Pi,C0能产快速生各个位的进位

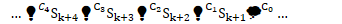

4位快速加法器

这个比较简单,如果画好了CLA74182,G*,P*作用仍不明

notice

上面GP index从1开始

作用

输入Xi,Yi,C0

由以上产生Gi,Pi,输入到CLA,能产快速生各个位的进位和

得到Si,Ci,G*,P*

| 输出(需要的)(高亮最后的输出) | 各结果的产生次序 |

| Xi,Yi,C0 | 0 |

| Gi,Pi(Xi,Yi) | 1 |

| G*P*(Gi,Pi),Ci(Gi,Pi,C0) | 2 |

| Si(Ci,Xi,Yi) | 3 |

notice

这里用了隧道G1,G2,…

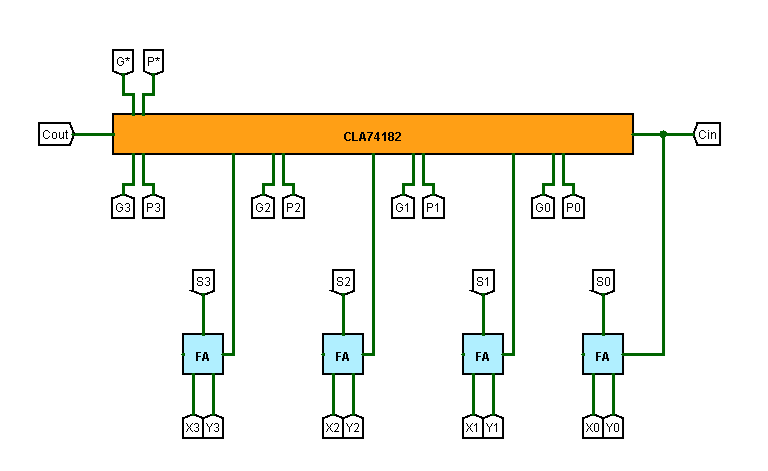

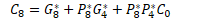

16位快速加法器

成组进位

而只把xi,yi丢向4位快速加法器,就能得到G*,P*,输入CLA74182,得到各个进位,再输回4位快速加法器,得到Si

| 输出(需要的)(高亮最后的输出) | 各结果的产生次序 |

| Xi,Yi,C0 | 0 |

| Gi*,Pi* | 1 |

| Ci(Gi*,Pi*,C0),GAll*,PAll* | 2 |

| Si(Ci,Xi,Yi) | 3 |

32位快速加法器

同16位加法器,只不过多了个溢出检测↓

_溢出检测

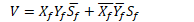

第一种

相加两数X,Y符号相同,且与结果S的符号不同

第二种

最高数据位的进位与符号位的进位是否一致,不一致表示溢出

例如 -111+(-110

补码是1001 + 1010

所以溢出了

这里用第一种溢出检测即可;可以用复用器-Bit-Selector分离出符号位(比Splitter简单)

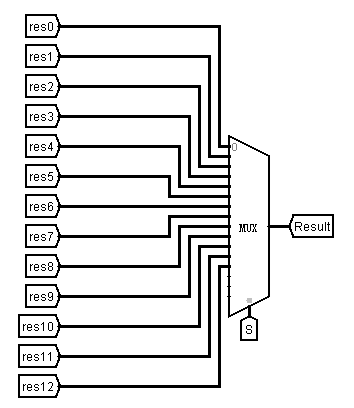

ALU

equal&&op=1011

logisim运算器→比较器

Signed OverFlow

只需要处理有符号加减的

Unsigned Overflow

加法和小于加数,减法差大于被减数

特别的:加法:无符号加法,溢出即是进位,32位加法器的一个输出cout就是此变量

alu operation

logisim→复用器→数据选择器multiplexer

| 0 | 自带移位器 |

| 1 | 自带移位器 |

| 2 | 自带移位器 |

| 3 | 自带乘法器 |

| 4 | 自带除法器 |

| 5 | 32位加法器 |

| 6 | 32位加法器 |

| 7 | 自带逻辑门 |

| 8 | 自带逻辑门 |

| 9 | 自带逻辑门 |

| 10 | 自带逻辑门 |

| 11 | √ |

具体电路不再给出

其他

^运算器测试电路

把☆ALU 从左侧的栏目中拖到运算器测试电路上,完成运算器测试电路

2235

2235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?