实例化FFT(vivado) 以及matlab和fpga的fft结果对比

实例化FFT(vivado) 以及matlab和fpga的fft结果对比

前言

我是fpga小白,在vivado软件上实例化fft单元的时候,走了不少弯路;记录下来,能加深记忆,也希望能够帮助向我一样的小白,快速上手fft。

一、FFT

fft就是快速傅里叶变换,具体理论,课堂上课本上博客上都有,不赘述了。在这里我将使用vivado软件实例化一个长度为64的快速傅里叶变换IP核,并将运算结果和matlab中的运算结果相比较。

二、使用步骤

新建工程没啥好说的,如果有开发板,那就按照对应的型号芯片来创建,然后点击一万个next一万个finish就好了。

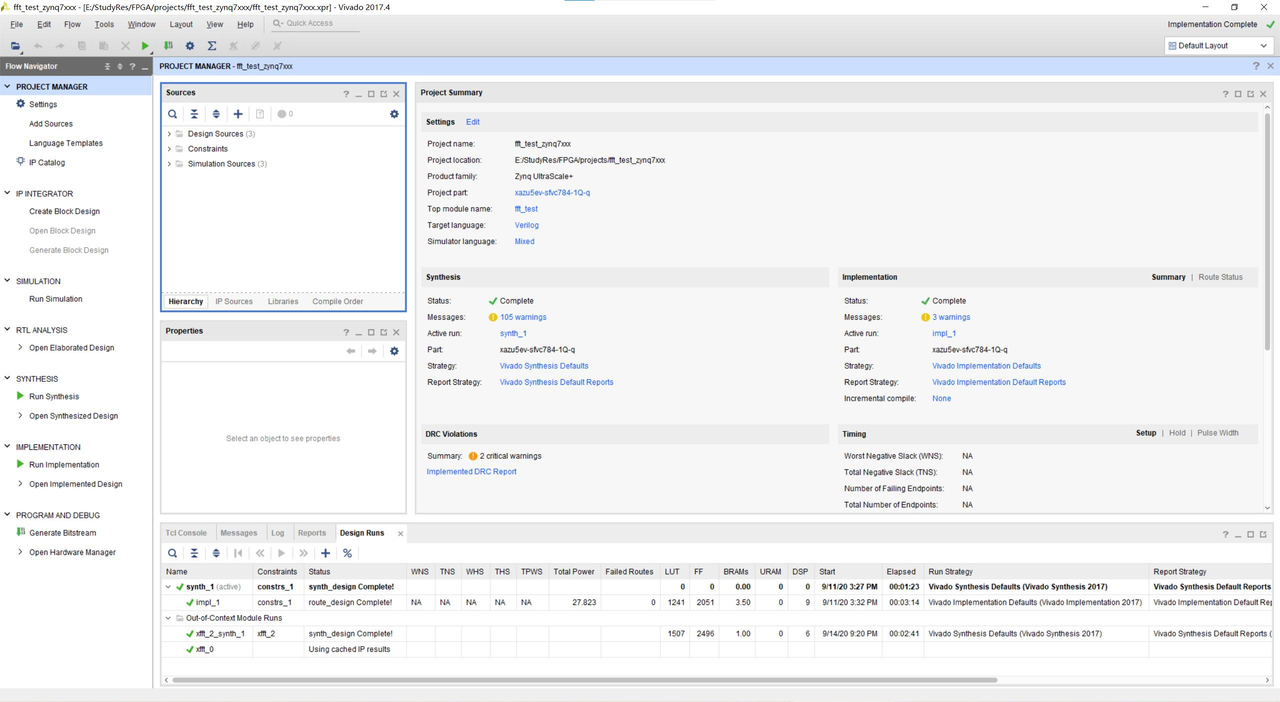

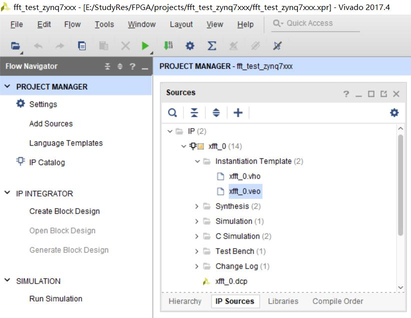

下面是我建立好的工程:

截图的时候我的相关文件代码都搞好了,所以design sources后面的()里面是3,新建的应该都是零。

2.1 按照途中顺序操作:

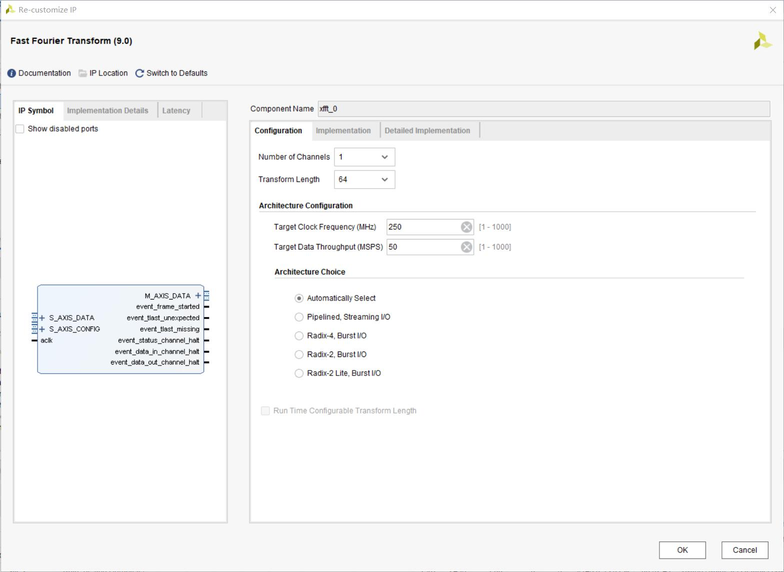

2.2 configuration

双击完了axi4-stream的那个fft就弹出来了配置页面

图中最关键的就是Transform Length,就是fft的点数,我设置的是64;Number of Channel应该指的是例化fft的个数,如果是1,就是一个64位的fft单元,如果是2,就是有两个64位的单元,组成了两个通道,这样就避免了重复配置。

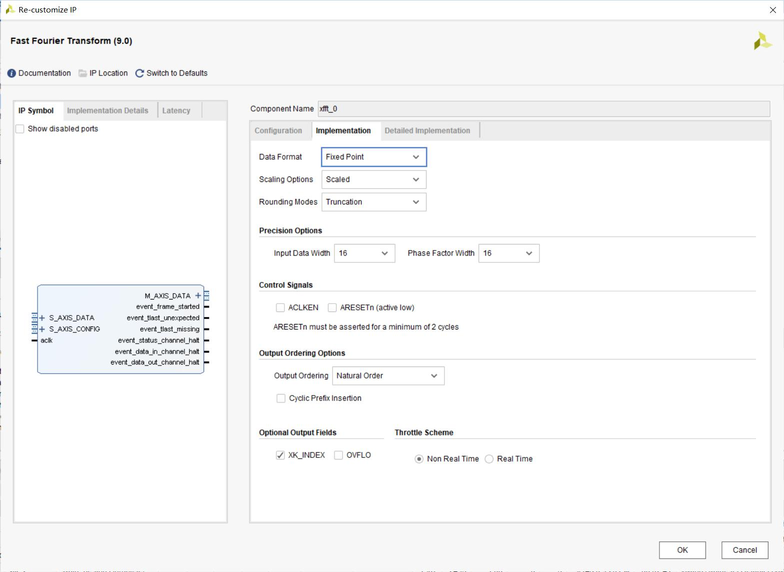

2.3 implementation

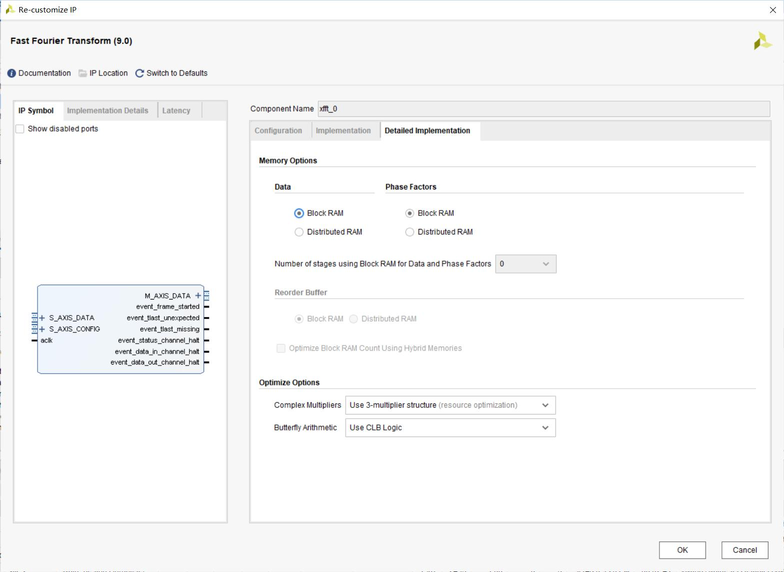

下面是implementation子目录截图:

数据格式,定点,初次学习,定点方便理解;浮点数比较复杂,可以单独去学习;剩下的就按照图中配置,记得给xk_index打上钩,这个是fft结果的索引,换个说法,如果fft结果是个数据流,那打了对勾,这个数数据流就自带下标。

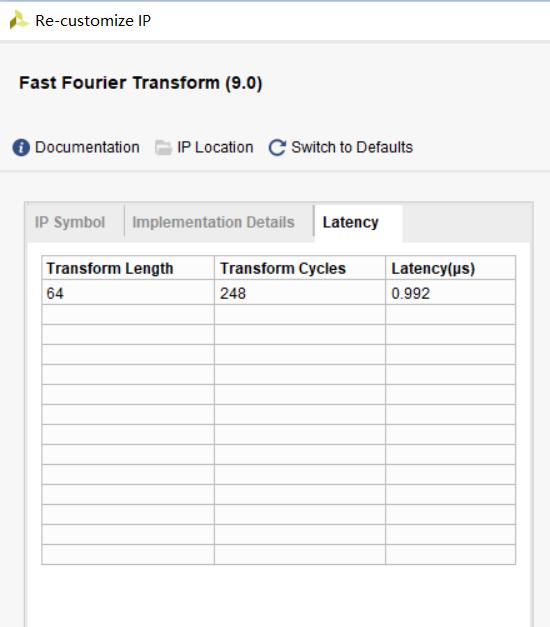

剩下的也是如图配置;在latency标签下面可以看到最终的延迟:

点击ok生成等待,ip核就可以用了,怎么用,下面讲。

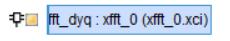

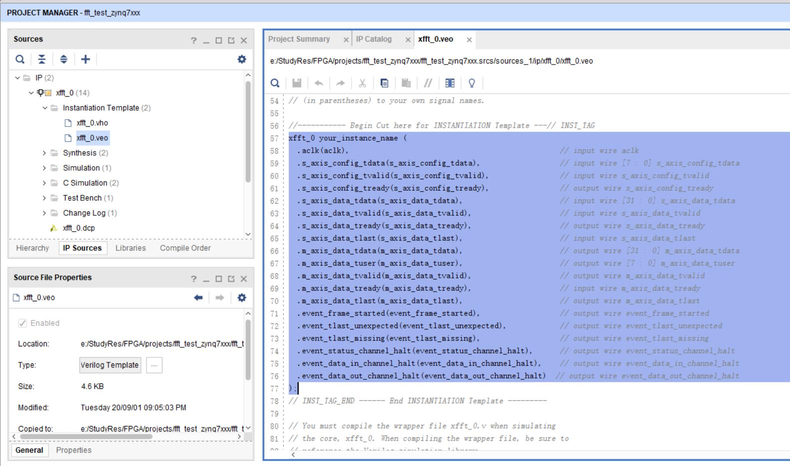

vivado软件很人性化,会自动生成ip核的调用方式的模板,位置如图所示:

双击.veo也就是Verilog版本的例化模板可以看到这些东西:

把选中的部分复制下来;开始写top文件,也就是驱动这个ip

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

324

324

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?