本章首先从指令形式和每周期可执行指令数两方面叙述处理器的分类方式,然后对超标量处理器诞生的原因以及与普通处理器的差异进行分析,最后对普通处理器、顺序执行和乱序执行的超标量处理器流水线进行介绍。

1.1. 处理器的分类方式介绍

主要依据指令形式和每周期可执行指令数进行分类。

CISC:最开始使用的指令形式,一条指令完成很多事情,尽可能创造更多的指令覆盖各种操作,以降低对存储器的需求,简化编译器设计。

RISC:软件模拟80%的非常用CISC指令以简化硬件设计,等长易于解码,方便流水线设计,提高频率,降低功耗和成本。

超标量处理器:一周期执行多条指令,因此指令的源操作数都准备好即可执行,称之为乱序执行,但不可改变程序原有功能,需要一些方法使得乱序执行的指令看起来仍按程序制定的顺序更改处理器状态。相比标量处理器,性能有很大提升,但需要更多的硬件资源和更大的功耗。

通用处理器由此可被分为:

Scalar CISC:处理器最开始结构,可能无法使用流水线,如Intel的8086、80286等处理器,已被淘汰。

Scalar RISC:RISC处理器的早期结构,使用流水线提高性能,主频高,成本低,如MIPS R2000及3000、Alpha21064和ARM7等,现在在嵌入式低功耗领域仍在使用,如MIPS 4K系列处理器、ARM的Cortex M和Cortex R系列。

Super scalar RISC:由于RISC指令集规整便于硬件实现且早期RISC处理器多面向服务器市场,故该类处理器率先采用单周期执行多条指令,早期有MIPS R1000、Alpha 21264和Power PC 620等处理器,现在嵌入式高性能领域有MIPS 74K系列、ARM Cortex A9和A15处理器。该类处理器为本专栏主要关注的处理器。

Super scalar CISC:Inter和AMD在处理器内部使用硬件将一条CISC转化为多条RISC解决流水化问题使得处理器可以单周期执行多条CISC指令。比普通的RISC处理器需要更多硬件资源,功耗更大,如当代Intel全系列处理器,Pentium4、Pentium M、Core和Core 2等处理器。

专用领域处理器还有其他架构和指令集,如VLIW,很难保证程序兼容性,特定领域可获得比通用处理器更好的性能。

1.2. 为什么需要超标量

程序执行时间=总指令数(程序大小、算法、编译器、ISA扩展、码农水平)X CPI(每指令所需cycle数,取决于具体的处理器即微架构)X 时钟周期(工艺)

ISA扩展:扩展特殊指令以减少数量如X86的多媒体指令。

硅农能做的:减小CPI,普通标量处理器使用流水线最多减小到1,故还需要超标量处理器。

硅农还能做的:通过精巧的电路设计和更深流水线提升时钟频率。此外EDA工具和工艺均对时钟频率有较大影响。

注意CPI与时钟周期相互约束,处理不好会造成高频低能即提高时钟频率,执行效率反而下降,如Intel Pentium 4系列。

超标量处理器:硬件决定哪些指令并行,码农可抛开底层硬件实现细节,为通用处理器采用。

超长指令字VLIW:编译器和码农决定哪些指令并行,硬件简单,可在专用处理器如DSP中使用。

总结:减少程序执行时间——提高IPC——超标量or VLIW——超标量。

几个tradeoff:

精确分支预测算法——复杂硬件——无法在一个cycle内完成预测——无法利用预测信息连续取指——性能下降;

乱序执行load/store——相关性检查及恢复机制复杂——硬件复杂且功耗增加;

Checkpoint个数与硬件面积;

发射队列个数与仲裁电路复杂度;

每cycle执行个数和寄存器堆端口。

本专栏将根据处理器应用领域和场合给出折中思路。

1.3. 普通处理器流水线

通过流水线降低周期时间提高执行频率。假设处理器频率决定性能:Performance = 1/(D/n + S),D为未使用流水线的周期时间,n为流水线级数,S为寄存器延迟。硬件面积:Cost = G + n X L,G为未使用流水线需要消耗的处理器硬件面积,L为寄存器及附带控制逻辑所消耗面积。Cost/Performance = GD/n + nSL + LD + GS(为n的勾勾函数),G、D、L、S一定时可选择合适的流水线级数n。nop=(GD/LS)0.5,但GD很难估计,且除频率外分支预测准确度、load/store指令的处理方式等均会影响性能,且有的应用着重考虑性能,有的应用着重考虑面积,因此需要根据实际需求决定流水线级数。

流水线的划分需注意:

最长流水段时间决定周期时间;

每个流水段操作一样但不同指令需要的操作也是不同的;

指令相关性影响流水线执行效率。

经典五级流水线:

Fetch,从I-cache中取指存在指令寄存器中;

Decode & Regfile read, 解码指令,根据解码值从寄存器堆读出源操作数;

Execute, 根据指令类型完成计算任务,如算数运算、地址运算等;

Memory, 访问D-Cache,除load/store指令外其他指令在该阶段不做任何事;

Write back, 将存在目的寄存器的指令结果写入目的寄存器。

若各流水段时间不均衡(如五级分别用时7 ns, 11 ns, 5 ns, 10 ns, 3 ns),可采取合并的方式(Fetch+ Decode/ Regfile read+ Execute/ Memory+ Write back),如低功耗嵌入式处理器ARM7、ARM9以及Cortex-M0、M3等均采用这种方式减少流水线级数。高性能处理器采取拆分方式以获得更快的时钟频率但流水级数会增加,控制逻辑、寄存器堆端口数、Mis-prediction penalty、Cache端口数、功耗均会增加,失败例子如Intel pentium4,较成功例子如MIPS R3000 (Fetch+ Decode/ Regfile read/ Execute/ Memory/ Write back)和 AMD AHL470V/7 (IF: PC GEN+2*ICache Read / ID/ 读取操作数OF:Read REG+Add GEN+2*DCache Read/ EX1+EX2/ 保存结果OS:Check Result +Write Result)。

同时处于流水线中(不一定相邻)指令间的相关性:

1) 先写后读RAW,如:

指令A:R1=R2+R3

指令B:R5=R1+R4

必须等待A将结果计算出来B才可执行,RAW相关性无法回避。

2) 先读后写WAR

指令A:R1=R2+R3

指令B:R2=R5+R4

A读R2之前B不可把结果写入R2,可将B结果写入其他寄存器(物理寄存器)以避免WAR相关性。

3) 先写后写WAW

指令A:R1=R2+R3

指令B:R1=R5+R4

A把结果写入R1前,B不可把结果写入R1,可将B结果写入其他寄存器(物理寄存器)以避免WAW相关性。

4) 控制相关性

由分支指令引起,只有分支指令结果被计算出时才知道下一条指令的pc,在此之前通过预测的方式取指。

RAW、WAR、WAW不仅适用于寄存器地址也适用于存储器地址,但存储器地址间的相关性很难看出。如:

sw R1, 0(R2)

lw R3, 0(R4)

当R2中值等于R4中时,即存在RAW相关性,这种相关性非常隐蔽,需要将load/store指令所携带地址计算出来才可判别。对于标量处理器,WAR和WAW均不存在,RAW通过旁路(bypass)的方式解决,对于超标量处理器所有相关性均会影响指令乱序执行,均需特殊处理,后文会逐一详细介绍。

1.4. 超标量处理器流水线

单周期取出多条指令执行且用硬件对指令进行调度的处理器即为超标量处理器,分为顺序执行和乱序执行两种,注意乱序执行在取指译码(乱序很难且无意义)以及提交(即指令被允许修改处理器状态如D-Cache,顺序以保证程序顺序且实现精确异常)时也是顺序执行。只要操作数准备好即可将指令乱序发射进FU中乱序执行,通过寄存器重命名将ARF动态转化为PRF实现乱序写回。

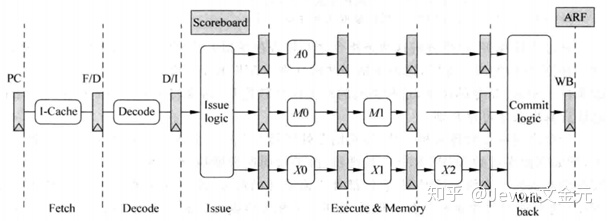

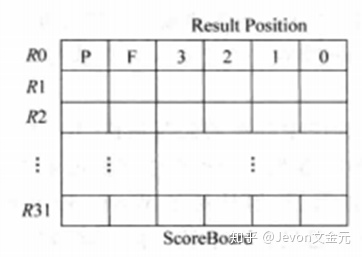

首先叙述顺序执行的超标量处理器,如图1,为保证WB阶段顺序执行,3个FU(分别负责ALU、存储器类型、乘法三种指令的运算)需经历同样周期数流水线。ScoreB oard用于记录每条指令的执行情况,如图2,记录了每个ARF(R0-R31)的执行情况,包括:

P:Pending,表示指令结果尚未写入ARF;

F:表示指令在哪个FU中执行,结果旁路时需要该信息;

Result Position:指令到FU中哪个阶段,3表示第一流水段,1表示最后流水段,0表示写回,发射阶段会将指令信息写入ScoreBoard。

同时该指令查询ScoreBoard源操作数是否准备好,FU每经过一个周期,Result Position被右移一位。更复杂的处理器,计分板会有其他内容。

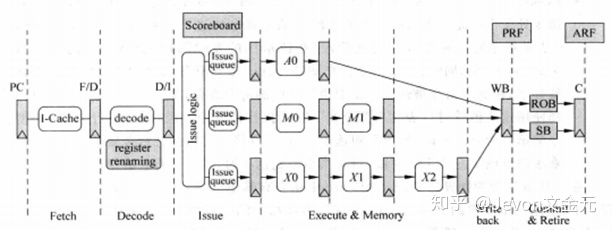

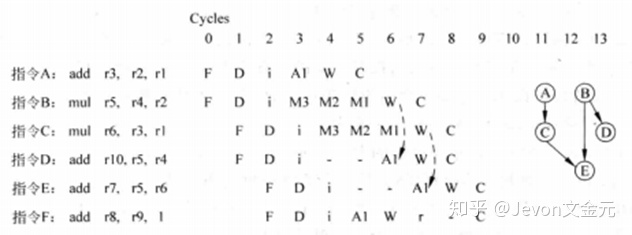

再看乱序执行的超标量处理器,如图3,为解决WAW和WAR相关性,译码器阶段重命名寄存器将ARF映射到数量更多的PRF。发射阶段指令被存入发射队列,源操作数准备好即被发射到对应FU中执行,而后乱序写回PRF,而由于分支预测失败或异常,PRF结果可能不会全部写入APF,故PRF也被称为future file。而后再通过重排序缓存ROB将结果从PRF顺序提交至ARF,不处于分支预测失败或异常路径则顺利退休。值得注意的是指令在退休之前都可能被清除,而store指令在写回阶段就可能被写回存储器,所以需要store buffer(SB),因此load指令也需要在D-cache和SB中同时寻找数据。图4为程序乱序执行过程,r表示计算完成。

本专栏会逐一详细叙述超标量处理器的各个流水段,在这里先粗略介绍。

1)取指(fetch):主要有两步,先由分支预测器决定下一条指令的PC,再从I-cache中取指;

2)译码(decode):识别指令类型、操作数及控制信号,RISC简单,CISC复杂;

3)寄存器重命名:寄存器重命名使得处理器可调度更多指令并行执行,通过表格存储ARF和PRF的映射关系、未使用的PRF等信息,分析并标记RAW相关性的指令,一般会把该步骤单独放一流水段;

4)分发(dispatch):被重命名后的指令顺序写入发射队列、ROB和SB中,如果没有空间则需要在重命名阶段等待,分发可和重命名放一个流水段,也可分开;

5)发射(issue):仲裁(select)电路从发射队列中选择准备好的最合适的指令送进FU执行,发射队列中还存在唤醒电路,将队列中对应的源操作数置为有效,仲裁电路和唤醒电路配合工作,是处理器中的关键路径;

6)读取寄存器:被仲裁电路选中的指令从PRF或旁路网络中得到操作数,旁路网络的存在使得减少PRF读端口成为可能,多端口寄存器堆访问速度慢,需要单独使用一个流水段;

7)执行(execute):得到操作数后送入对应FU中执行,一般包括负责普通运算、乘累加运算、分支指令运算、load/store指令运算等FU,现代处理器还会加入负责多媒体运算如进行单指令多数据(SIMD)运算的FU;

8)写回:将计算结果写入PRF,还需要通过旁路网络送出,该网络布线非常重要直接影响速度,一般使用cluster结构将FU分组,同组FU紧挨,可在一个周期送出,跨组则需更多周期;

9)提交(commit):ROB顺序将结果写入ARF,同时处理异常,所有异常均需到达该阶段后再进行处理以实现精确异常,指令从ROB离开后无法再修改处理器状态。

还需注意的是,预测失败后不仅需要清除错误指令,还需清除其造成的痕迹,如修改的重命名映射表、已写入结果的PRF,处理异常时也需要清除流水线中的指令及痕迹以恢复处理器状态。

注:本专栏所有内容均来自于本人对《超标量处理器设计》这本书学习笔记的总结整理与思考,专业术语的英文全称及解释均只在第一次出现时说明,后文不再说明,可读性较差,但适合从事CPU设计工作的专业人员逐字逐句精读,不喜请自行离开,没必要瞎喷。

4909

4909

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?