1、何为数字系统?

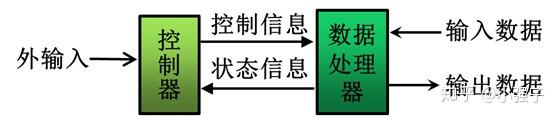

采用数字电子技术实现数字信息处理、传输与控制的数字逻辑单元集合称为数字系统。数字系统一般包括数据处理器和控制器两个部分。

数据处理器:由寄存器和组合电路组成。寄存器用于暂存信息,组合电路实现对数据的加工和处理。

控制器:决定数据处理器的操作和操作序列。控制器决定操作步骤,可以记忆当前步骤,也可以确定下一步骤,因此控制器中包含存储器,用来记忆操作步骤,及时根据外部输入和数据处理器的状态信息来确定下一个操作步骤。

大部分数字系统都可以划分为数据模块和控制模块。数据模块完成数据处理,产生系统的输出信号、数据运算状态等信息。控制模块实际上就是一个状态机,它接收输入信号以及数据模块产生的数据信息,经状态机控制后产生控制信号,因而状态机的性能好坏对整个系统的性能有很大影响。

2、何为有限状态机?

有限状态机(Finite State Machine,FSM),顾名思义,就是一系列数量有限的状态组成的循环机制。它是由寄存器和组合逻辑构成的硬件时序电路。状态机通过控制各个状态的跳转来控制流程,使得整个代码看上去更加清晰易懂,在控制复杂流程的时候,状态机优势明显,因此基本上都会用到状态机,如SDRAM控制器等。FSM设计技术是实现数字逻辑设计的重要组成部分,是实现高效率、高可靠性控制逻辑的重要途径。通过状态转移图设计手段可以将复杂的控制时序图形化表示,分解为状态之间的转换关系,将问题简化。

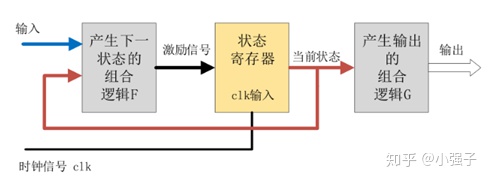

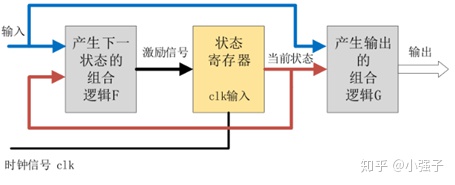

根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore)型状态机和米勒(Mealy)型状态机。

(1)Moore状态机:组合逻辑的输出只取决于当前状态。Moore机属于异步输出状态机,它的输出仅为当前状态的函数,与当前输入信号状态无关。

(2)Mealy状态机:组合逻辑的输出不仅取决于当前状态,还取决于输入状态。Mealy机属于同步输出状态机,它的输出是当前状态和所有输入的函数,其输出会在输入变化后立即发生,不依赖于时钟的同步。

3、设计FSM的基本步骤?

(1)画出状态转移图

把实际系统进行逻辑抽象,即实际问题转化为设计要求。首先确定电路输入输出引脚;然后根据实际需要列出所有的状态情况,并对状态顺序进行编号;最后根据状态转移条件画出状态转移图。

(2)确定状态编码和编码方式

编码方式的选择对所设计的电路复杂与否起着重要作用,要根据状态数目确定状态编码和编码方式。

(3)给出状态方程和输出方程

列写状态转移表,选定触发器类型,通过卡诺图化简给出状态方程和输出方程。(此步在FPGA编程中可省略)

(4)编写Verilog代码

按照步骤(1)~(2)编写具有可综合的Verilog代码。

4、何为编码方式?

用Verilog HDL设计实现有限状态机的关键是状态编码,状态机的状态编码规则对设计实现的状态机性能具有很大影响。常用的编码方式有三种:

(1)顺序码:也称二进制编码,就是使用二进制数来表示状态 ,这是一个简单而常用的状态编码方式。

(2)枚举类型状态编码:根据所需要的状态,定义新的枚举类型,并使用枚举类型定义状态变量。

(3)独热码:也称一位有效编码,就是使每个状态占用状态寄存器的一位。

枚举类型状态编码与顺序编码基本相同,所不同的是书写格式不同,用枚举变量来表示状态具有更好的可读性,多用于小型数字系统设计。使用独热码看起来好像很浪费资源,但这种编码方法可以简化各组合逻辑电路之间的内部连接,产生较小的且更快的有限状态机。这对于时序逻辑资源比组合逻辑资源更丰富的可编程逻辑器件来说 , 是比较有效的编码方式。所以强烈推荐独热码。

5、三段式状态机?

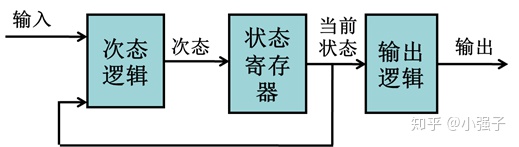

根据状态机的实际写法,状态机还可以分为一段式、二段式和三段式状态机。最常用的是三段式状态机,在此介绍三段式状态机。

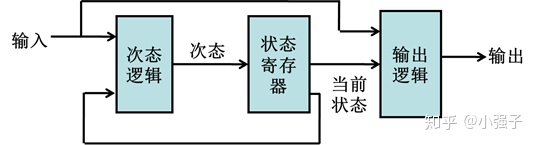

三段式状态机使用三个always模块:一个always模块采用同步时序描述状态转移(使用状态寄存器);另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律(次态逻辑);最后一个always模块描述状态输出,可以是组合电路输出,也可以是时序电路输出(输出逻辑)。

为了避免不必要的锁存器生成,需要穷举所有状态对应的输出动作,或者使用 default 来定义未定义状态动作;在定义状态时,推荐使用本地化参数定义 localparam(或parameter),这样可以在编写时状态更清晰且不容易出错,也方便修改;在复位或者跑飞能回到初始态或者预定态;要有异步或者同步复位来确保状态机上电有个初始态。

6、三段式状态机代码八股文?

(1)Moore型状态机

//Moore型状态机的Verilog HDL一般结构:

(2)Moore型状态机

//Mealy型状态机的Verilog HDL一般结构:

『文末说明』

本文作者:小强子

知乎ID:Power小强

永远年轻,永远热泪盈眶,永远充满希望,一个嗜好太多能力又太小的普通人。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?