以全加器为例(个人经验,大家可以借鉴一下!!!)

记得关注,转发 ,收藏,评论!!!!

记得关注,转发 ,收藏,评论!!!!

记得关注,转发 ,收藏,评论!!!!

实验器材

1、 SOPC实验箱

2、 计算机(装有Quartus II 7.0软件)点击

实验原理

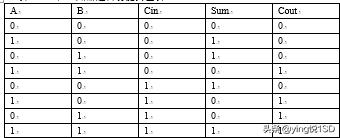

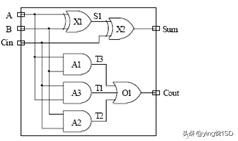

1、1位全家器能实现2个二进制数含进位位的加法,其逻辑功能真值表如表-1,电路原理图如图1.0所示

表-1 1 位全加器逻辑功能真值表

表-1 1 位全加器逻辑功能真值表

图1.0 1 位全加器电路

图1.0 1 位全加器电路

实验内容

设计一个全加器,实现全家器的逻辑功能。其输入由三位拨码开关提供,输出由五路LED指示,其中两路显示输出结果,另外三路显示输入拨码开关的状态。

注意:实验箱上的LED指示灯,低电位时亮,高电位时灭,注意电路最后的输出逻辑转换。

一、使用QUARTUS II建立工程

1、打开QUARTUS II软件并建立工程

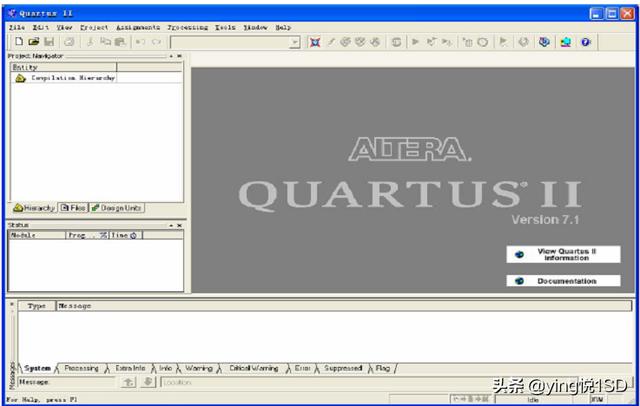

选择 开始>>程序>>Quartus II 7.0>> Quartus II 7.0(32-Bit)打开Quartus II 7.0软件。也可以直接点击桌面上的Quartus II 7.0(32-Bit)图标打开Quartus II 7.0,软件界面如图1.1所示。

图1.1 Quartus II界面

图1.1 Quartus II界面

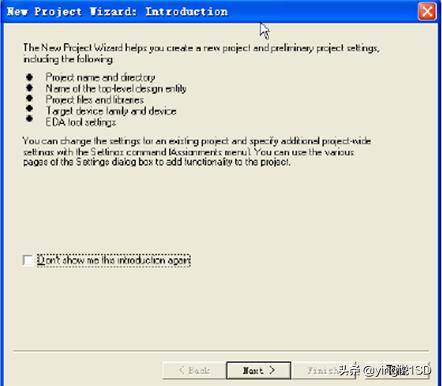

2、在图1.1中选择 File>>New Project Wizard来新建一项工程。在本实验指导书中,任何一个实验都是包含于一个项目中。同时要区别"New Project Wizard"与"New"的关系,"New"是新建项目内的子文件用。

图1.2 新建工程向导说明对话框

图1.2 新建工程向导说明对话框

3、弹出如图1.2所示新建工程向导说明对话框,从中可以了解我们要完成任务,其中包括:

a.指定项目目录,名称和顶层实体。

b.指定项目设计文件。

c.指定该设计的Altera器件系列。

d.指定用于该项目的其他EDA工具。

e.项目信息报告。

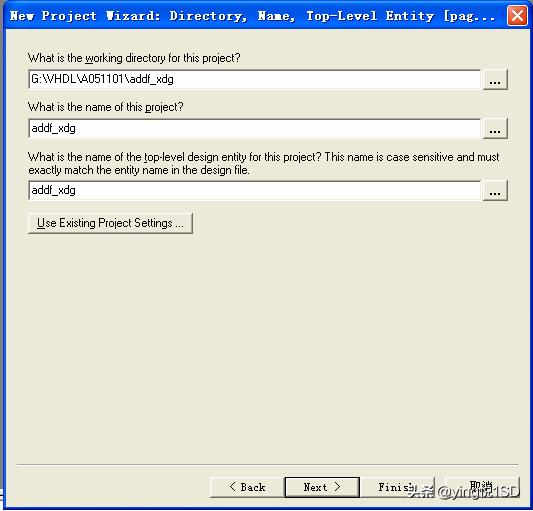

1)在图1.2中单击Next进入图1.3所示的新建工程路径、名称、顶层实体对话框。任何一项设计都是一项工程,必须首先为此工程建立一个放置此工程相关的所有文件的文件夹,此文件夹放置所有与此工程相关的文件,为默认的设计工作库。

一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。实验过程中,我们统一要求,大家在计算机的最后一个盘内,存放自己的设计。如电子A0511班1号,则在计算机的最后一个盘内新建一个文件夹:E:VHDLA051101addf_xdg中(xdg为姓名首字母),本实验存放在E:VHDLA051101addf_xdg。同时注意,存放目录中最好不要出现中文。

图1.3 新建工程路径、名称、顶层实体对话框

图1.3 新建工程路径、名称、顶层实体对话框

在图1.3中,第一栏用于指定工程所在的工作库文件夹;第二栏用于指定工程名,也可以直接用顶层文件的实体名作为工程名(建议使用);第三栏用于指定顶层文件实体名。

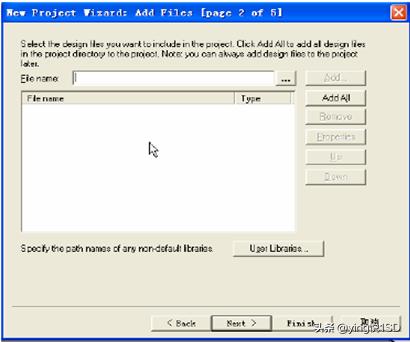

2)在图1.3中单击Next进入图1.4所示的添加文件对话框。本设计为新建项目,暂时不添加文件,直接进入下一步。

图1.4 添加文件对话框

图1.4 添加文件对话框

3)在图1.4中单击Next进入图1.5所示指定目标器件对话框。在此我们选择的是PowerSOPC-2C35核心板上的Cyclone II系列的FPGA EP2C35F672C8。我们可以利用右边的过滤器栏(Filters)快速选择。

图1.5 指定目标器件对话框

图1.5 指定目标器件对话框

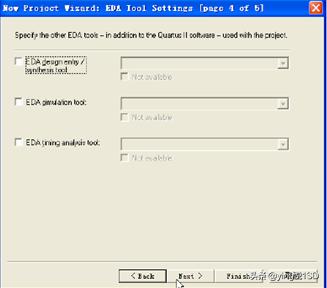

4)选定以后,在图1.5中单击Next进入图1.6所示的指定EDA工具对话框。本实验只使用Quartus II的集成环境进行开发,不使用第三方EDA工具,所以不需要修改,直接点"Next"。

图1.6 指定EDA工具对话框

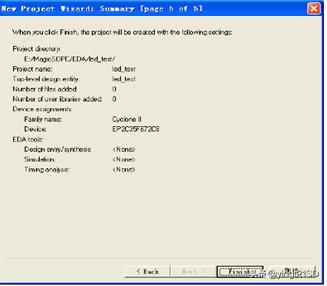

图1.7 工程信息报告对话框

图1.6 指定EDA工具对话框 图1.7 工程信息报告对话框

5)在图1.6中单击Next进入图1.7工程信息报告对话框。可以看到工程配置信息报告。单击Finish,完成新建工程的建立。

4、 建立图形设计文件,即顶层实体设计文件。

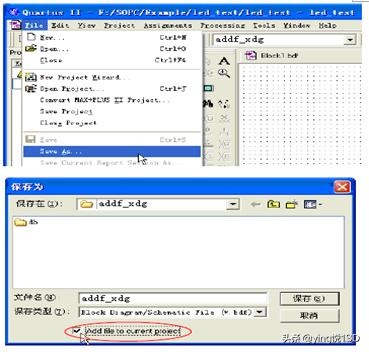

选择 File>>New打开如图1.8所示新件文件对话框,选中Device File页面下的Block Diagram/Schematic File,单击OK,如图1.8a所示,建立一个空的图形设计文件,缺省名为Block1.bdf,选择File>>Save As,打开BDF文件存盘对话框,保存为addf_xdg.bdf,同时选中Add file to current project选项,将文件添加到工程中去,如图1.8b所示。至此,完成顶层模块的建立。

(a)

(b)

图1.8 新件文件对话框

5、 新件文本编辑文件(VHDL源程序文件)

在图1.8a中,重复选择File>>New,打开新件文本对话框,选择Device File页面下的VHDL File,按OK,建立一个缺省名为Vhdl1.vhd的文件,选择File>>Save AS改名为addf.vhd并保存。(编写源程序时需注意,实体名必须和文件名相同)

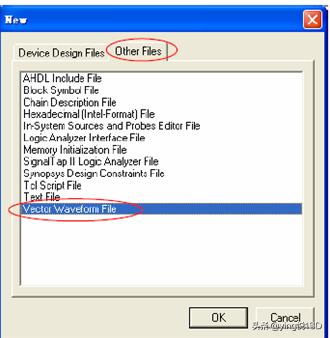

6、 新建波形编辑文件,用于电路仿真。

在图1.8a中,选择File>>New,打开新件文本对话框,选择Other File页面下的Vector Waveform File,如图1.9所示,建立一个空的波形编辑器窗口,缺省名为Waveform1.vwf,选择File>>Save AS改名为addf.vwf并保存。

图1.9 新建波形文件对话框 图1.10 文件浏览栏

图1.10 文件浏览栏

图1.9 新建波形文件对话框 图1.10 文件浏览栏

二、QUARTUS II工程设计

1、在文件中编写源程序

打开addf.vhd文件,输入预习时编写的VHDL源程序。若找不到以前新建的源文件addf.vhd可在如图1.10中的Project Navigator栏内,选中File页面,点开Device Design File项,可找到上一步新建的子文件。编写完模块源程序后,存盘。

注意:VHDL程序中,要求源程序的模块的实体名必须和文件名一致。

2、对编写的源文件进行编译。

具体操作分为三个步骤,具体操作如图1.11:

图1.11 源文件的编译

图1.11 源文件的编译

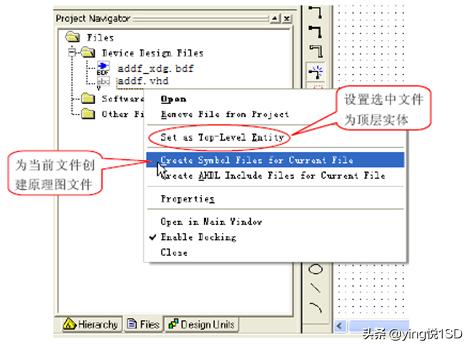

①在Project Navigator栏内,选中File页面,点开Device Design File项,选中addf.vhd文件,单击右键,在弹出的菜单中选中Set at Top-level Entity。将addf.vhd设为顶层实体。

②选择菜单中Process>>Start>>Start Analysis & Synthesis或工具栏上的

进行自动编译。

③若编译后提示有错误,根据状态栏的提示,改正错误后重新编译。

3、 从设计文件创建模块

编译完成后,将编译后的文件创建成模块,用于图形设计文件中,具体操作如下:

在Project Navigator栏内,选中File页面,点开Device Design File项,可找到上一步完成编译的的文件addf.vhd,如图1.11所示,选中后单击右键,在弹出的菜单中,选择Creat Sybol File for Current File,进行编译以后,会弹出对话框,确认模块创建成功。

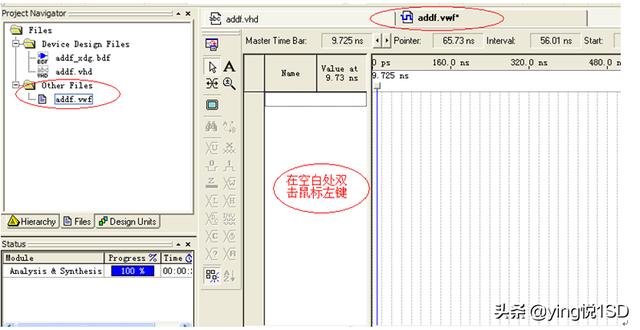

4、模块功能仿真

1)在Project Navigator栏内,选中File页面,点开Other File项,双击打开addf.vwf文件,如图1.12所示。

图1.12 新建波形文件界面

图1.12 新建波形文件界面

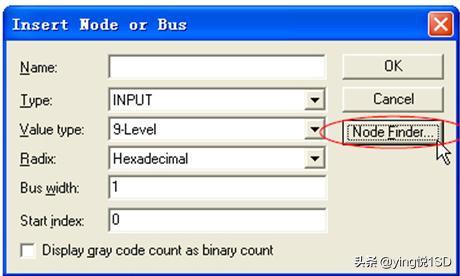

2)在如图1.12所示的Name标签区域内双击鼠标左键,弹出如图 1.13所示的添加节点对话框。

图 1.13 添加节点对话框

图 1.13 添加节点对话框

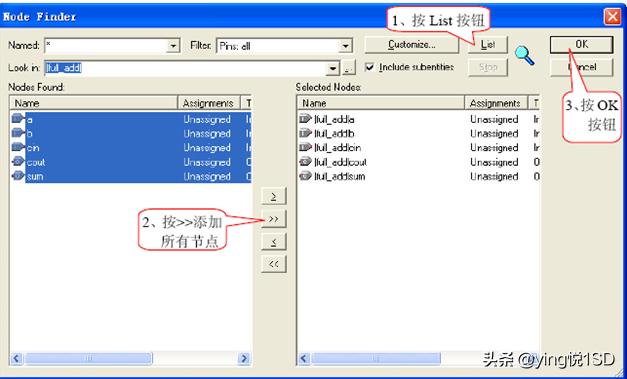

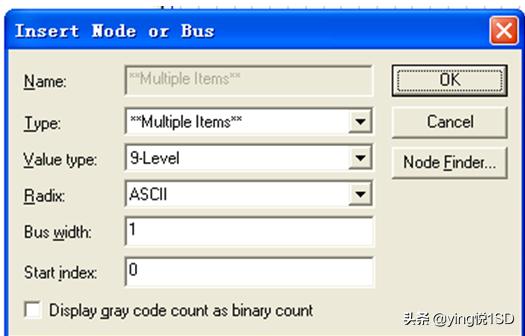

3)在如图1.13所示的添加节点对话框中单击Node Finder 按钮,弹出如图 1.14所示的对话框,按图1.14所示步骤进行选择和设置,单击OK 按钮后弹出如图1.15所示的对话框,再单击OK 按钮完成节点添加,如图1.16所示。

图1.14 添加节点

图1.15 添加节点后的界面

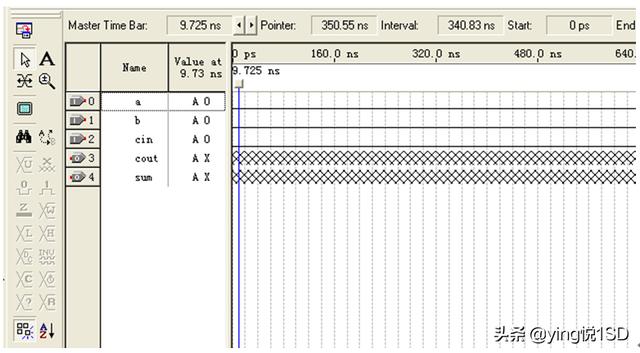

图1.16 添加完节点后的仿真文件界面

图1.14 添加节点

图1.15 添加节点后的界面

图1.16 添加完节点后的仿真文件界面

4)波形编辑器默认的仿真结束时间为1μS,根据仿真需要,可以自由设置仿真文件的结束时间。选择Edit>>End Time 命令,弹出结束时间对话框,在Time 框内输入仿真结束时间,时间单位可选为S、mS(10-3S)、μS(10-6S) 、nS(10-9S) 、pS(10-12S)。单击OK按钮完成设置。在这里采用默认设置(1μS)。

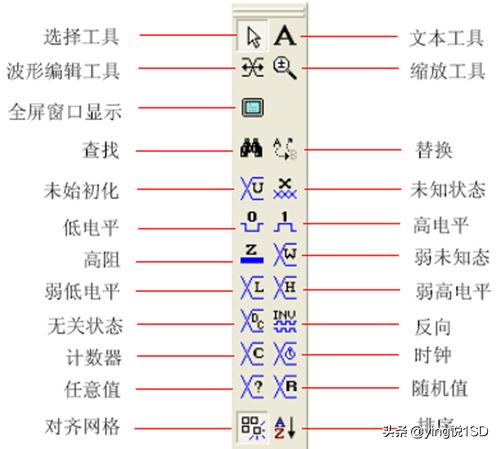

5)编辑输入节点波形。编辑时将使用到波形编辑工具栏中的各种工具。图 1.17显示了工具栏中各工具的功能。选中输入信号后,点计数器工具,弹出如图 1.18所示计数器窗口,选中Timing页面,修改Count every,其中a为20ns,b为40ns,cin为80ns。完成编辑后,各输入信号如图1.19所示,完成后保存文件。

图1.17 波形编辑工具条

图1.18 计数器设置窗口

图1.19 编辑后的输入节点波形

图1.17 波形编辑工具条 图1.18 计数器设置窗口

图1.19 编辑后的输入节点波形

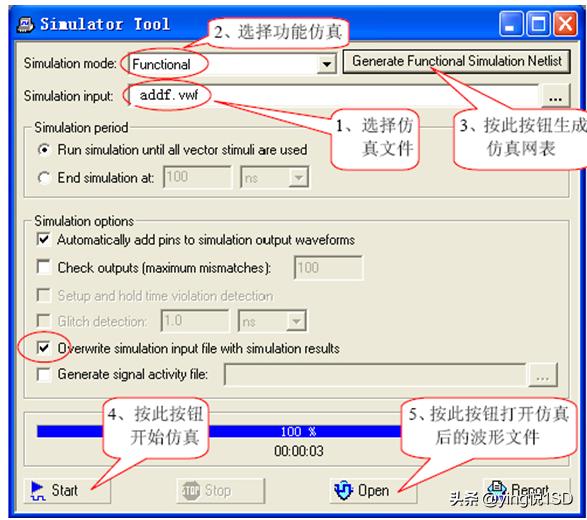

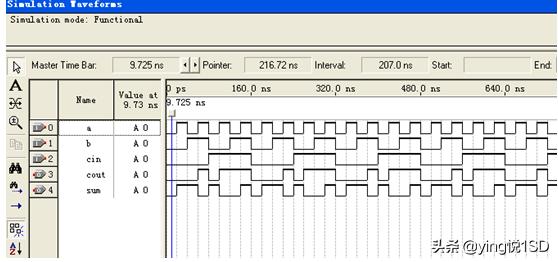

6)选择Processing>>Simulator Tool 命令,弹出如图1.20所示的对话框。按图1.20所示步骤进行选择和设置。1位全加器最后的仿真波形如图1.21所示。

图1.20 仿真设置对话框

图1.21 仿真波形

图1.20 仿真设置对话框

图1.21 仿真波形

7)观察仿真结果是否符合设计要求,保存打印仿真波形。

5、添加模块到Quartus II顶层模块。

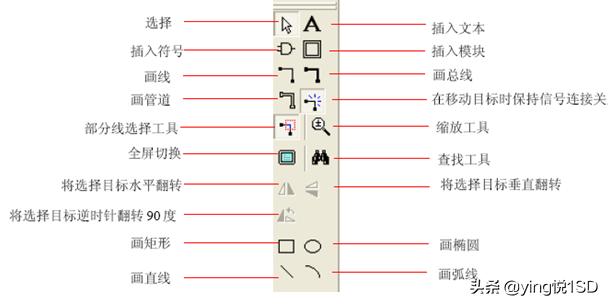

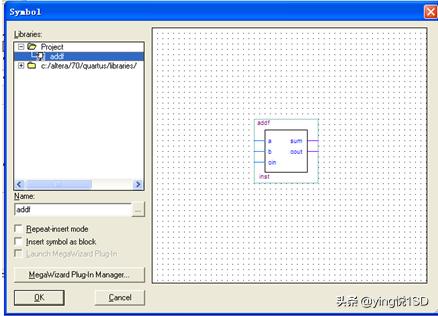

1)在Quartus II中打开的addf.bdf文件,在其左侧,有工具栏,其作用如图1.22所示。在窗口工作区中的任意处双击左键,弹出符号(Symbol)对话框,如图1.23所示。

图1.22 工具栏

图1.22 工具栏

2)在Project下选择addf,在右边的窗口中出现一个大的符号,这就是由addf.vhd源文件生成的模块符号。

3)单击OK,Symbol对话框关闭,addf符号被附在鼠标的指针上,在addf_xdg.bdf的窗口适当位置单击,放置符号。

图1.23 符号(Symbol)对话框

图1.23 符号(Symbol)对话框

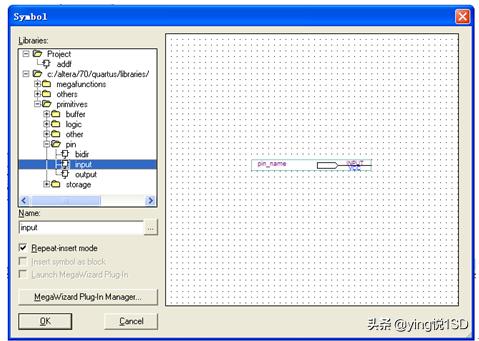

4、 添加引脚和其他基本单元

除了双击编辑区外,也可以使用工具栏上的调出符号对话框,放置引脚和非门。

1)单击模块编辑工具栏中的插入符号按钮,调出符号对话框。在Library窗口中,打开Primitives>>Pin,如图1.24所示,选择输入(input)及输出(output)引脚,并放置在合适的位置。取消放置时点右键,在弹出菜单中选中Cannel。

图1.24添加输入引脚对话框

图1.24添加输入引脚对话框

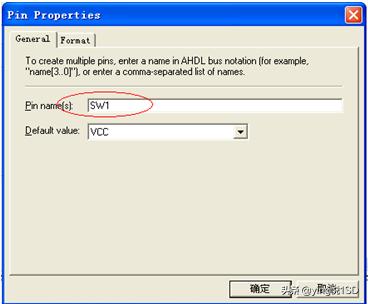

2) 双击端口符号,在弹出窗口如图1.25中,修改端口名字。

图1.25 修改端口名称

图1.25 修改端口名称

3)同理,在Primitives>>logic中,选择非门(not),插入顶层设计图中,并修改名称。

4)用画线工具连线,连接各输入输出端口或中间信号,如图1.26所示,完成以后保存。

图1.26 顶层模块原理图

图1.26 顶层模块原理图

5)选择菜单中Process>>Start>>Start Analysis & Synthesis或工具栏上的

进行自动编译。

5、 选择器件型号及分配FPGA引脚

器件型号在新建项目的时候已经指定,若需要改变,可通过Assignment>>Device,调出Setting对话框修改。一般情况,可省略此步。

在电路设计时,外围电路的接口已经和FPGA对应的引脚连接在一起,实验过程中,只需要查附录中的引脚表,找到对应的引脚,并将其分配锁定既可。分配FPGA引脚步骤如下:

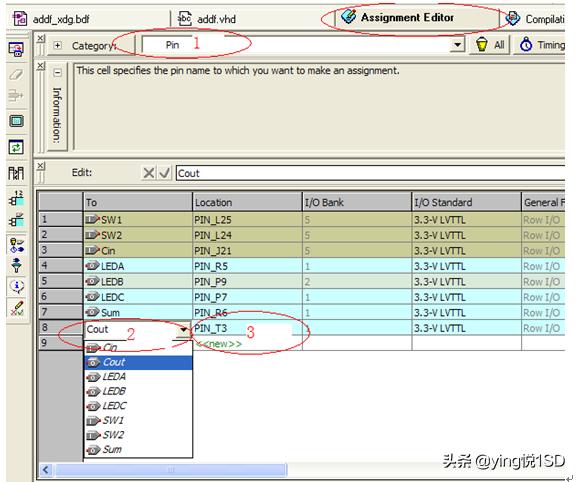

1)选择Assignment>>Assignment Editor打开引脚分配对话框,如图1.27所示。

图1.27 引脚分配界面

图1.27 引脚分配界面

2)在Gategory下拉菜单中选择Pin。

3)在To栏中,输入各引脚名称,或者双击后在下拉框中选定。在Location下拉栏中选择相应的引脚,也可在该栏下输入引脚号,如PIN_R5以次来快速定位,引脚对应关系如表1.2。其他实验对应的引脚,可以通过附录二,查表得知。

表1.2

④选择File>>Save来保存分配,然后关闭Assignment Editor。

6、 器件和引脚的其他设置。

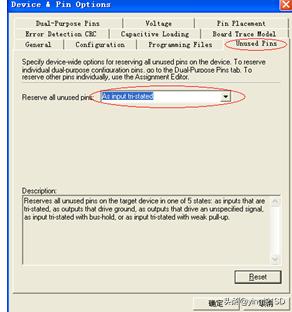

主要用来处理下载方式和其他在设计中没有用到的引脚的设置。选Assignment>>Device,在弹出的对话框中选择Device and Options,弹出Device & Pin Options对话框,如图1.28所示。

1)在Configuration标签页中,选择Auto配置方式。

2)在Unused Pins对话框中,在Reserve all unused pins选项中,将其设置为As input tri-stated,即将其定义为三态输入。如图1.29所示。

注意:在设计中一定要将未定义的引脚定义为三态输入,注意一定不能将未定义(不使用)引脚模式设为输出,并连接到地(As outputs,driving ground)。否则会造成未使用的芯片冲突而损坏芯片。

图1.28 下载方式配置

图1.29 不使用引脚的配置

图1.28 下载方式配置 图1.29 不使用引脚的配置

三、综合编译

1、设置编译选项。本实验采用默认的编译设置,不进行其他修改。

2、编译硬件系统。

在编译过程中,编译器定位并处理所有工程文件,生成与便宜相关的信息与报告,创建sof文件及任何可选配置文件。

1)在Project Navigator栏内,选中File,点开Device Design File项,选中文件addf_xdg.bqf,单击鼠标右键,在弹出的菜单中单击Set at top-level Enity选项,将addf_xdg.bqf设置为顶层实体。

2)选择Processing>>Start Compilation进行全程编译,也可以选择工具栏上的按钮启动编译,对该工程文件进行编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。编译结果可以在Compilation Report窗口中查看。整个编译过程可能会持续数分钟,另外编译过程中可能会产生很多警告信息,这些不影响设计结果。

3、查看编译报告

编译结束后,对话框显示"Full compilation wa successful

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?