单片机基础(05)

5.1 MCS51单片机的最小系统

所谓最小系统,是指可独立工作的单片机,所需要的最小配置电路。MCS-51单片机根据片内有无程序存储器最小系统分两种情况。

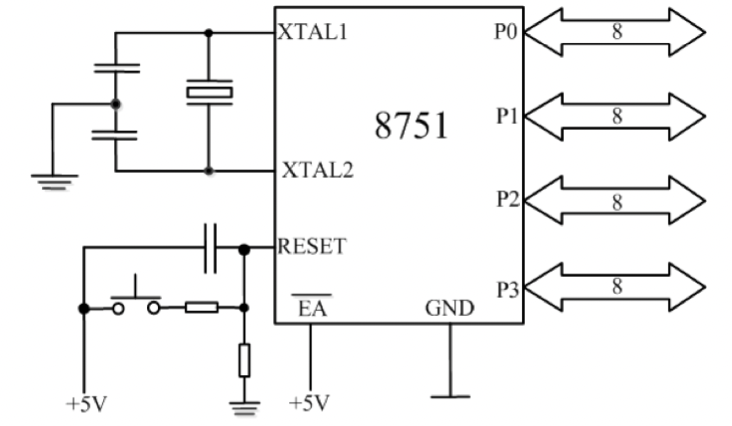

8051/8751片内有4kB的ROM/EPROM,只需要外接晶体振荡器和复位电路就可构成最小系统。如图所示。

该最小系统的特点:

由于片外没有扩展存储器和外设,PO、P1、P2、P3都可以作为用户I/O口使用。

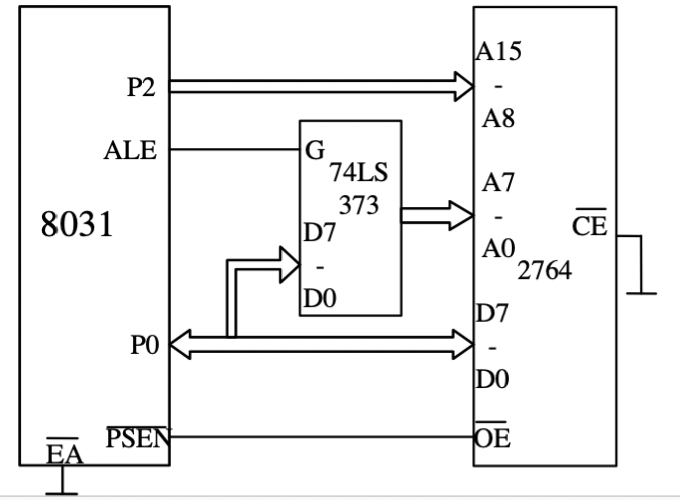

8031最小应用系统

8031片内无程序存储器片,在构成最小应用系统不仅要外接晶体振荡器和复位电路,还应外扩展程序存储器。

单片机外部总线扩展的基本思路

5.2单片机片外总线扩展存储器

MCS-51单片机的存储器扩展能力

片外程序存储器可扩展64kB,地址:0000H~FFFFH。

片外数据存储器可扩展64kB,地址:0000H~FFFFE。

存储器扩展的一般方法

不论何种存储器芯片,其引脚都呈三总线结构,与单片机连接都是三总线对接。

-

控制线

- 程序存储器:ROM芯片输出允许控制线 OE与单片机的PSEN信号线相连。

- 数据存储器:RAM芯片输出允许控制线oE和写控制线WE分别与单片机的读信号线RD和写信号线WR相连。

-

数据线:存储器芯片的数据线与单片机的数据总线

(PO。0~PO。7)按由低位到高位的顺序相接。 -

地址线:存储器芯片的地址线的数目由芯片的容量决定。

容量(Q)与地址线数目(ND)满足关系式: Q = 2 N Q=2^N Q=2N。 -

芯片选择引脚:每一个连接在公共总线上的芯片都有片选输入引脚(CS,一般为低电平有效),用于供CPU选择某个时刻使能该芯片被选中,占用总线。而当片选引脚电平无效时,芯片不被选中,芯片与总线连接引脚呈高阻隔离状态。

译码有两种方法:部分译码法和全译码法。

部分译码:存储器芯片的地址线与单片机系统的地址线顺次相接后,剩余的高位地址线仅用一部分参加译码,包括某根线直接接片选端(线选法)。

程序存储器扩展

单片程序存储器的扩展

A15直接连接CS端

多片程序存储器的扩展

第一片的地址空间为:

第二片的地址空间为:

全译码:存储器芯片的地址线与单片机系统的地址线顺次相接后,剩余的高位地址线全部参加译码。这种译码方法存储器芯片的地址空间是唯一确定的,但译码电路相对复杂。

由于采用全译码,每片2764的地址空间唯一,分别是:

5.3 单片机总线扩展并行IO口

输入/输出口扩展

简单I/O口扩展

通常通过数据缓冲器、锁存器来扩展简单I/O接口。例如:74LS373 74LS244、74LS273、 74LS245等芯片都可以作简单I/0扩展。

绝对地址的访问

C51编译器提供了一组宏定义来对51系列单片机的code、xdata空间进行绝对寻址.规定只能以无符号数方式访问,定义了宏定义,其函数原型如下:

#define CBYTE((unsigned char volatile*)0x50000L)

#define XBYTE((unsigned char volatile*)0x20000L)

#define CwORD((unsigned int volatile*)0x50000L)

#define XWORD((unsigned int volatile*)0x20000L)

这些函数原型放在absacch文件中。使用时须用预处理命令把该头文件包含到文件中,形式为:#include <absacc.h>。

其中:

- CBYTE以字节形式对code区寻址,

- XBYTE以字节形式对xdata区寻址,

- CWORD以字形式对code区寻址,

- XWORD以字形式对xdata区寻址。访问形式如下:

宏名[地址]

宏名为CBYTE、 XBYTE、 CWORD 或XWORD。地址为存储单元的绝对地址。

绝对地址对存储单元的访问

#include <absacc.h> //将绝对地址头文件包含在文件中

#include <reg51.h> //将寄存器头文件包含在文件中

void main(void) {

unsigned char var1;

unsigned int var2;

var1=XBYTE[0x0005]; // 访问片外RAM的0005字节单元

var2=XWORD[0x0002]; // 访问片外RAM的0002字单元

}

图中,扩展的输入口接了K0K78个开关,扩展的输出口接了LOL78个发光二极管,如果要实现K0K7开关的状态通过LOL7发光二极管显示,

#include <reg51.h>

#include <absacc.h> // 定义绝对地址访问

#define uchar unsigned char

void main(void){

uchar i;

while(1){

i=XBYTE[0x7fff]; // 读74LS244扩展的输入口

XBYTE[0x7fff]=i; // 输出到74LS373扩展的输出口

}

}

5.4单片机外部总线扩展并口芯片8255

可编程I/O扩展(8255A)

8255A的结构与功能

8255A是一款可编程并行IO接口扩展芯片,通过单片机总线连接,可使单片机扩展出3个8位并行IO口。

扩展的并行IO口具有多种工作模式,可实现方向控制、询问、应答控制等多种功能,可用于单片机对各种不同速度要求的外部设备的IO口控制。

3个可编程的并行I/0端口:PA口、PB口和PC口

| C S ‾ \overline{CS} CS | A1 | A0 | R D ‾ \overline{RD} RD | W R ‾ \overline{WR} WR | I/O操作 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 读A口寄存器内容到数据总线 |

| 0 | 0 | 1 | 0 | 1 | 读B口寄存器内容到数据总线 |

| 0 | 1 | 0 | 0 | 1 | 读C口寄存器内容到数据总线 |

| 0 | 0 | 0 | 1 | 0 | 数据总线上内容写到A口寄存器 |

| 0 | 0 | 1 | 1 | 0 | 数据总线上内容写到B口寄存器 |

| 0 | 1 | 0 | 1 | 0 | 数据总线上内容写到C口寄存器 |

| 0 | 1 | 1 | 1 | 0 | 数据总线上内容写到控制口寄存器 |

8255A的引脚信号

- D7~DO:三态双向数据线,与单片机的数据总线相连。

- C S ‾ \overline{CS} CS:片选信号线,低电平有效,用于选中8255公芯片。

- R D ‾ \overline{RD} RD:读信号线,低电平有效,用于控制从8255A端口读出信息。

- W R ‾ \overline{WR} WR:写信号线,低电平有效,用于控制向8255A端口写入信息。

- A1, A0:地址线,用来选择8255A的内部端口。

- PA7~PA0, PB7~PB0, PC7~PC0: A、 B、C口的8根I/O信号线,用于与外部设备连接。

- RESET:复位信号线。

- V c c V_{cc} Vcc:+5v电源线。GND:地信号线。

8255A的控制字

8255A有两个控制字:工作方式控制字和C口按位置位/复位控制字

-

工作方式控制字

-

C口按位置位/复位控制字

8255A的工作方式

- 方式0

- 具有两个8位端口(A、B和两个4位端口(C口的高4位和C口的低4位)。

- 任何一个端口都可以设定为输入或者输出。

- 每一个端口输出时锁存,而输入时不锁存。

- 方式1

- A口和B口作为数据I/O口,C口用作I/0的应答信号。

方式0输入/输出时没有专门的应答信号,通常用于无条件传送。

例如:下图是8255A工作于方式0的例子,其中A口输入,B口输出。

-

方式1输入(单向并行口读入数据通信,带查询/应答机制)

- S T B ‾ \overline{STB} STB:外设送给8255A的“输入选通〞信号

- IBF: 8255A送给外设的“输入缓冲器满〞信号

- INTR: 8255A发送给CPU的“中断请求〞信号

- INTE:8255A内部为控制中断而设置的“中断允许”信号

-

方式1输出(单向并行口输出数据通信,带查询/应答机制)

- O B F ‾ \overline{OBF} OBF:8255A送给外设的“输出缓冲器满〞信号

- A C K ‾ \overline{ACK} ACK:外设送给8255A的“应答”信号

- INTR: 255A送给CPU的“中断请求〞信号

- INTE:8255A内部为控制中断而设置的“中断允许〞信号

-

方式2(双向并行口数据通信,带查询/应答机制)

8255A与MCS-51单片机的接口

-

硬件接口

8255A的A口、B口、C口和控制口的地址分别是7F00H、 7F01H、 7F02H和7F03HI (高8位地址线未用的取1,低8位地址线未用的取0).

-

软件编程

A口接开关K0~K7,B口接发光二极管L0~L7,要求从A口读入开关状态通过B口显示出来。8255A的工作方式控制字为1000 0010B (82H)

#include <reg51.h> #include <absacc.h> //定义绝对地址访问 #define uchar unsigned char void main(void){ uchar i; XBYTE[0x7f03]=0x82; // 8255A初始化,B口方式0输入,A口方式0输出 while(1){ i = XBYTE[0x7f01]; //从B口输入 XBYTE[0x7f00] = i; //从A口输出 } }

5.5 LED数码管的工作原理及驱动方法

LED显示器的结构与原理

在单片机应用系统中通常使用的是7段式LED数码管显示器,如图所示。

LED数码管的内部结构

7段式LED数码管显示器,它有共阴极和共阳极两种。

LED数码管的字段码

- 显示字符0,共阴极字段码为0x3F,共阳极为0xC0

LED数码管字型码表

| 显示字符 | 共阴极字段码 | 共阳极字段码 | 显示字符 | 共阴极字段码 | 共阳极字段码 |

|---|---|---|---|---|---|

| 0 | 3FH | C0H | C | 39H | C6H |

| 1 | 06H | F9H | D | 5EH | A1H |

| 2 | 5BH | A4H | E | 79H | 86H |

| 3 | 4FH | B0H | F | 71H | 8EH |

| 4 | 66H | 99H | P | 73H | 8CH |

| 5 | 6DH | 92H | U | 3EH | C1H |

| 6 | 7DH | 82H | T | 31H | CEH |

| 7 | 07H | F8H | Y | 6EH | 91H |

| 8 | 7FH | 80H | L | 38H | C7H |

| 9 | 6FH | 90H | 8.(全亮) | FFH | 00H |

| A | 77H | 88H | “灭” | 00 | FFH |

| B | 7CH | 83H | … | … | … |

LED数码管显示器的译码方式

硬件译码方式

硬件译码方式是指利用专门的硬件电路来实现显示字符到字段码的转换,如

MOTOTOLA公司生产的MC14495芯片,MC14495是共阴极一位十六进制数-字段码转换芯片,能够输出用四位二进制表示形式的一位十六进制数的七位字段码,不带小数点。

静态显示方式

数码管公共端接固定电平,各笔画段位与1/0引脚相连,程序直接控制I/0口显示字符。

动态显示是将多个数码管的每一位笔划段并接在一起,用八个I/O口控制,公共端通过不同的I/O口线控制。工作时,逐位选中数码管并显示各自字符,循环点亮,利用人眼的暂态效应,达到显示效果。

动态显示技术中难点在于:扫描移位的切换过程:

5.6 LED数码管与单片机的接口

LED显示器与单片机的接口

硬件译码静态显示

在实际应用时,如果数码管个数较少,通常用硬件译码静态显示,在数码管个数较多时,则通常用软件译码动态显示。

软件译码动态显示

下图是一个8位软件译码动态显示的接口电路图。

P1口输出数据信号,PO口输出位选信号。数码管为共阴极,低电平选中。

#include <reg51.h>

#define uchar unsigned char

#define uint unsigned int

uchar disbuffer[8]={0,1,2,3,4,5,6,7}; //定义显示缓冲区

uchar codevalue[16]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07, 0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71}; //0~F的字段码表

uchar chipcode[8]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f}; // 位选码表

void main(void) {

while(1){

display(); // 设显示函数

}

}

void display(void) {

uchar i,p,temp;

for (i=0;i<8;i++) {

P0=0xFF;

p=disbuffer[i]; //取当前显示的字符

temp=codevalue[p]; //取出显示数字对应字段码

P1=temp; //送出字段码

P0 =chipcode[i]; //送出位选码

delay(20); //延时

}

}

void delay(uint i) {

for (;i>0;i++); //延时函数

}

LED动态显示技术的扩展应用

LED点阵

LED点阵器件构造和多位数码管很相似。

LED点阵显示驱动原理完全一样。

LED手摇棒的实现

手摇棒可通过晃动单排LED灯,显示整幅图形。单片机检测手摇棒所在不同位置,控制LED灯显示不同列的图形。

LED旋转电子钟的设计

由于人手摇的频率不稳定,手摇棒显示LED图形的效果并不流畅。当使用小直流电机带动单列LED转动,显示的效果更流畅。

旋转电子钟相当于一个环形LED点阵。

1208

1208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?