1 产品概述

1.1 介绍

S5P6818是一款基于64位RISC处理器的系统级芯片(SoC),适用于平板电脑和手机。采用28纳米低功耗工艺设计,S5P6818的特点包括:

- Cortex-A53 八核CPU

- 最高内存带宽

- 全高清显示

- 1080p 60帧视频解码和1080p 30帧视频编码硬件

- 3D图形硬件

- 高速接口,如eMMC4.5和USB 2.0

S5P6818使用基于ARMv8-A架构的Cortex-A53八核处理器,在AArch32执行状态下为ARMv7 32位代码提供更高性能,并在AArch64执行状态下支持64位数据和更大的虚拟地址空间。它提供6.4 GB/s的内存带宽,用于1080p视频编码和解码、3D图形显示以及全高清显示的高分辨率图像信号处理。该应用处理器支持动态虚拟地址映射,有助于软件工程师轻松充分利用内存资源。

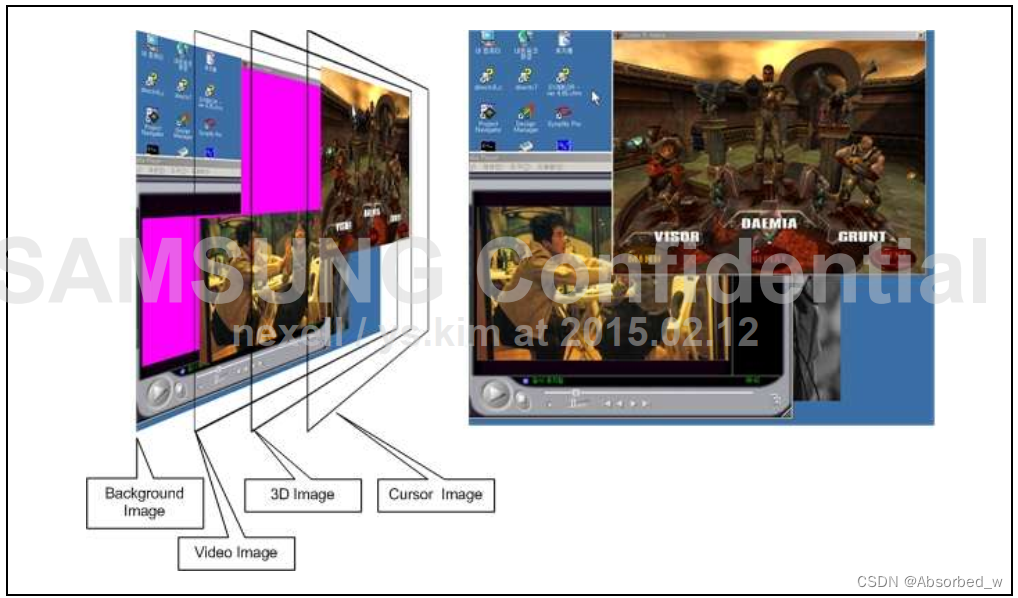

S5P6818通过广泛的API(如OpenGL ES1.1, 2.0)提供最佳的3D图形性能。卓越的3D性能完全支持全高清显示。原生双显示特别支持主LCD显示器的全高清分辨率和通过HDMI的1080p 60帧高清电视显示,能够同时进行。独立的后处理管线使S5P6818能够实现真正的显示场景。

1.2 特点

- 28纳米,高K金属栅极(HKMG)工艺技术

- 537针脚FCBGA封装,0.65毫米球间距,17×17毫米体积

- Cortex-A53八核CPU,主频 >1.4 GHz(待定)

- 高性能3D图形加速器

- 全高清多格式视频编解码器

- 支持各种内存

- LPDDR2/3,最高频率533 MHz(待定)

- LVDDR3(低电压DDR3),DDR3最高频率800 MHz(待定)

- 支持MLC/SLC NAND闪存,具有硬件纠错码算法(4/8/12/16/24/40/60位)

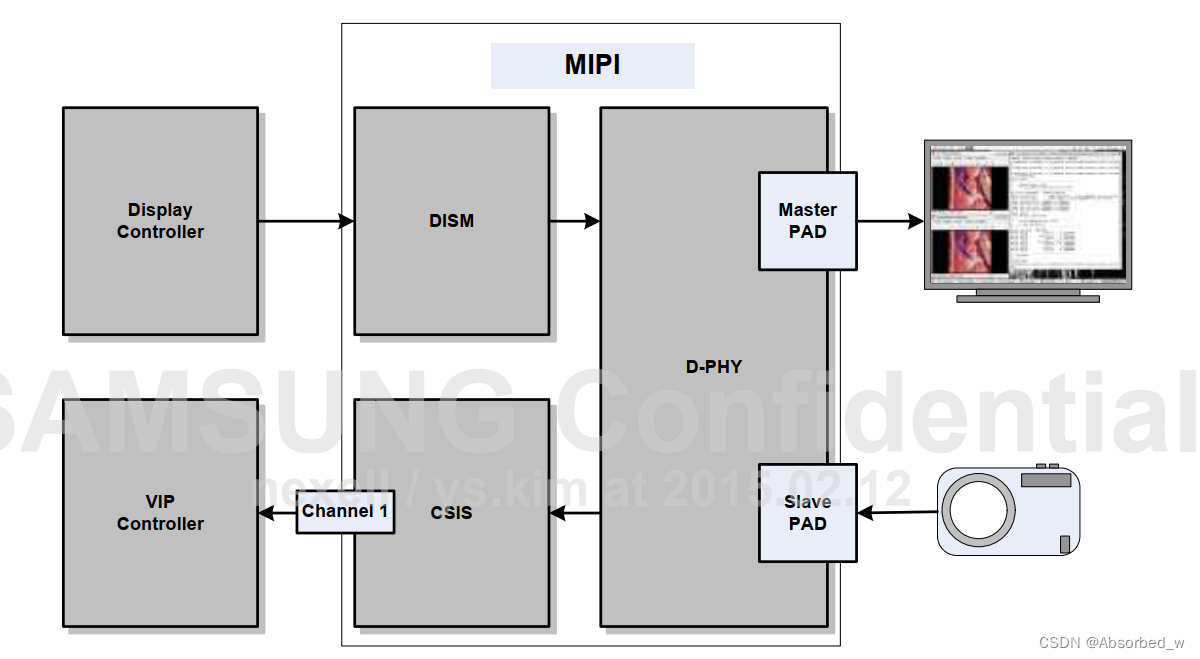

- 支持1920×1080分辨率的双显示,TFT-LCD,LVDS,HDMI 1.4a,MIPI-DSI和CVBS输出

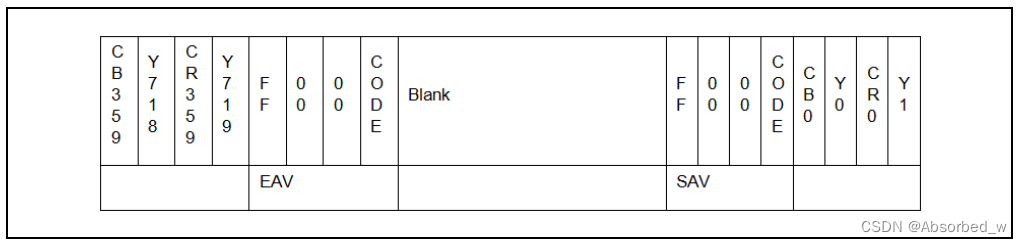

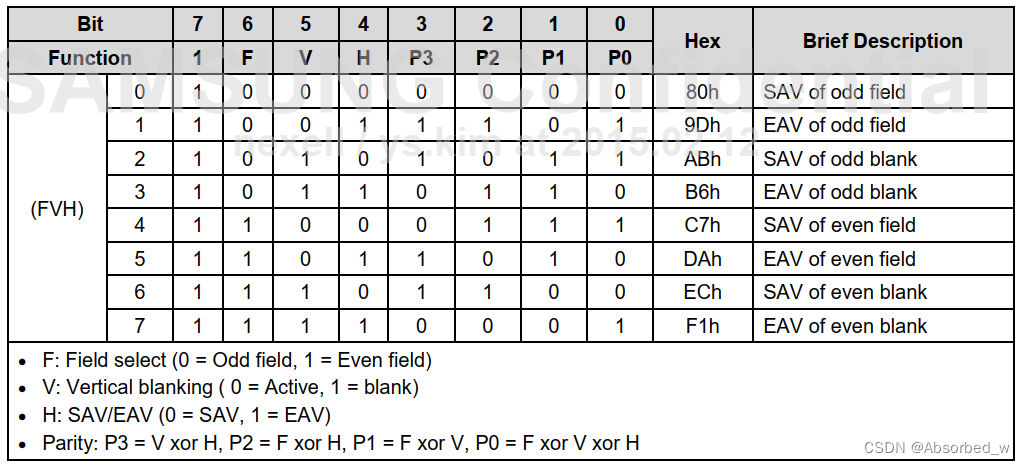

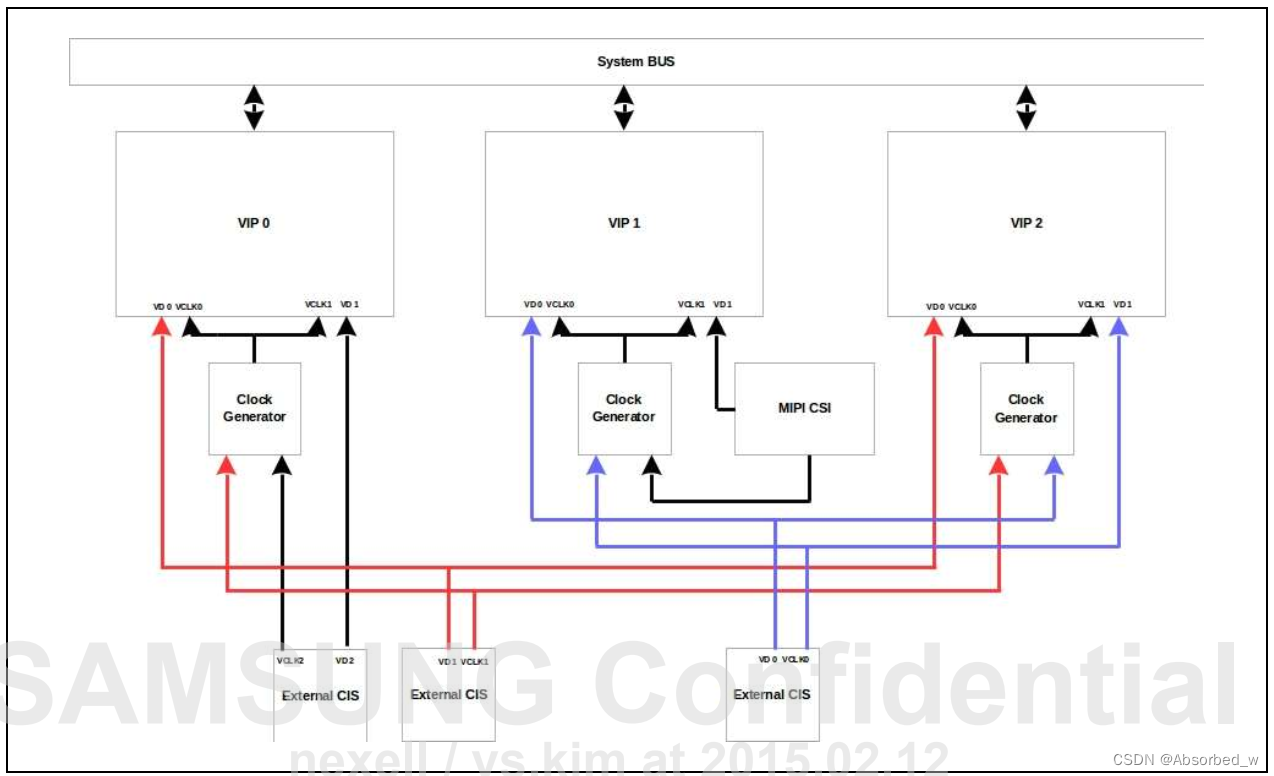

- 支持3通道ITUR.BT 656并行视频接口和MIPI-CSI

- 支持10/100/1000M位以太网MAC(RGMII接口)

- 支持3通道SD/MMC,6通道UART,32通道DMA,4通道定时器,中断控制器,RTC

- 支持3通道I2S,SPDIF接收/发送,3通道I2C,3通道SPI,3通道PWM,1通道PPM和GPIO

- 支持8通道12位ADC,1通道10位DAC用于CVBS

- 支持MPEG-TS串行/并行接口和MPEG-TS硬件解析器

- 支持1通道USB 2.0主机,1通道USB 2.0 OTG,1通道USB HSIC主机

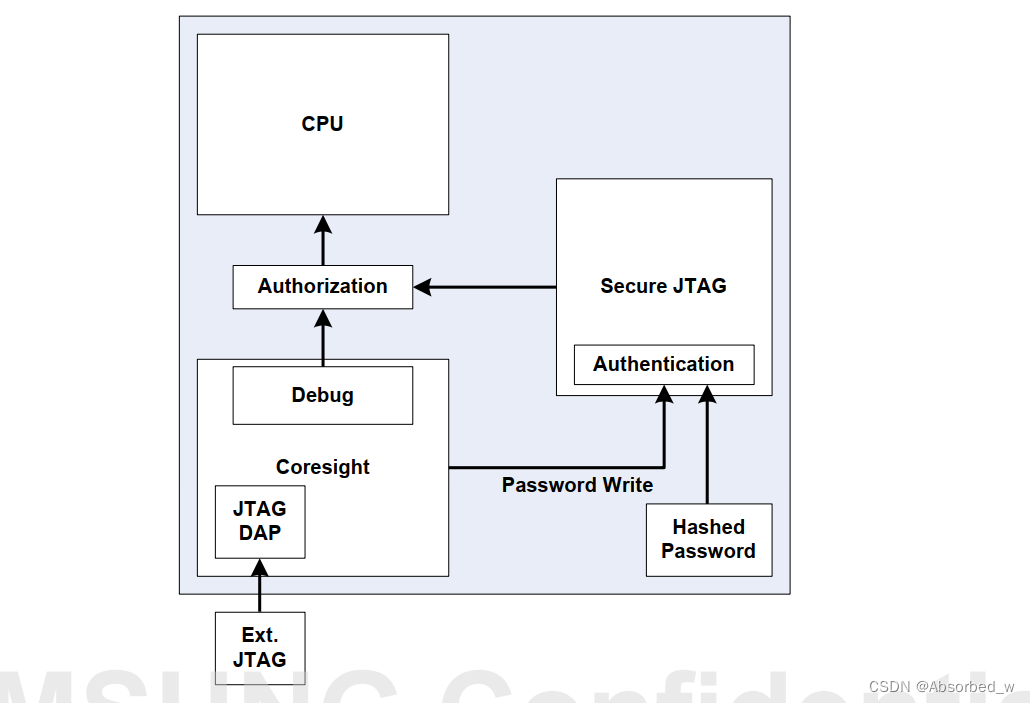

- 支持安全功能(AES,DES/TDES,SHA-1,MD5和伪随机数生成器)和安全JTAG

- 支持ARM TrustZone技术

- 支持各种电源模式(正常模式,睡眠模式,停止模式)

- 支持各种启动模式,包括NAND(具有ECC检测和校正),SPI闪存/EEPROM,NOR,SD(eMMC),USB和UART

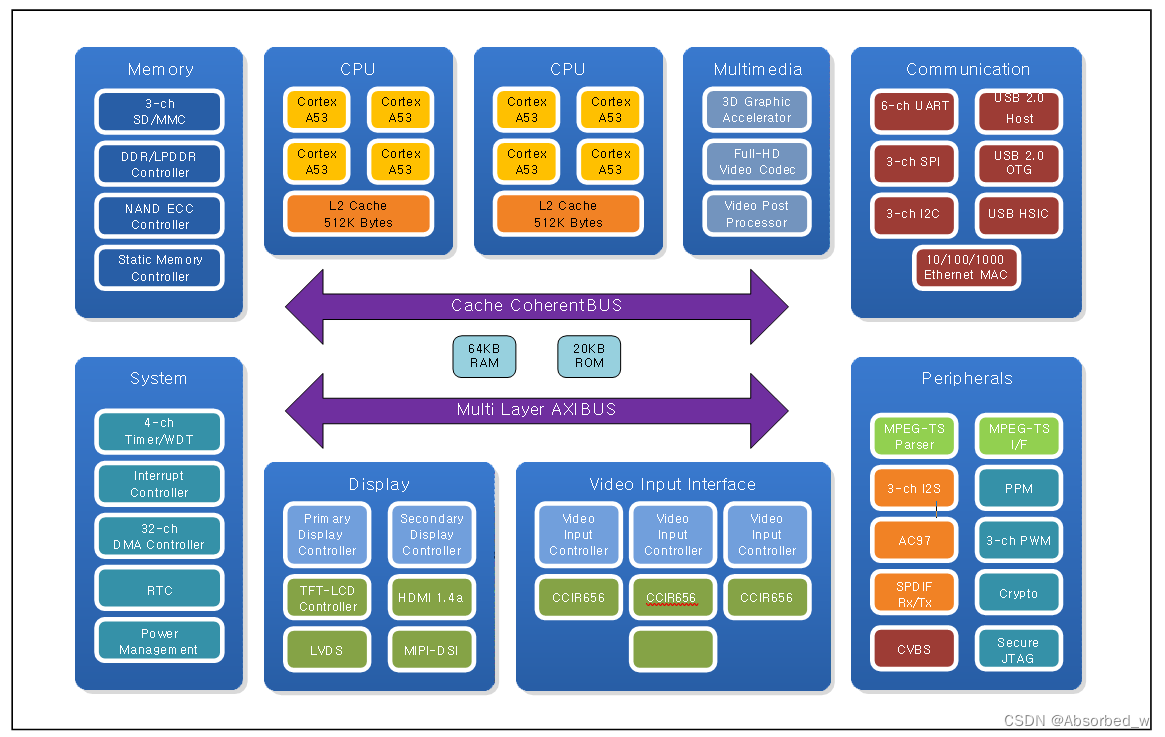

1.3 模块图

1.4 简要功能规格

1.4.1 CPU

- Cortex-A53 八核,主频 >1.4 GHz

- L1 缓存

- 32 KB I-Cache, 32 KB D-Cache

- L2 缓存

- 1 MB 共享缓存

- 协处理器

- VFP(向量浮点处理器),Neon处理器

1.4.2 时钟与电源管理

- 4个扩展频谱PLL

- 外部晶体:24 MHz(用于PLL),32.768 kHz(用于RTC)

- 支持多种电源模式

- 正常、空闲、停止

- 睡眠模式(Suspend to RAM)

1.4.3 DMA

- 32通道DMA

- 操作模式

- 内存到内存传输

- 内存到IO传输,IO到内存传输

1.4.4 中断控制器

- 向量中断控制器

- 支持128通道中断源

- 支持以下功能

- 固定硬件中断优先级

- 可编程中断优先级

- 硬件中断优先级屏蔽

- 可编程中断优先级屏蔽

- IRQ和FIQ生成

- 软件中断生成

- 测试寄存器

- 原始中断状态

- 中断请求状态

1.4.5 计时器与看门狗计时器

- 4通道计时器与看门狗计时器

- 带中断请求的正常间隔计时器模式

- 当计时器计数值达到0(超时)时,激活内部复位信号

- 电平触发中断机制

1.4.6 实时时钟(RTC)

- 32位计数器

- 支持报警中断

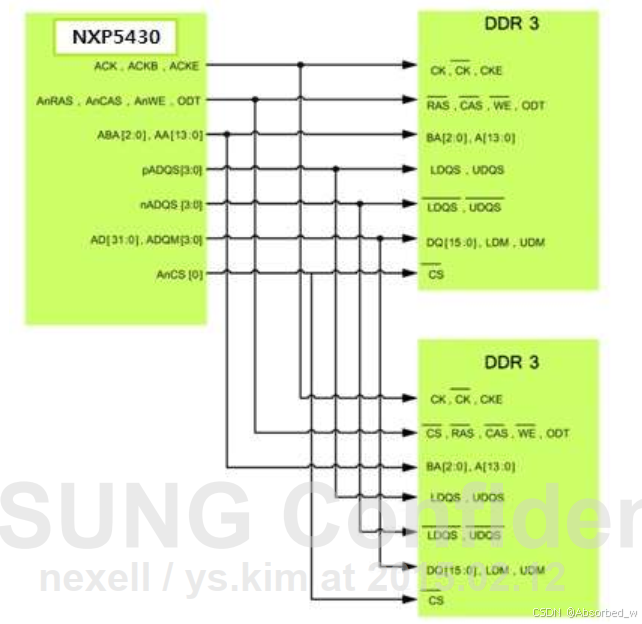

1.4.7 内存控制器

- 系统内存控制器

- 支持LPDDR2/LPDDR3/LVDDR3(低电压DDR3)/DDR3 SDRAM,容量最高达2 GB

- 支持1.2 V至1.5 V电源

- 最大操作频率:800 MHz(DDR3,LVDDR3),533 MHz(LPDDR2,LPDDR3)

- 数据总线宽度:32位

- 静态内存控制器

- 多路复用地址:最多24位

- 支持SRAM、ROM和NAND闪存

- 突发读/写

- NAND闪存控制器

- 支持SLC/MLC NAND闪存

- 支持SLC NAND启动

- 硬件纠错码算法

- 4/8/12/16/24/40/60位BCH错误校正

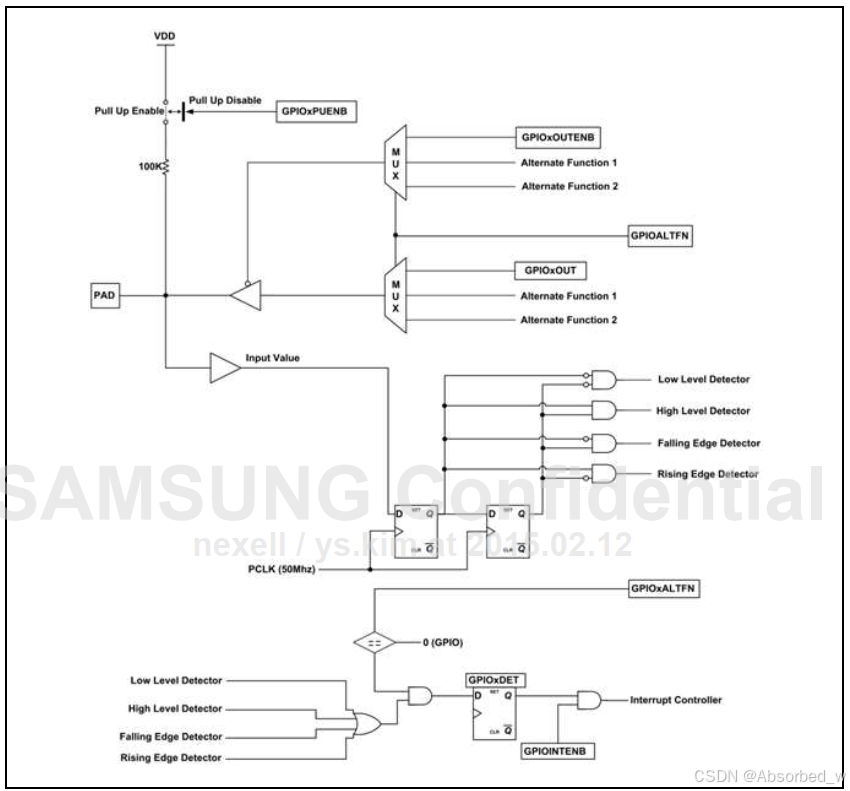

1.4.8 GPIO控制器

- 各种GPIO中断模式

- 上升沿、下降沿、高电平、低电平检测

- 独立中断生成

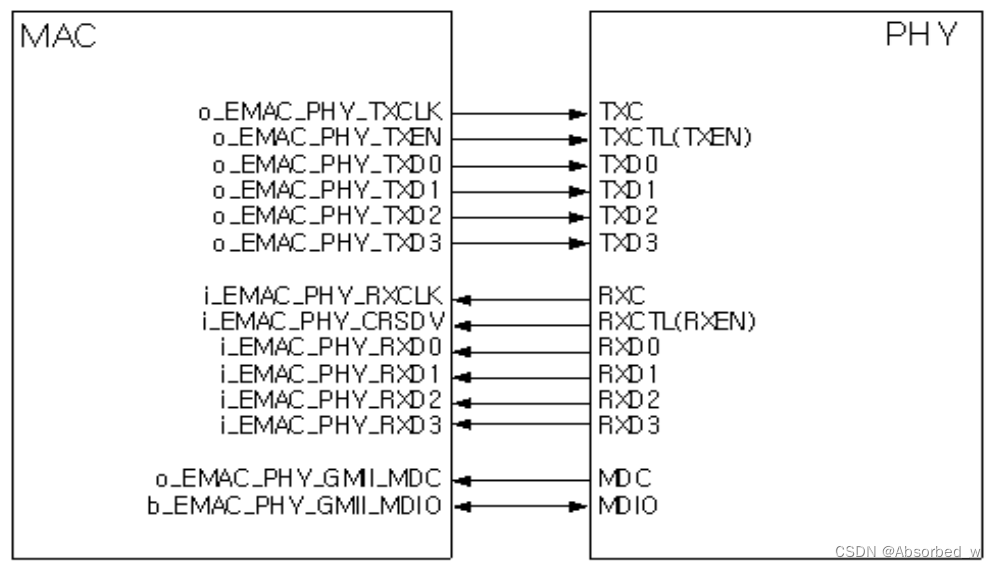

1.4.9 以太网MAC控制器

- 标准符合性

- IEEE 802.3az-2010,节能以太网(EEE)

- HP/Marvell的RGMII规范版本2.6

- MAC支持以下功能

- 10、100和1000 Mbps数据传输速率,以下PHY接口:

- RGMII接口与外部千兆PHY通信

- 全双工操作:

- IEEE 802.3x流量控制,流量控制输入解除时自动传输零量暂停帧

- 可选的接收到的暂停帧转发到用户应用程序

- 半双工操作:

- 支持CSMA/CD协议

- 支持使用反压的流量控制

- 在1000 Mbps半双工操作中支持帧突发和帧扩展

- 发送路径中的前导码和帧开始数据(SFD)插入

- 接收路径中的前导码和SFD删除

- 自动生成的CRC和填充字节,按帧控制

- 接收帧的自动填充字节和CRC剥离选项

- 灵活的地址过滤模式,如:

- 最多31个附加的48位完美(DA)地址过滤器,每个字节的掩码

- 最多96个附加的48位完美(DA)地址过滤器,可以分32和64个块选择

- 最多31个48位SA地址比较检查,每个字节的掩码

- 64位、128位或256位哈希过滤器(可选)用于多播和单播(DA)地址

- 通过所有多播地址帧的选项

- 混杂模式,用于网络监控时通过所有帧而不进行过滤

- 按状态报告通过所有传入数据包(按过滤器)

- 可编程帧长度,支持标准或巨型以太网帧,最大支持16 KB大小

- 可编程帧间隔(IFG)(40-96位时间,以8位为步长)

- 减小前导码大小的帧传输选项

- 独立的32位发送和接收数据包状态

- 接收帧的IEEE 802.1Q VLAN标签检测

- 额外的帧过滤:

- 基于VLAN标签的:完美匹配和基于哈希(可选)过滤

- 基于第3层和第4层:TCP或UDP通过IPv4或IPv6

- 应用程序的单独传输、接收和控制接口

- MDIO主接口(可选)用于PHY设备配置和管理

- 标准IEEE 802.3az-2010节能以太网

- 在传输帧中,通过帧控制实现CRC替换、源地址字段插入或替换、以及VLAN插入、替换和删除

- 可编程接收路径的看门狗超时限制

- 10、100和1000 Mbps数据传输速率,以下PHY接口:

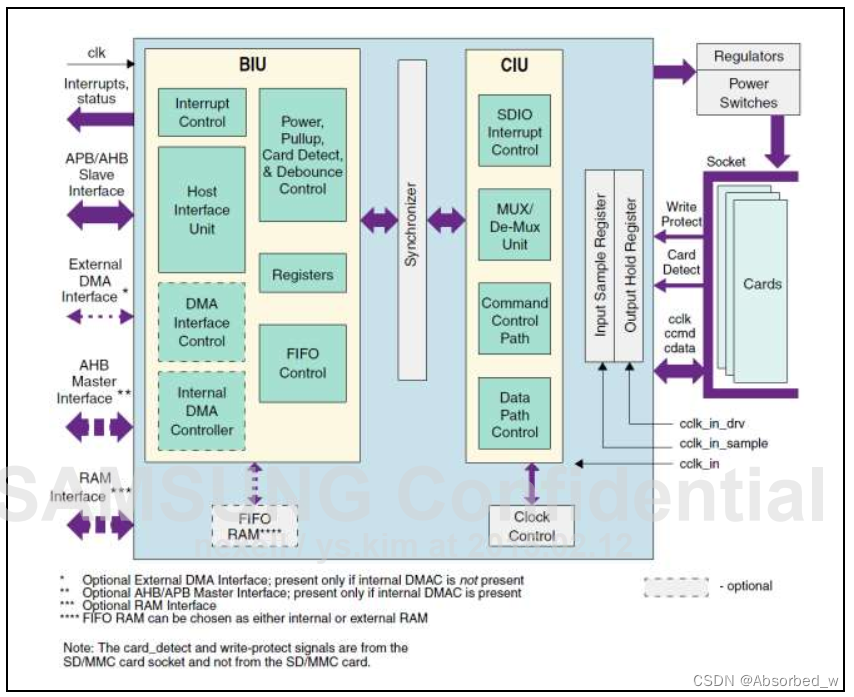

1.4.10 SD/MMC控制器

- 3个独立的SD/MMC控制器和端口

- 安全数字存储(SD存储器-版本3.0)

- 安全数字I/O(SDIO-版本3.0)

- 消费电子高级传输架构(CE-ATA-版本1.1)

- 多媒体卡(MMC-版本4.41,eMMC 4.5)

- 支持MMC4.41的功能

- 支持eMMC4.5的功能

- 支持8位DDR模式,频率最高可达50 MHz

- 支持PIO和DMA模式的数据传输

- 支持1/4位数据总线宽度

- 将SPI信号覆盖到SSP/SPI控制器的相同GPIO

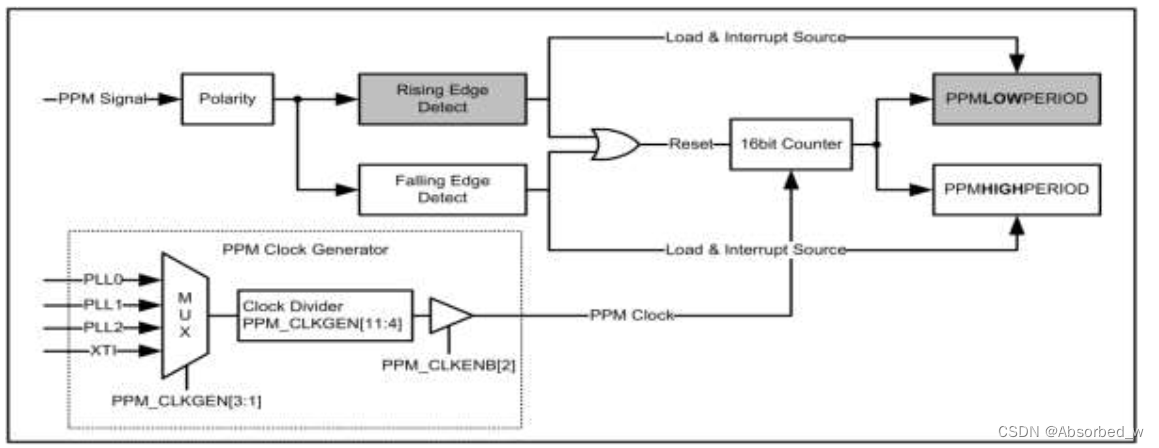

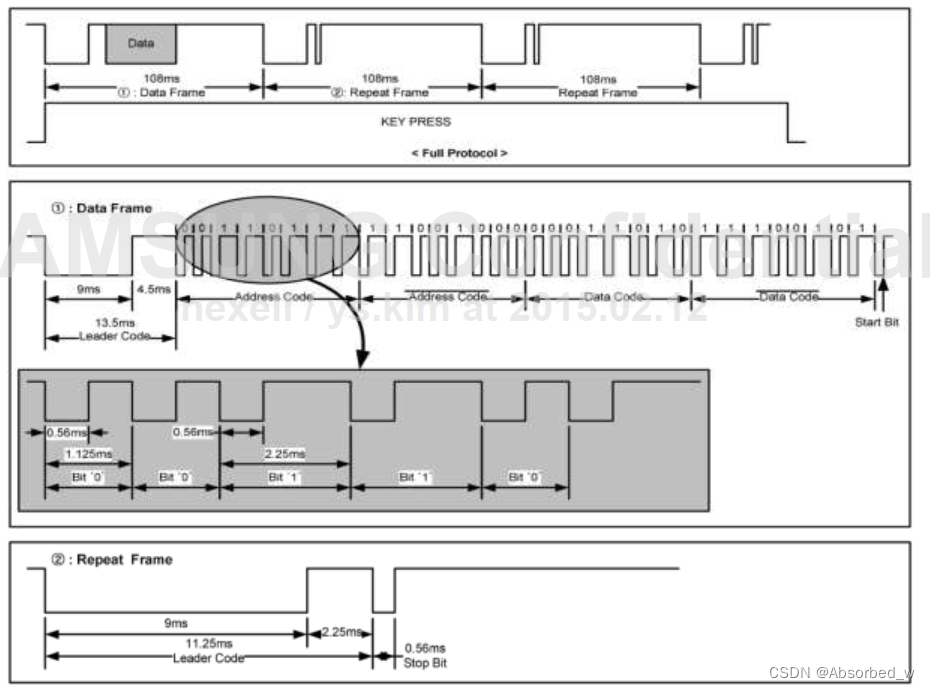

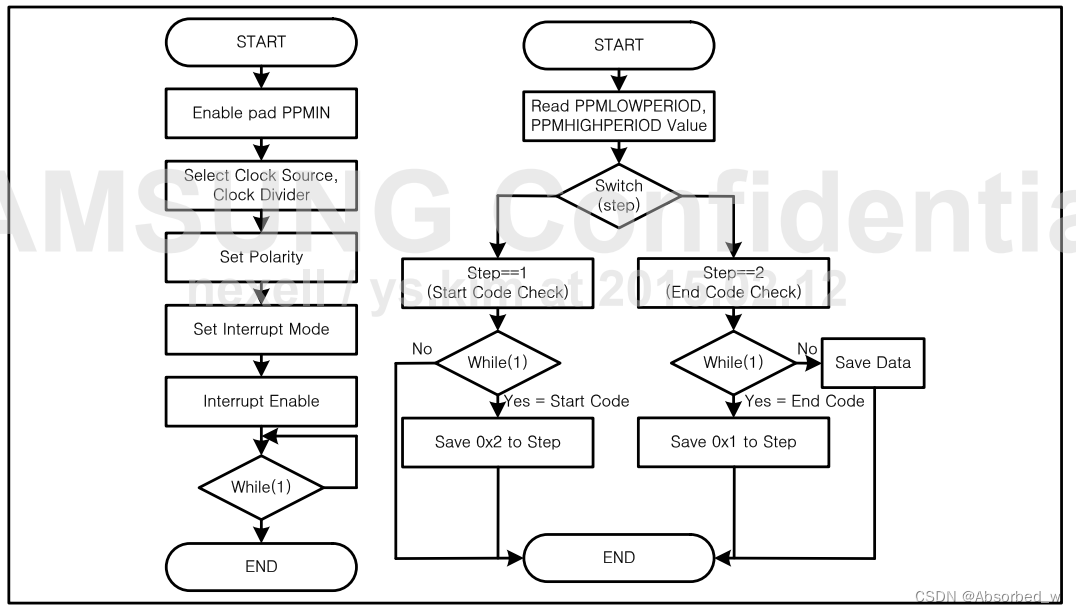

1.4.11 PPM

- 脉冲周期测量用于红外遥控接收器

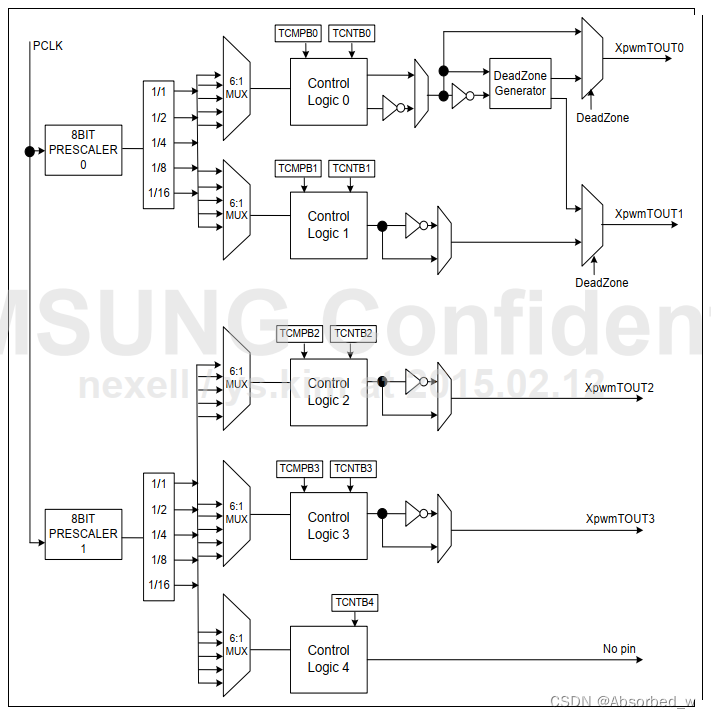

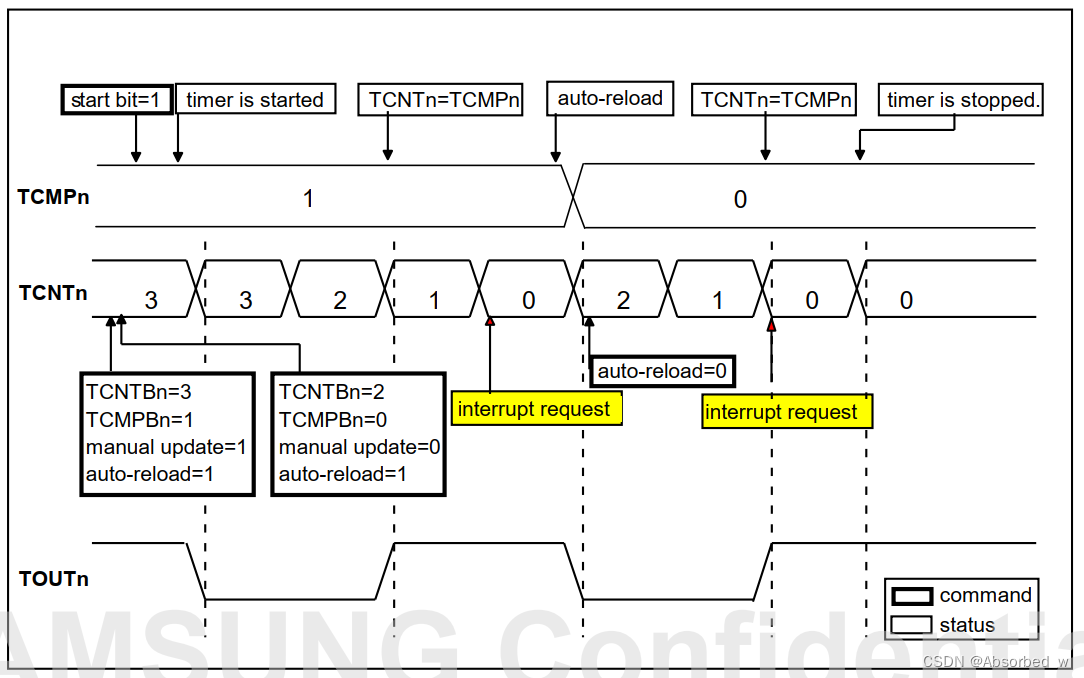

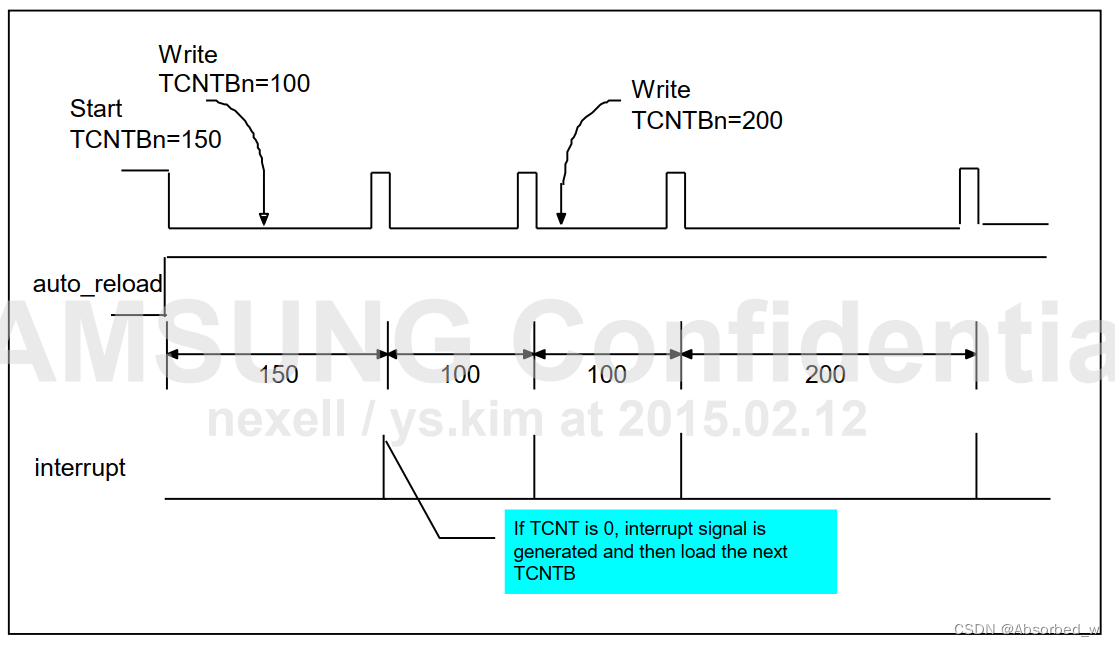

1.4.12 PWM

- 3通道PWM控制器

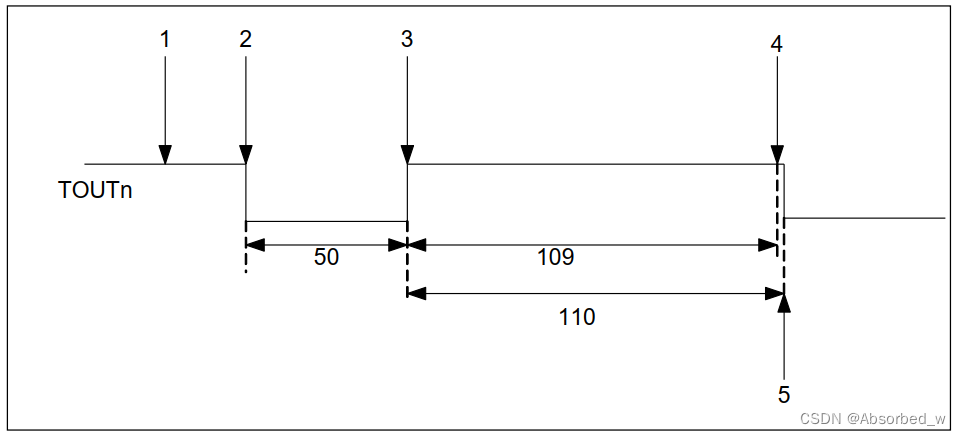

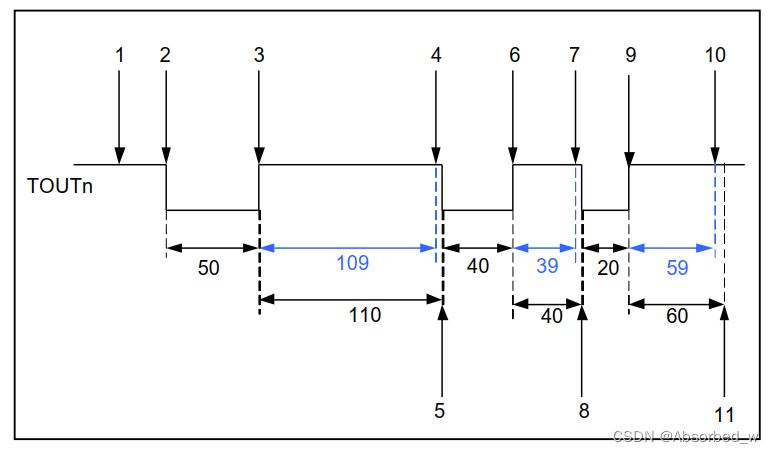

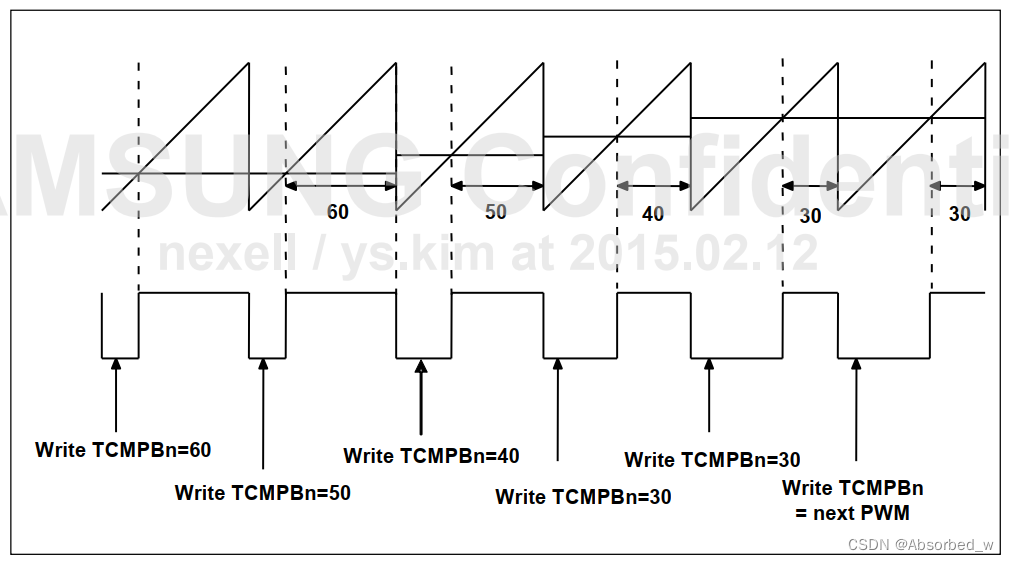

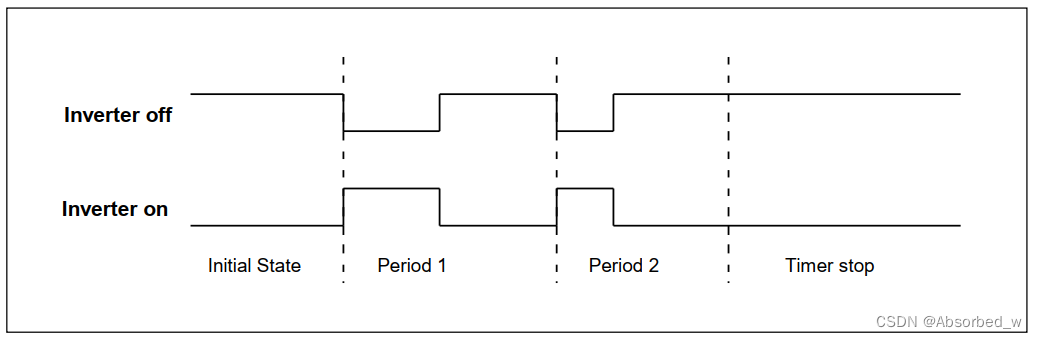

- 五个32位计时器

- 两个8位时钟预分频器,为PCLK提供第一层分频,五个时钟分频器和多路复用器,为预分频器时钟提供第二层分频,两个外部时钟

- 每个PWM通道的可编程时钟选择逻辑

- 四个独立的PWM通道,具有可编程的占空比控制和极性

- 静态配置:PWM停止

- 动态配置:PWM运行

- 支持自动重装模式和单次脉冲模式

- 支持两个外部输入启动PWM

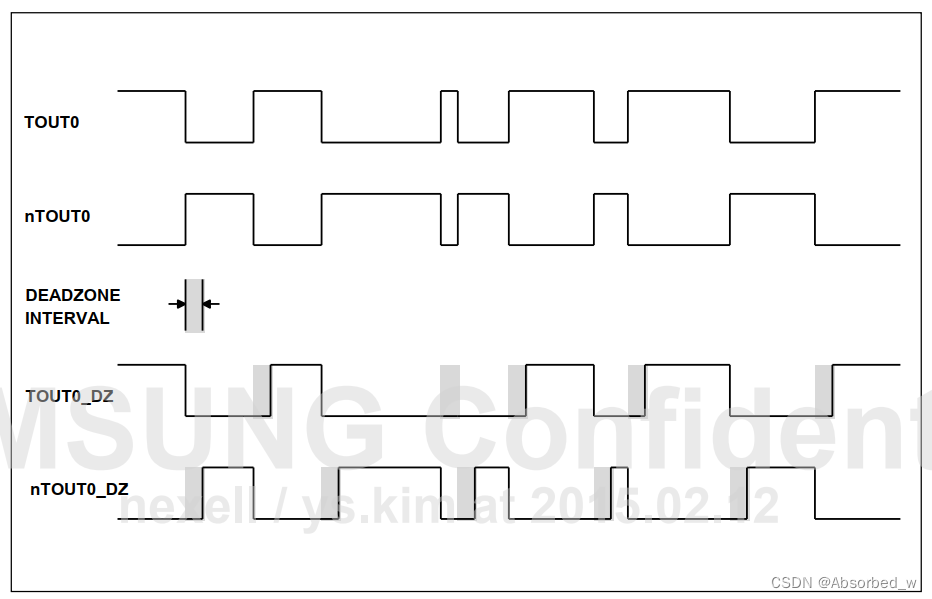

- 两个PWM输出的死区生成器

- 支持DMA传输

- 可选的脉冲或电平中断生成

- PWM有两种操作模式:

- 自动重装模式

- 基于编程的占空比和极性,连续生成PWM脉冲

- 单次脉冲模式

- 基于编程的占空比和极性,只生成一个PWM脉冲

- 自动重装模式

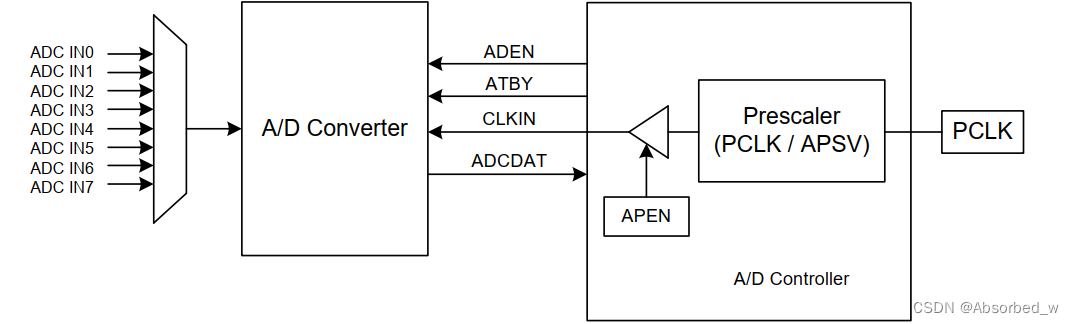

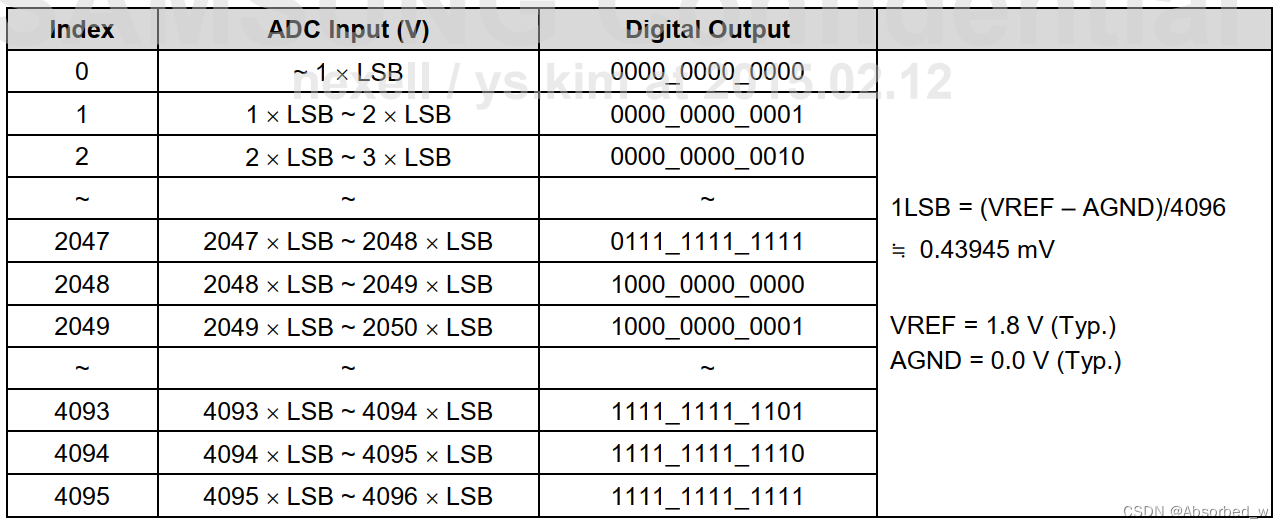

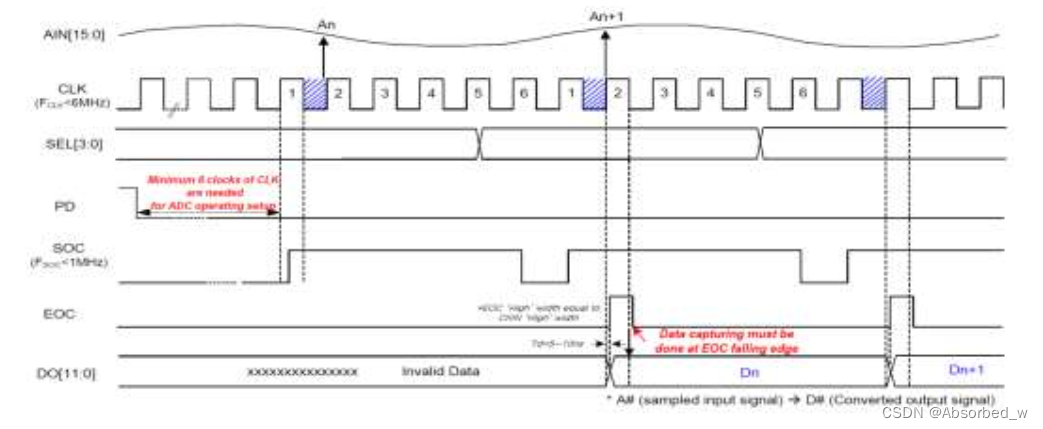

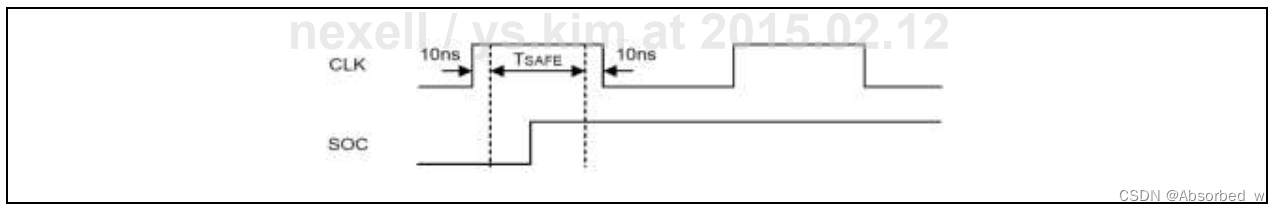

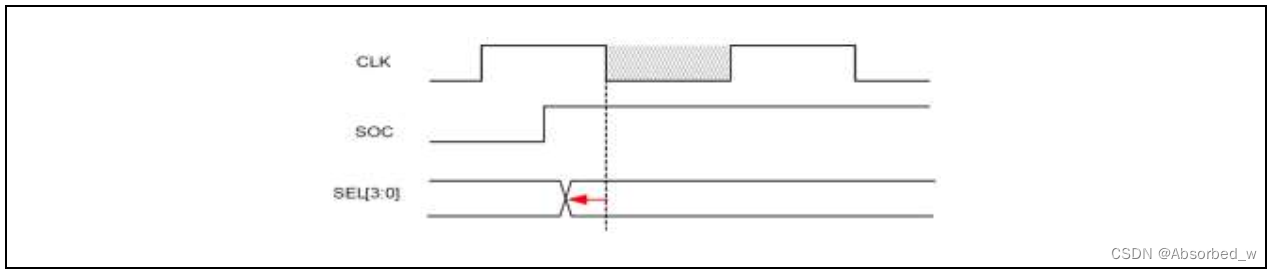

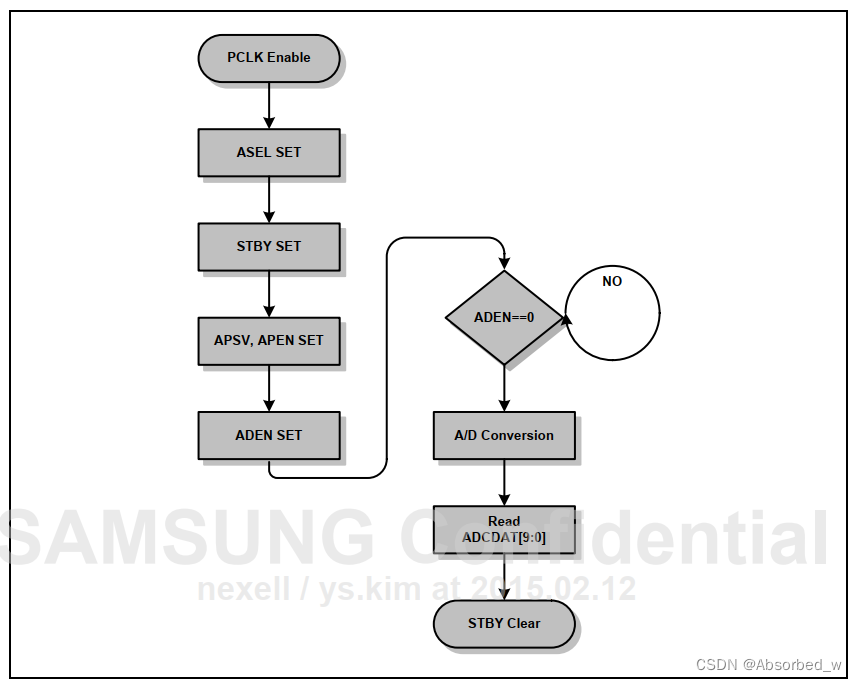

1.4.13 ADC

- 8通道模拟输入端口

- 支持以下功能

- 分辨率:12位

- 转换率:1 MSPS

- 功耗

- 正常操作模式下,典型功耗1.0 mW(Fs = 1 MSPS)

- 断电模式下,典型功耗0.005 mW

- 输入范围:0到AVDD18

- 输入频率:最高可达100 kHz

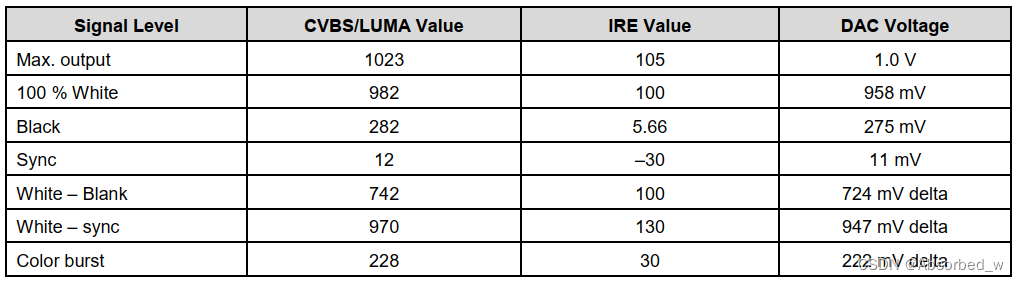

1.4.14 DAC

- 1通道10位电流输出DAC,用于CVBS输出

- 最大更新率54 MHz

- 内部电压参考

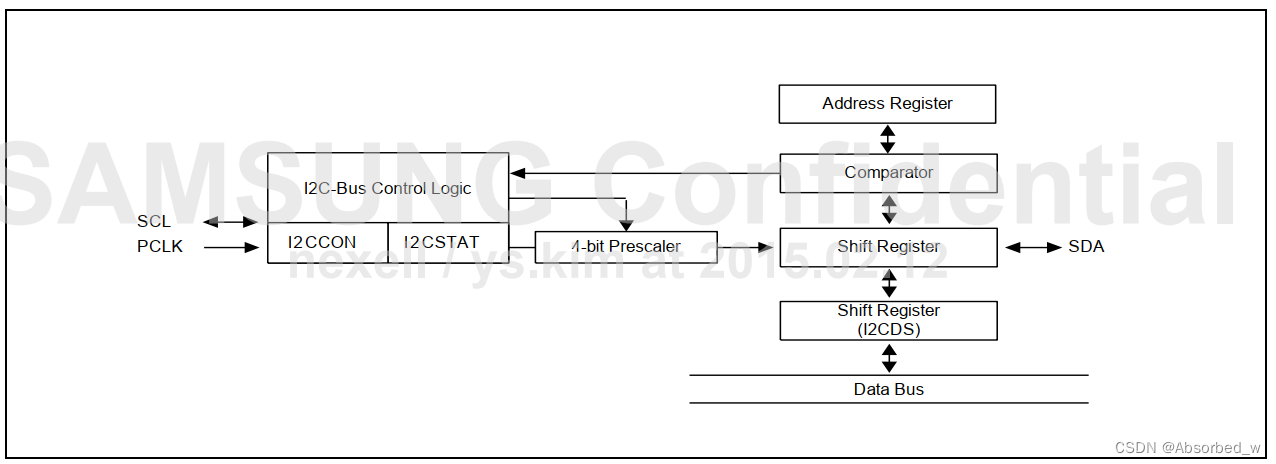

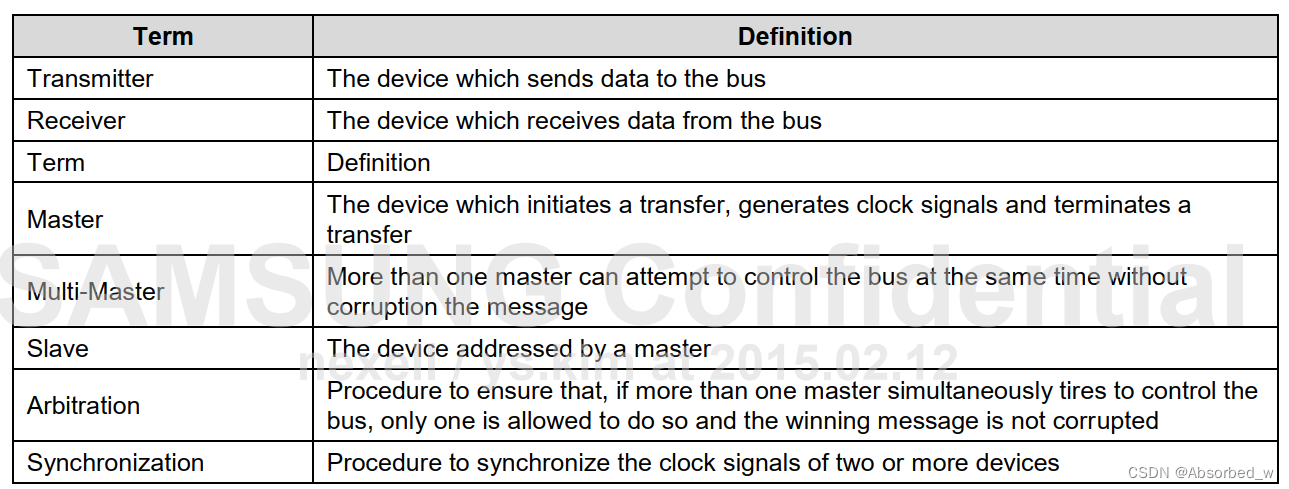

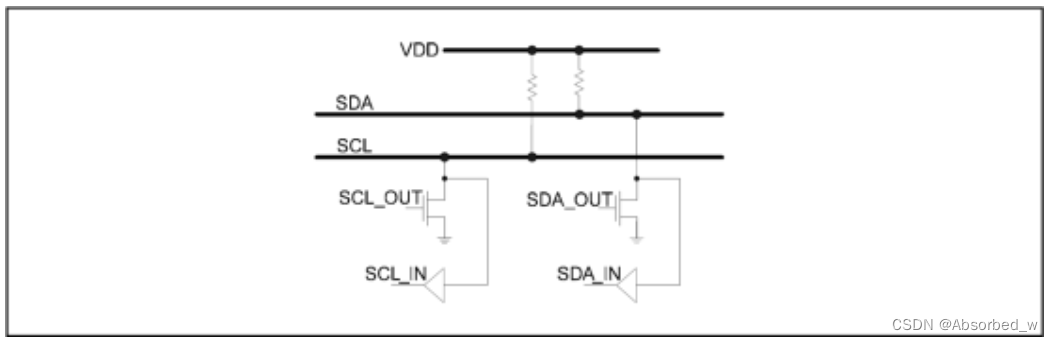

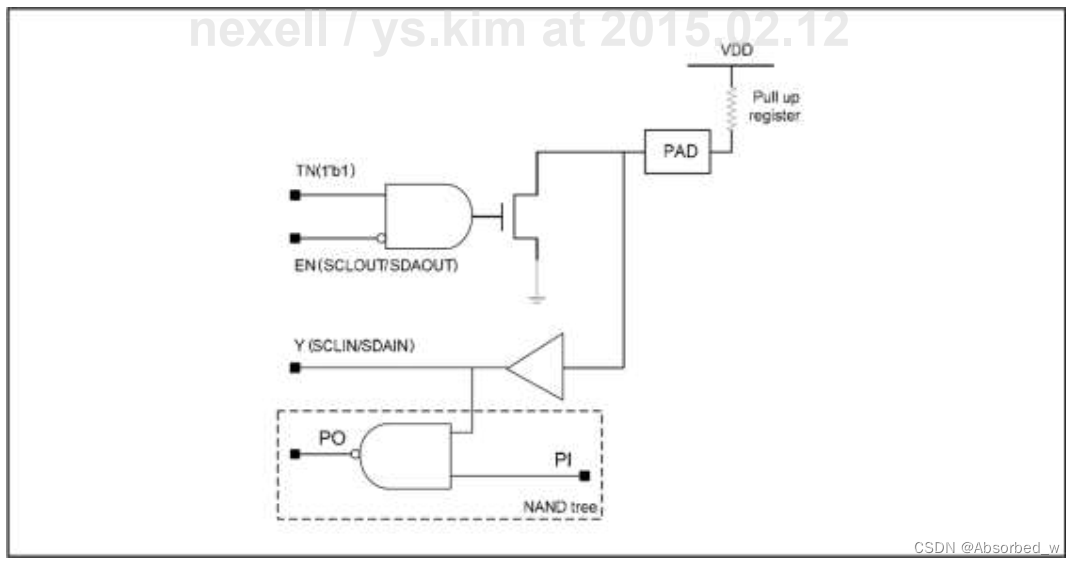

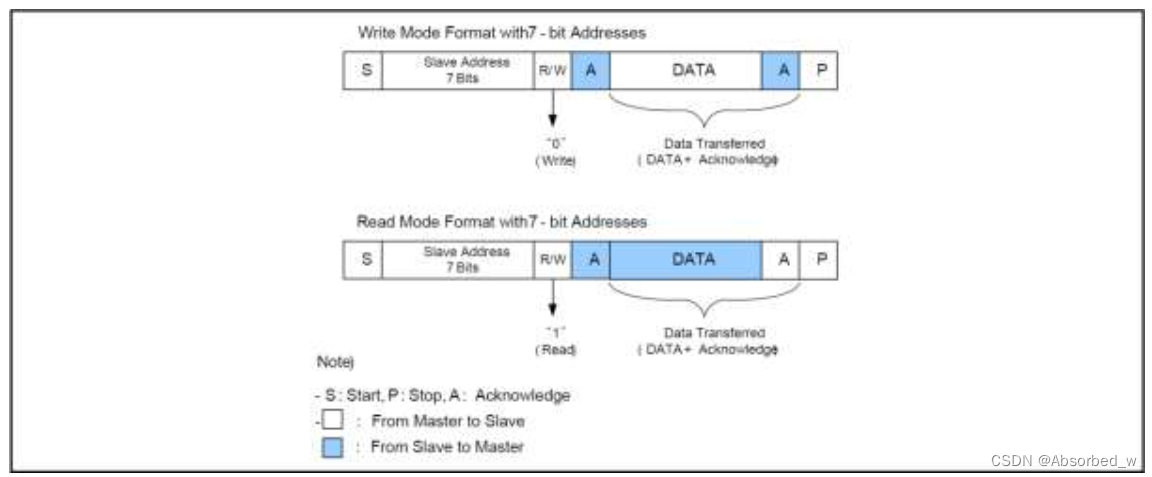

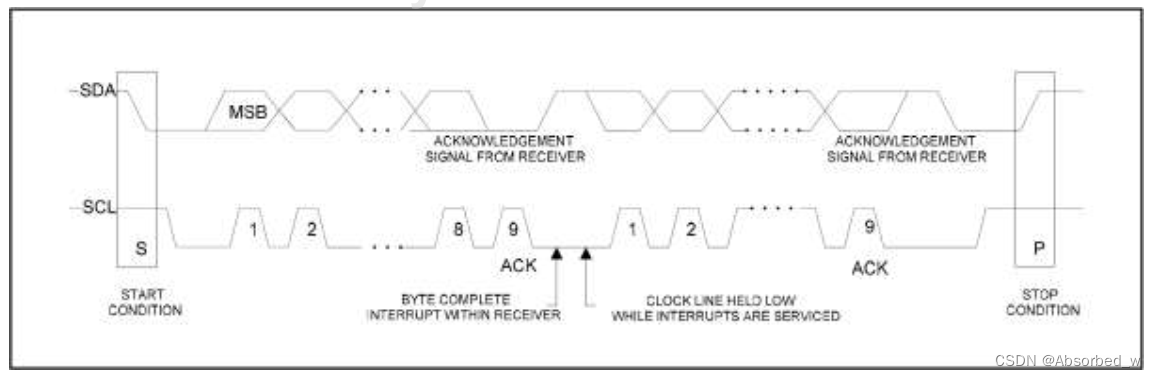

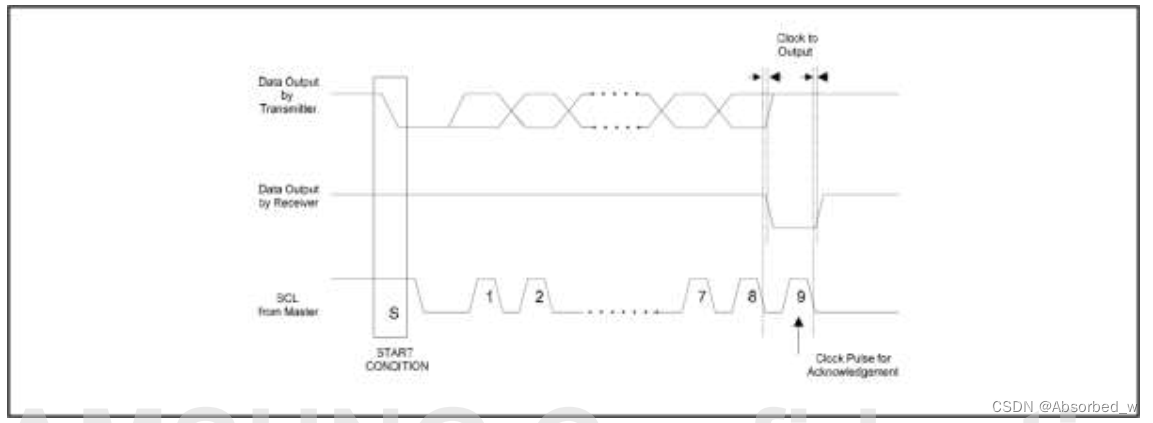

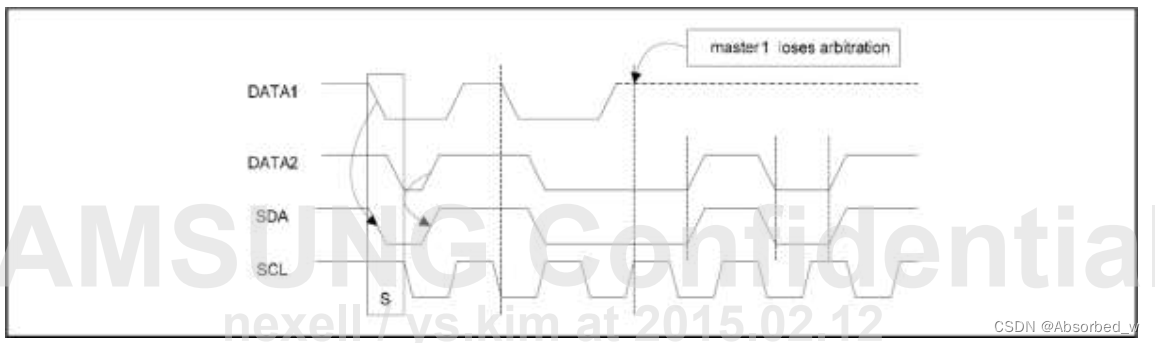

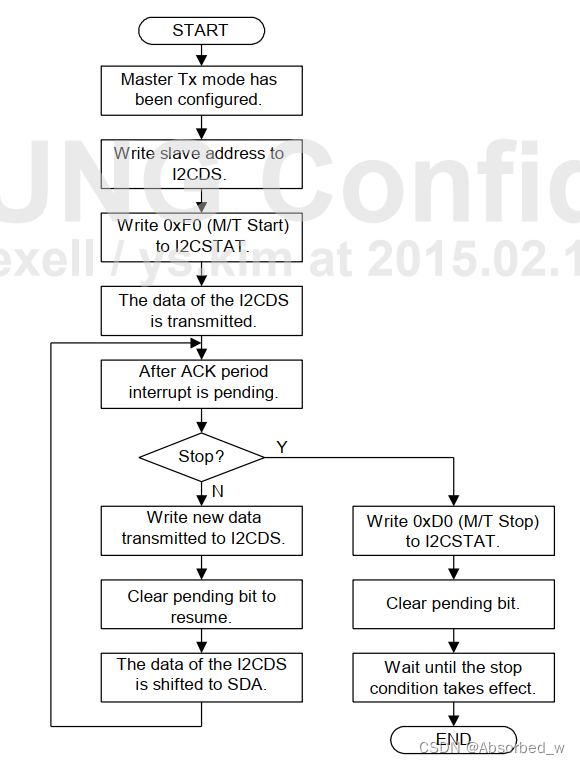

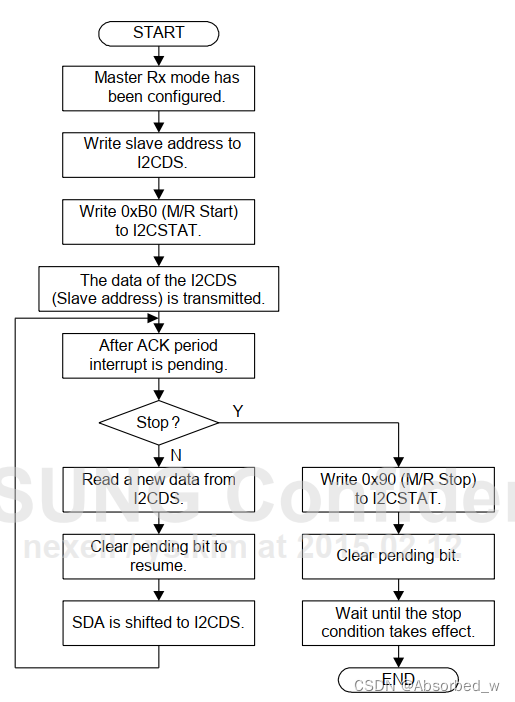

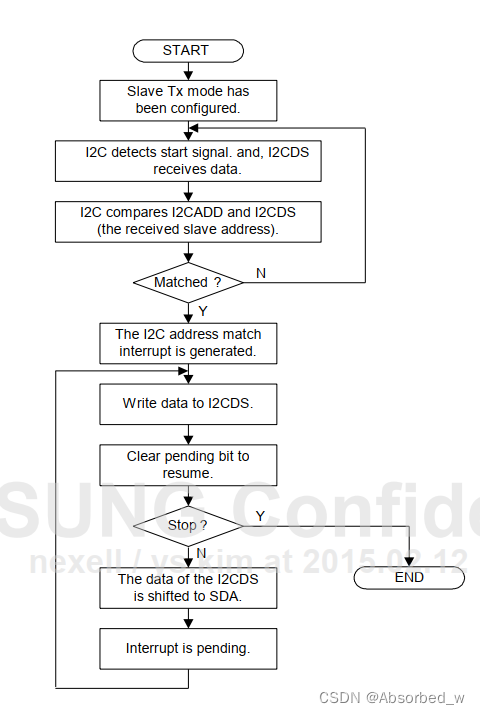

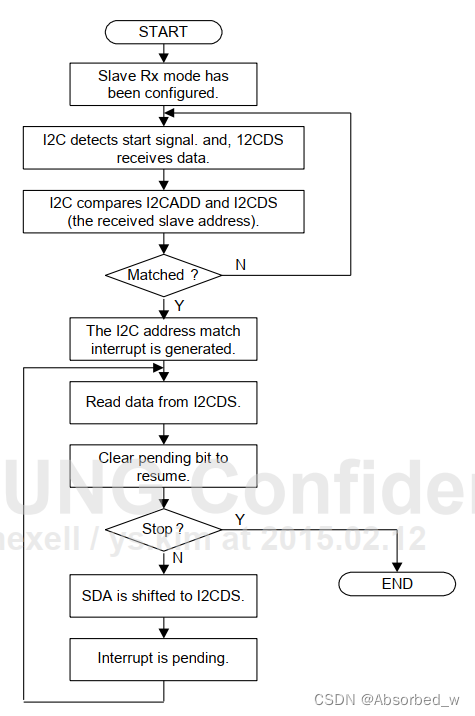

1.4.15 I2C

- 3通道I2C总线控制器

- 总线上连接的每个设备通过唯一地址由软件可寻址,并且始终存在简单的主/从关系;主设备可以作为主发送器或主接收器操作

- 在标准模式下,串行、8位定向、双向数据传输速度最高可达100 kbit/s,在快速模式下,最高可达400 kbit/s

- 可以连接到同一总线的IC数量仅受最大总线电容400 pF的限制

- 不支持重复启动和提前终止功能

- 不支持高速模式、组合格式、10位地址

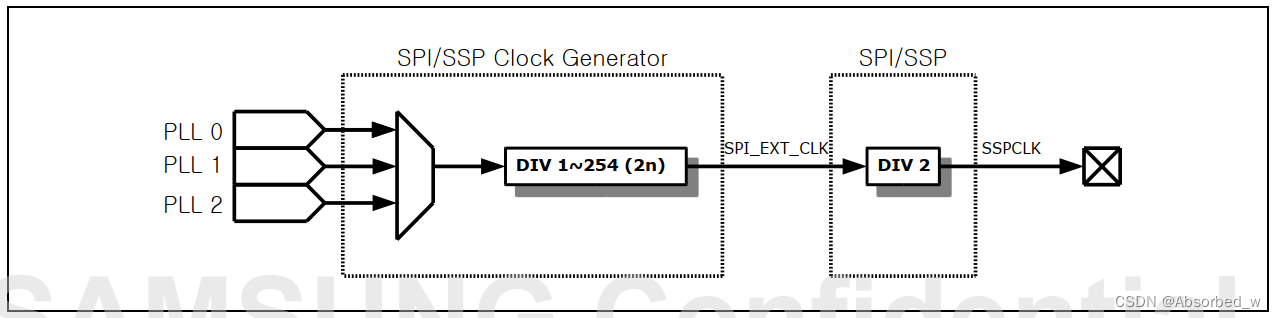

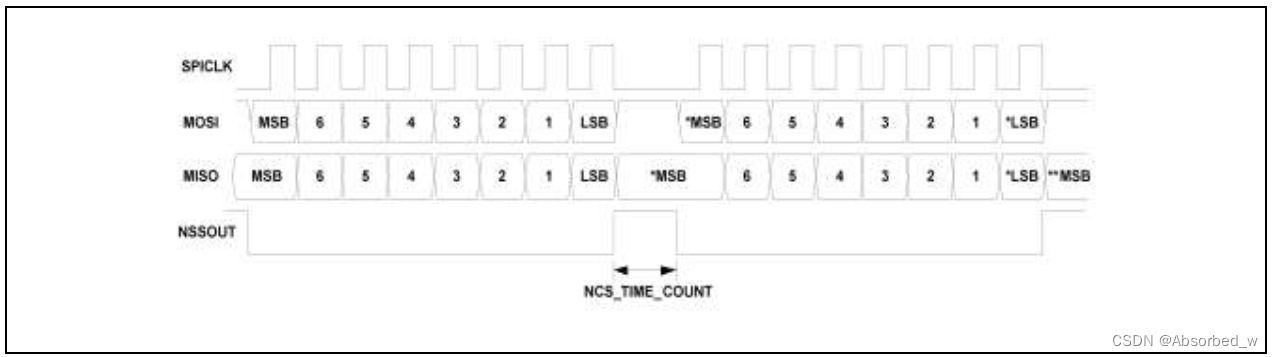

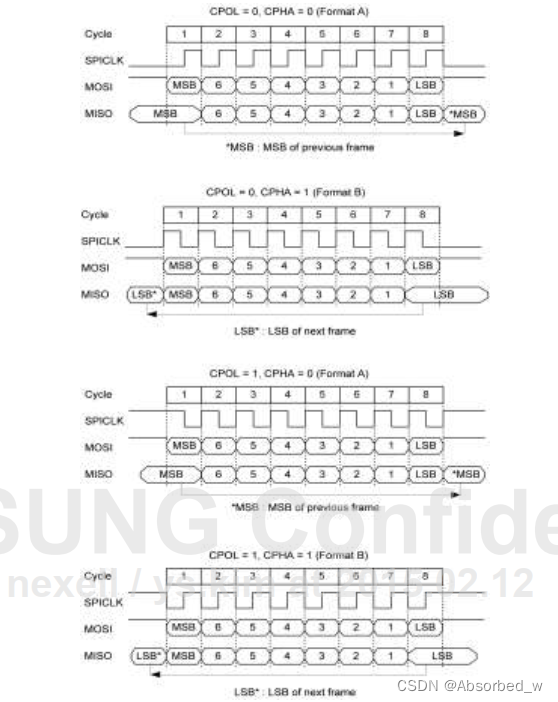

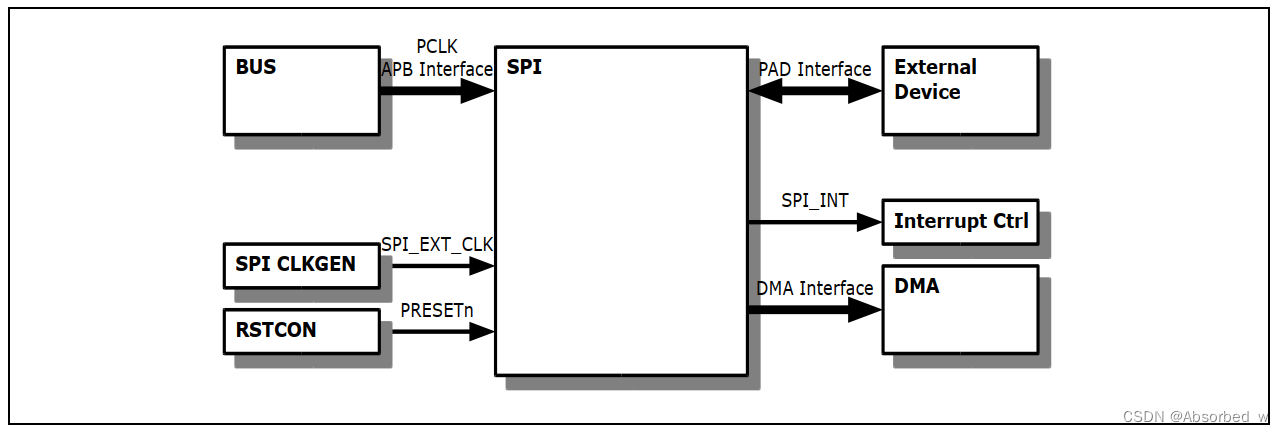

1.4.16 SPI/SSP

- 3通道SPI控制器

- 主设备或从设备操作

- 可编程时钟比特率和预分频器

- 分开的传输和接收先入先出内存缓冲区,16位宽,8位深

- 可编程的接口操作选择:SPI、Microwire或TI同步串行

- SPI协议、SSP协议、Microwire协议

- DMA请求服务传输和接收FIFO

- 通知系统接收FIFO溢出

- 在空闲期后接收FIFO中有数据时通知系统

- 只支持DMA突发长度4

- 最大SSP CLKGEN频率为100 MHz

- SSP接收超时时间:64周期的SSP CLKGEN时钟

- 最大操作频率

- 主模式:50 MHz(接收数据为20 MHz)

- 从模式:8 MHz

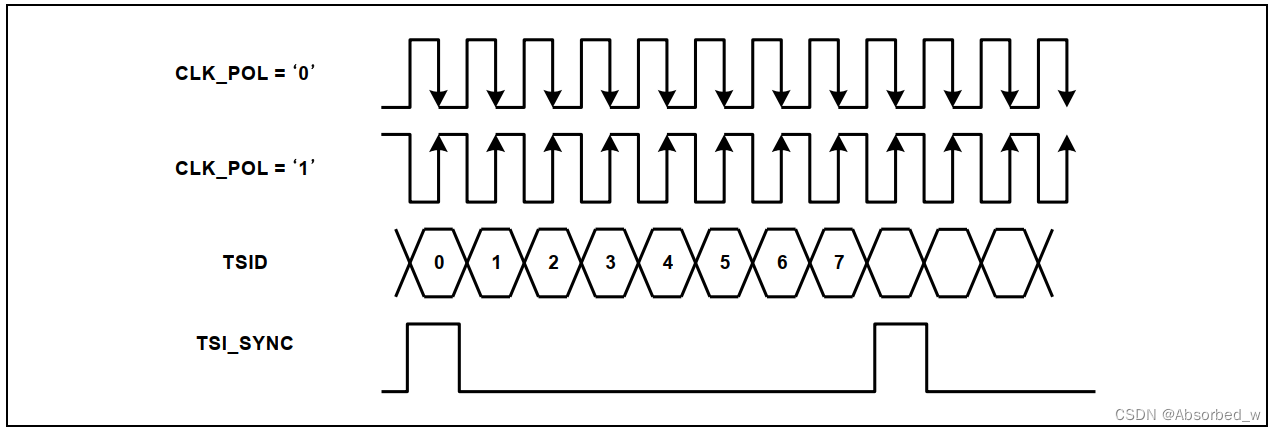

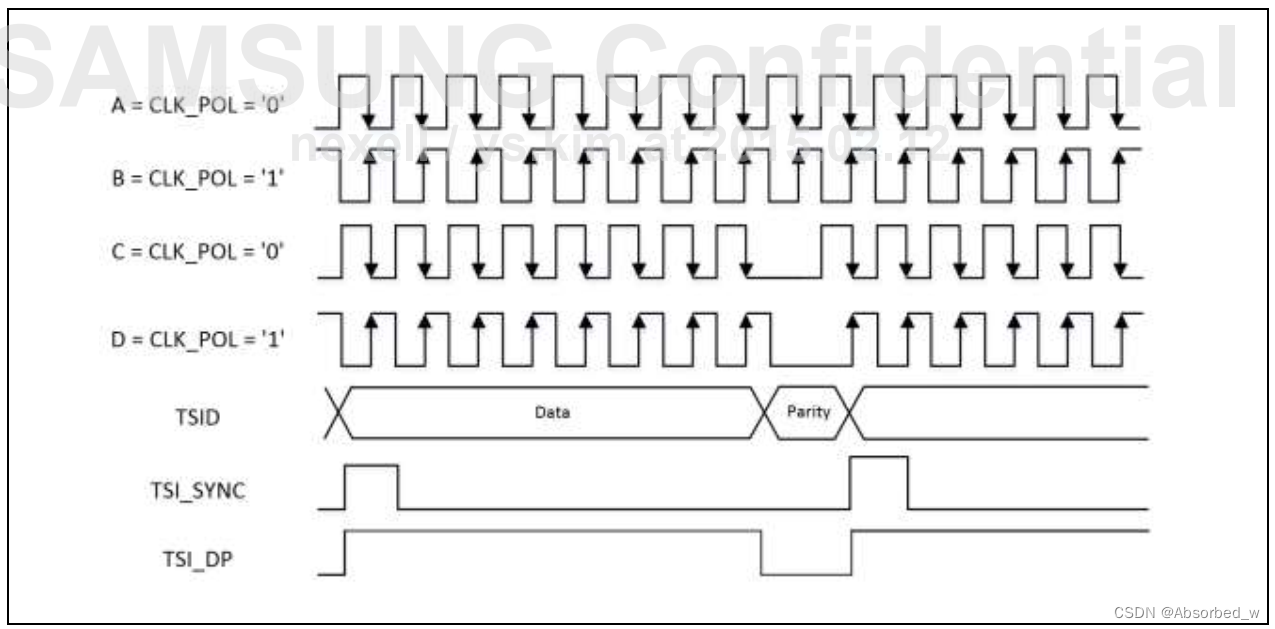

1.4.17 MPEG-TS

- 支持并行MPEG-TS接口

- 支持硬件MPEG-TS解析器用于Set-top和IPTV

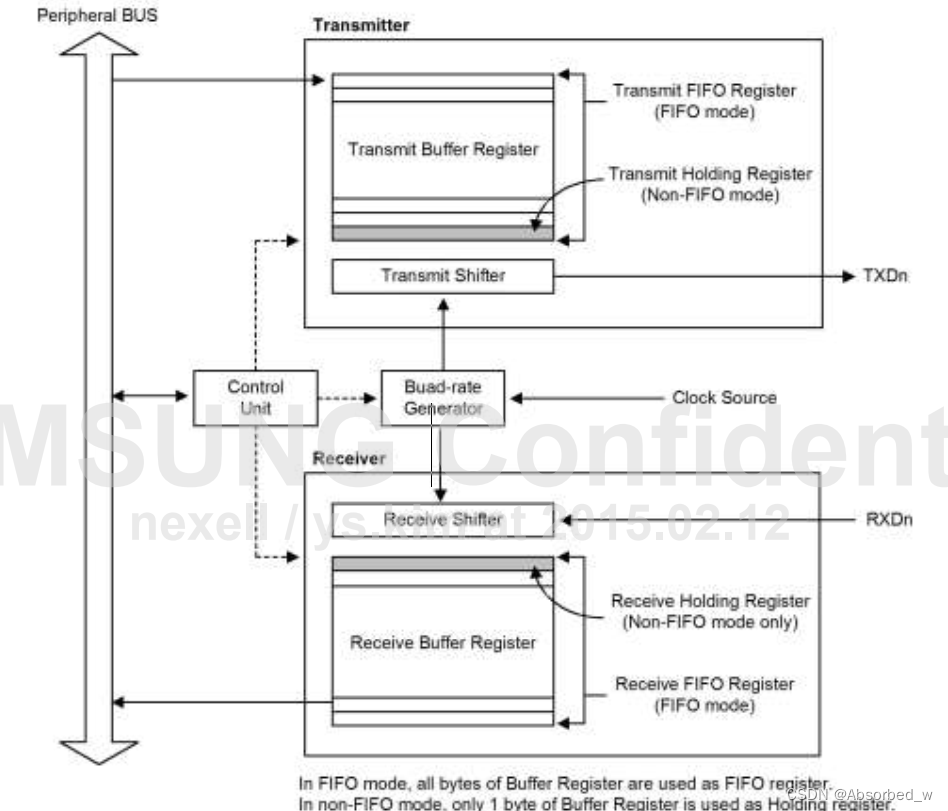

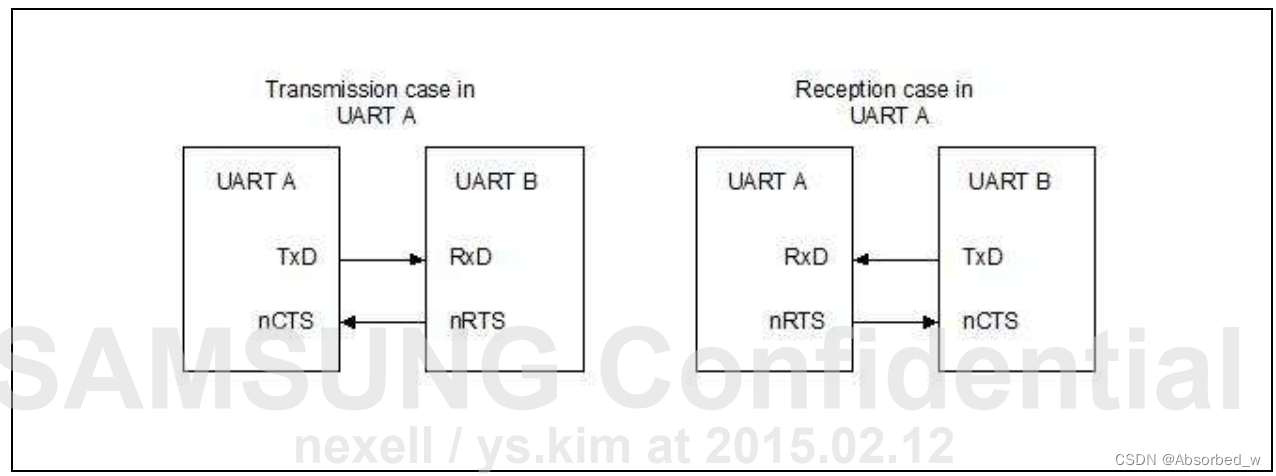

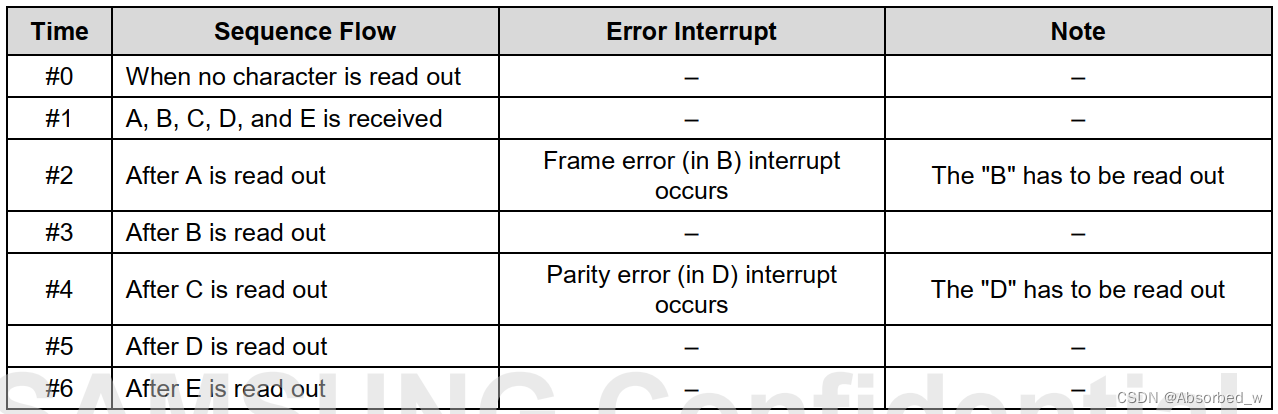

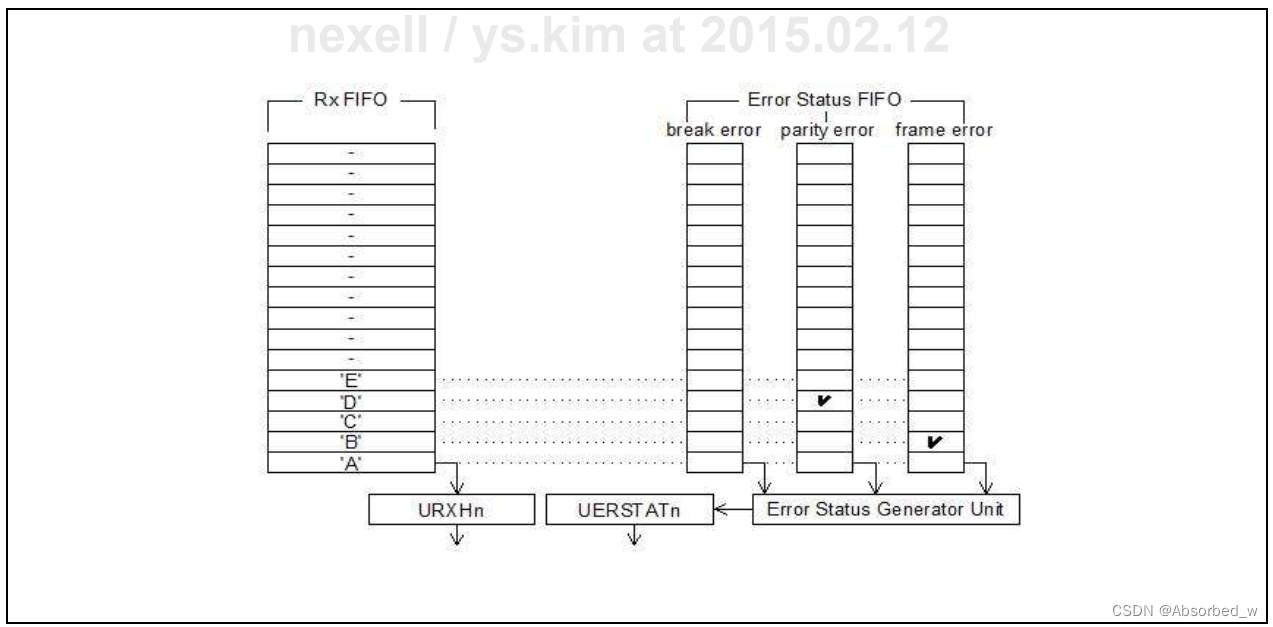

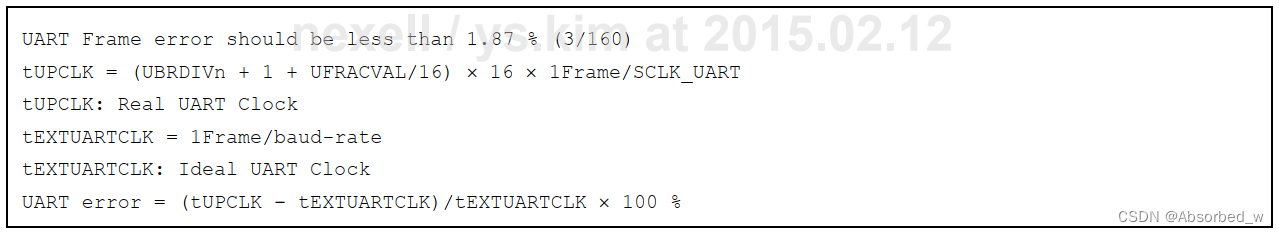

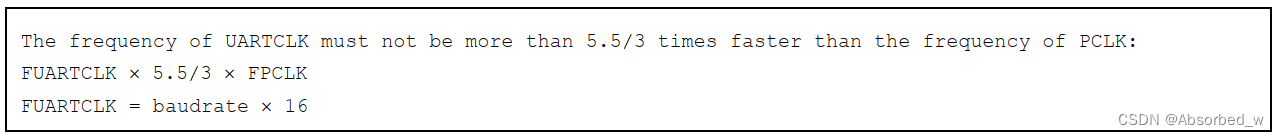

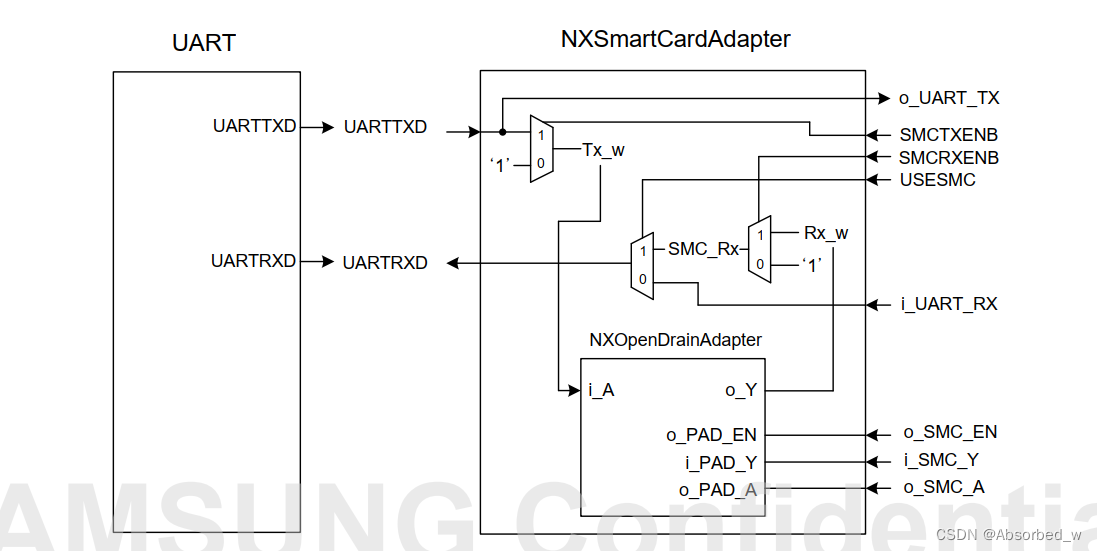

1.4.18 UART及ISO7816 SIM卡接口

- 6通道UART控制器

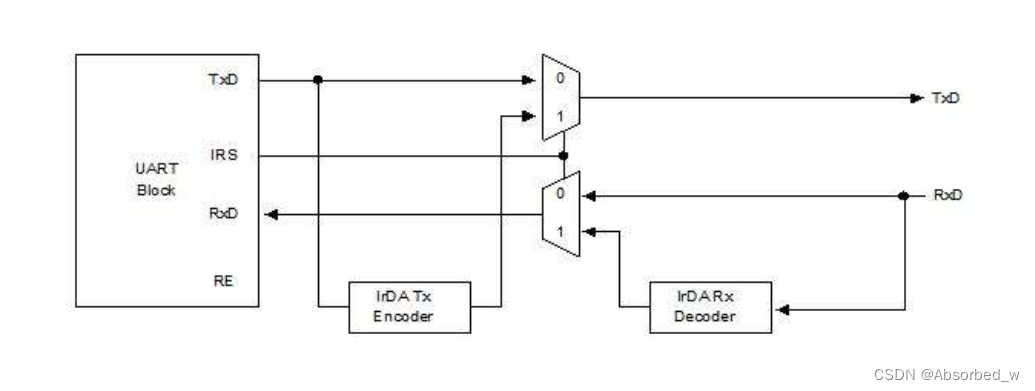

- 可编程使用UART或IrDA SIR输入/输出

- 独立的32×8发送和32×12接收FIFO缓冲区,减少CPU中断

- 可编程FIFO禁用,深度为1字节

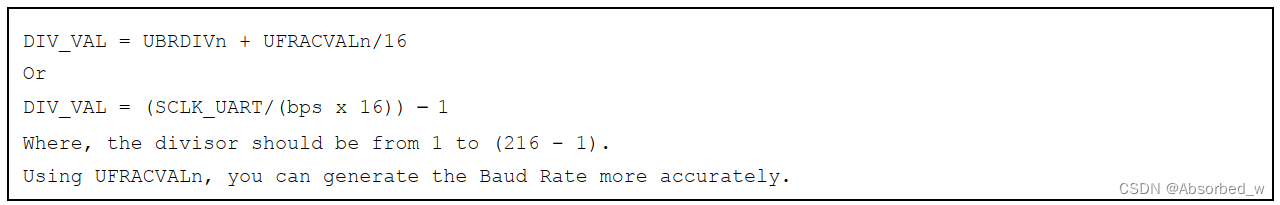

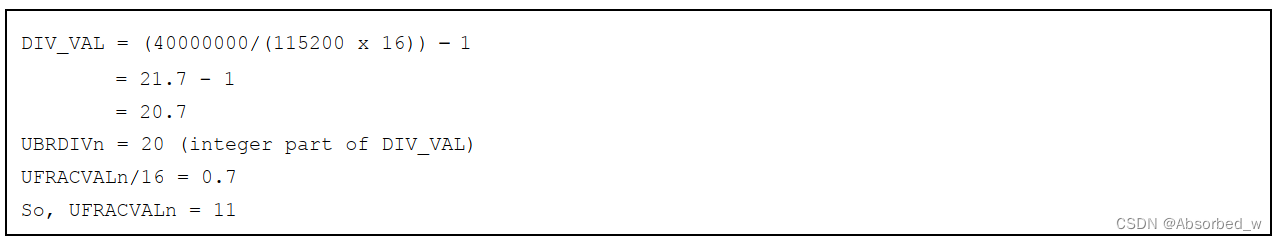

- 可编程波特率发生器,使参考时钟的分频范围为(1×16)到(65535×16),生成内部×16时钟。除数可以是分数,使您可以使用频率大于3.6864 MHz的任何时钟作为参考时钟

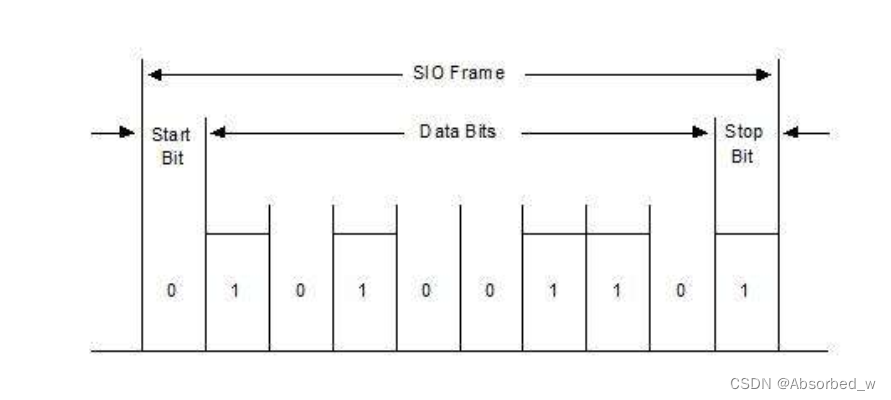

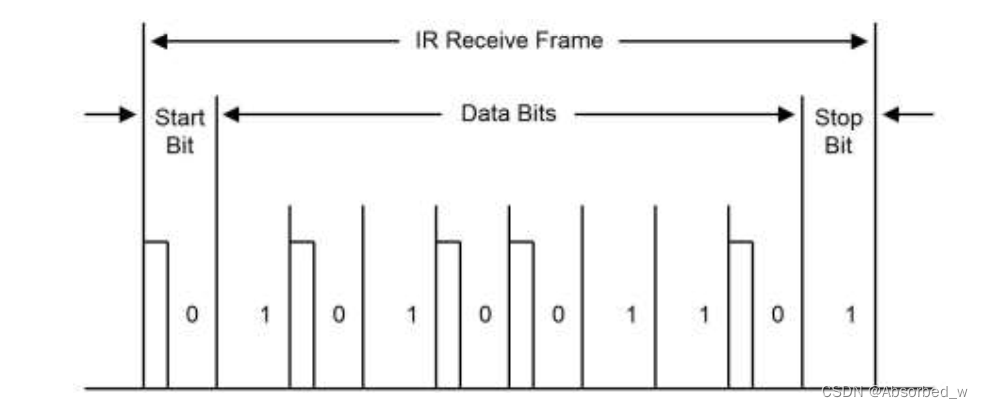

- 标准异步通信位(起始位、停止位和奇偶校验位),在传输前添加,在接收时移除

- 传输FIFO、接收FIFO、接收超时、调制解调器状态和错误条件中断的独立屏蔽

- 支持直接内存访问(DMA)

- 错误起始位检测

- 线路中断生成和检测

- 支持调制解调器控制功能CTS、DCD、DSR、RTS、DTR和RI

- 可编程硬件流控制

- 完全可编程的串行接口特性:

- 数据位数可以是5、6、7或8位

- 奇偶校验位生成和检测可以是偶数、奇数、粘性或无校验

- 生成1或2个停止位

- 波特率生成,最高为UARTCLK/16

- IrDA SIR ENDEC模块提供:

- 可编程使用IrDA SIR或UART输入/输出

- 支持高达115200 bps半双工数据率的IrDA SIR ENDEC功能

- 支持正常的3/16和低功耗(1.41-2.23 μs)位持续时间

- 可编程分频UARTCLK参考时钟,生成适合低功耗IrDA模式的位持续时间

- 识别寄存器,可用于操作系统自动配置

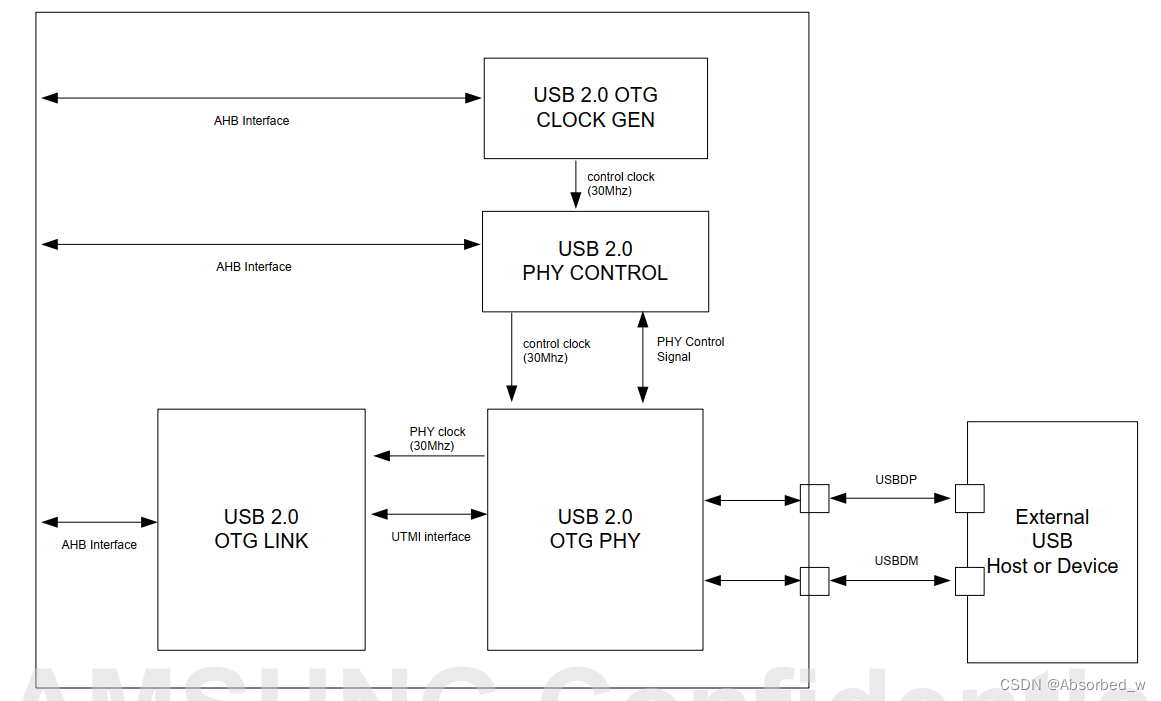

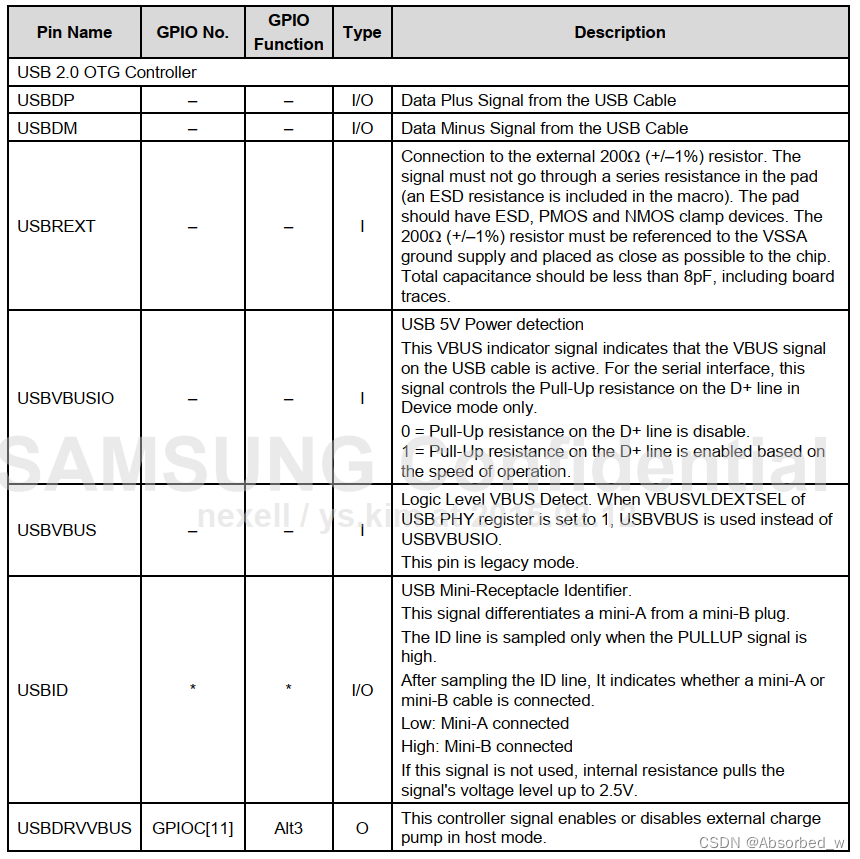

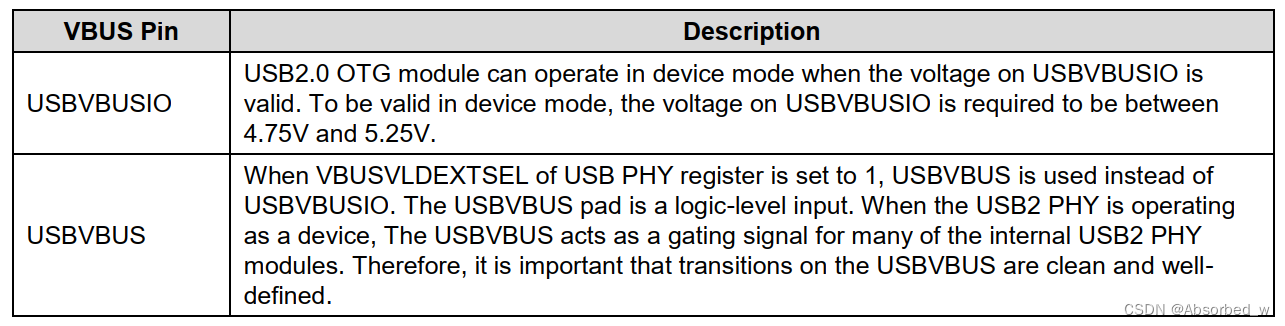

1.4.19 USB

- 1通道USB 2.0主机和1通道USB2.0 HSIC主机

- 完全符合通用串行总线规范,修订版1.1,通用串行总线增强型主控制器接口规范,修订版2.0,以及USB开放主控制器接口规范,版本1.0a。控制器通过EHCI主控制器支持高速、480 Mbps传输(比USB 1.1全速模式快40倍),以及通过一个或多个集成的OHCI主控制器支持全速和低速传输

- 在USB 2.0物理接口,控制器提供以下功能:

- UTMI:UTMI+ 3级,修订版1.0

- 高速芯片间(HSIC),版本1.0

- 支持ping和分离事务

- UTMI/UTMI+ PHY接口时钟支持30 MHz操作,适用于16位接口或60 MHz操作,适用于8位接口

- 使用绑带引脚选择每个端口的UTMI+或HSIC接口。在异构模式下,只支持8位接口(60 MHz)

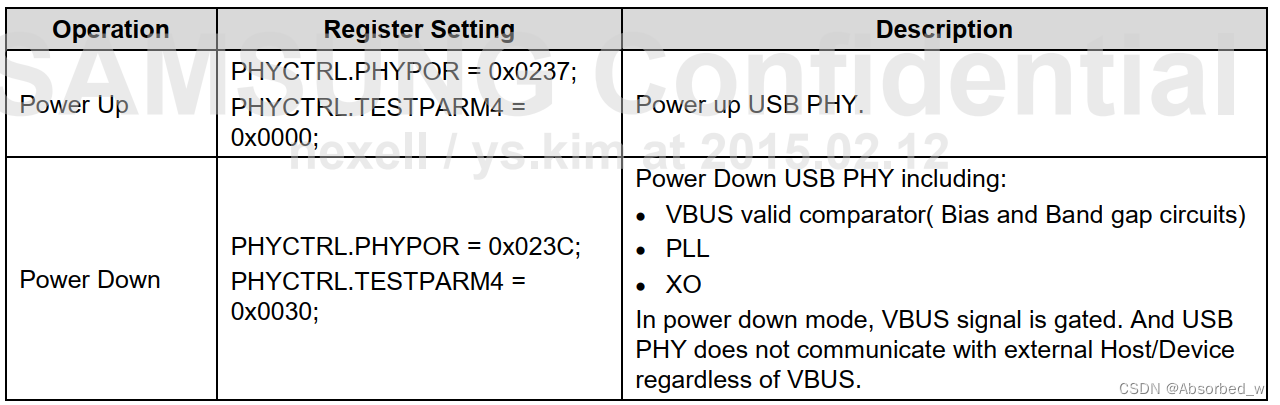

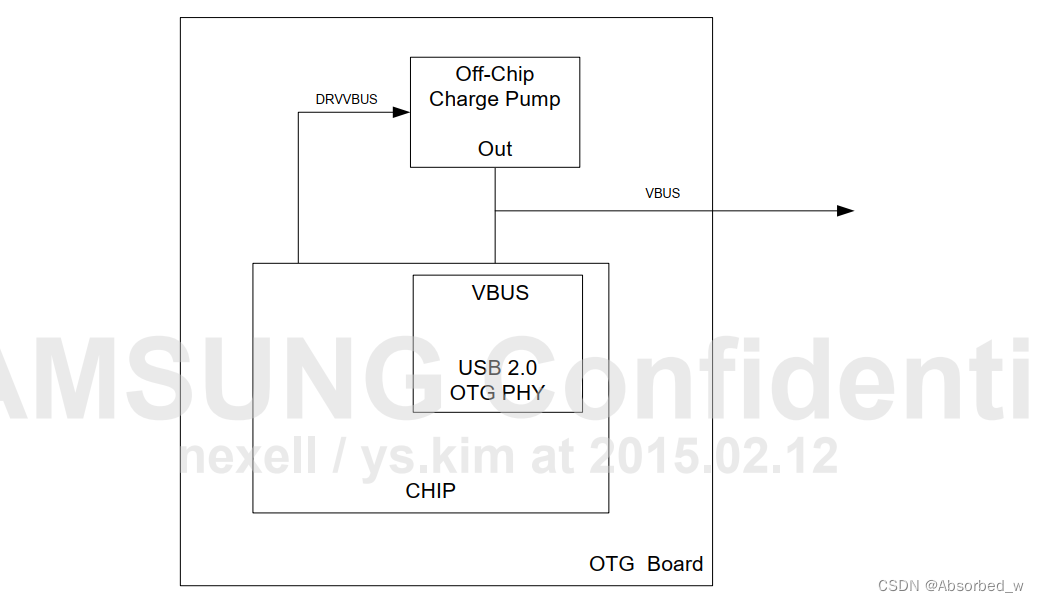

- 1通道USB 2.0 OTG控制器

- 支持设备和主机功能,完全符合USB 2.0规范补充,修订版1.3a和修订版2.0。也可以配置为仅主机或仅设备控制器,完全符合USB 2.0规范

- 符合USB 2.0规范补充(修订版1.3)

- 符合USB 2.0规范补充(修订版2.0)

- 软件可配置为OTG1.3和OTG2.0操作模式

- 支持以下速度:

- 高速(HS,480 Mbps)

- 全速(FS,12 Mbps)

- 低速(LS,1.5 Mbps)

- 提供多种低功耗操作选项

- 多种DMA/非DMA模式访问支持

- 多种MAC-PHY接口支持

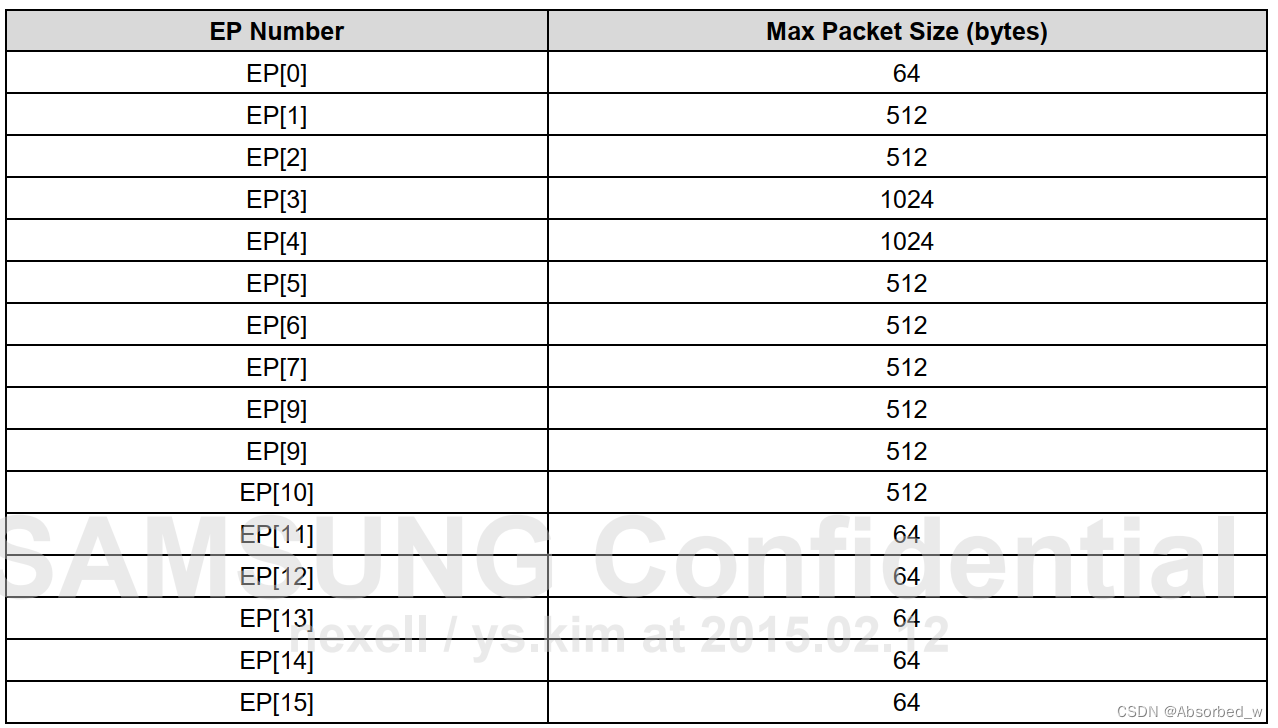

- 支持16个双向端点,包括控制端点0

- 支持会话请求协议(SRP)

- 支持主机协商协议(HNP)

- 支持多达16个主机通道。在主机模式下,当要支持的设备端点数量超过主机通道数量时,软件可以重新编程通道,以支持多达127个设备,每个设备有32个端点(IN + OUT),最大支持4,064个端点

- 包含自动ping功能

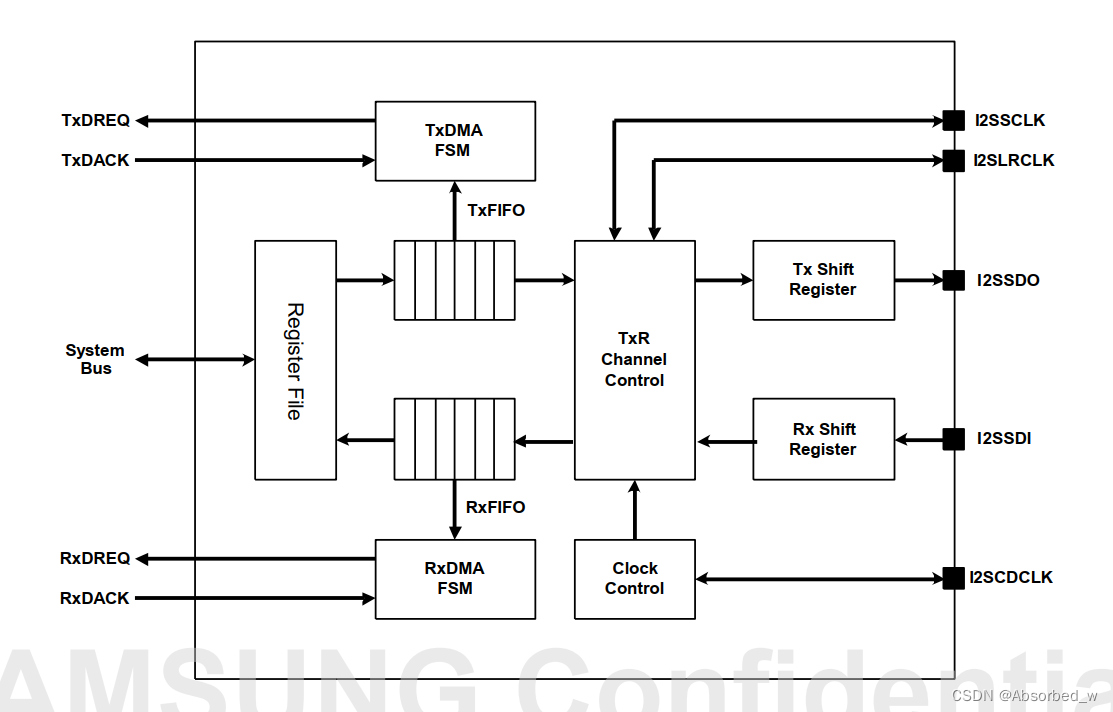

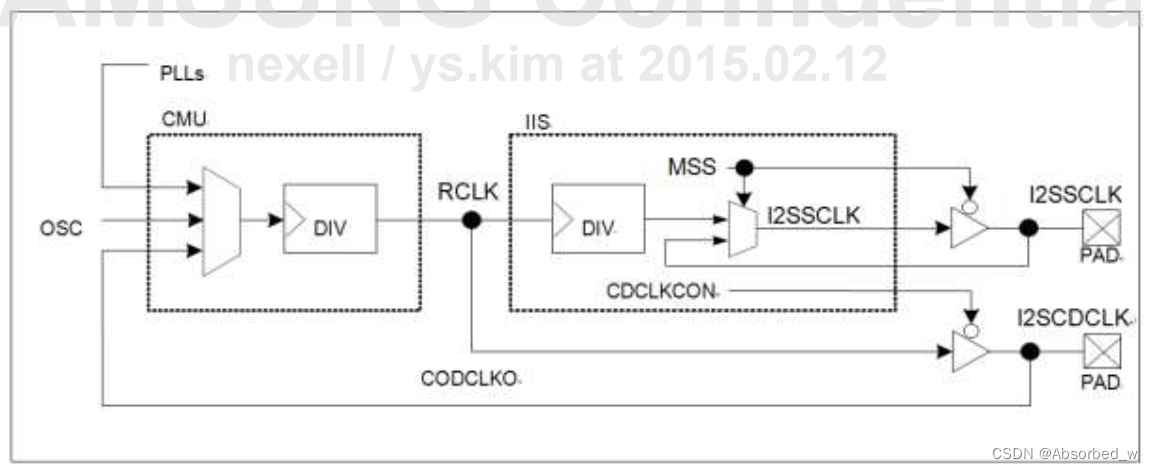

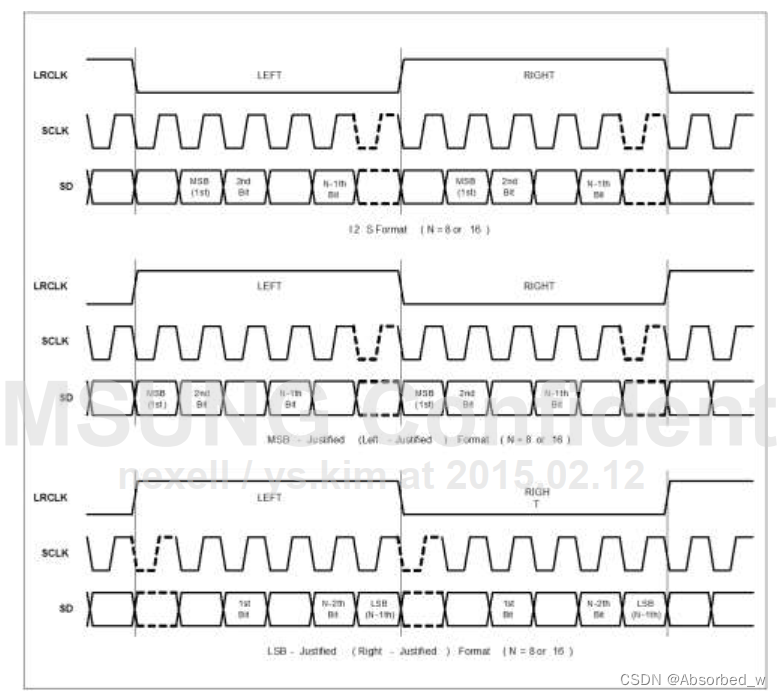

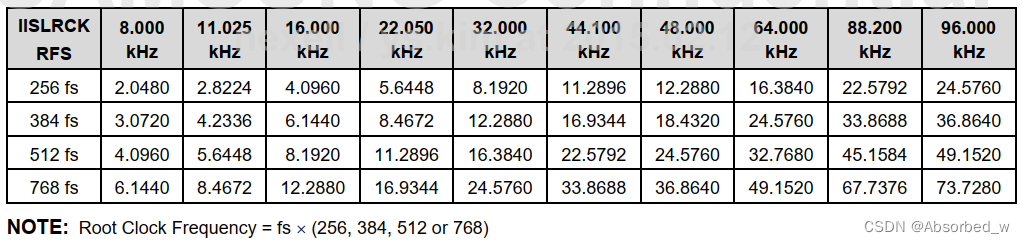

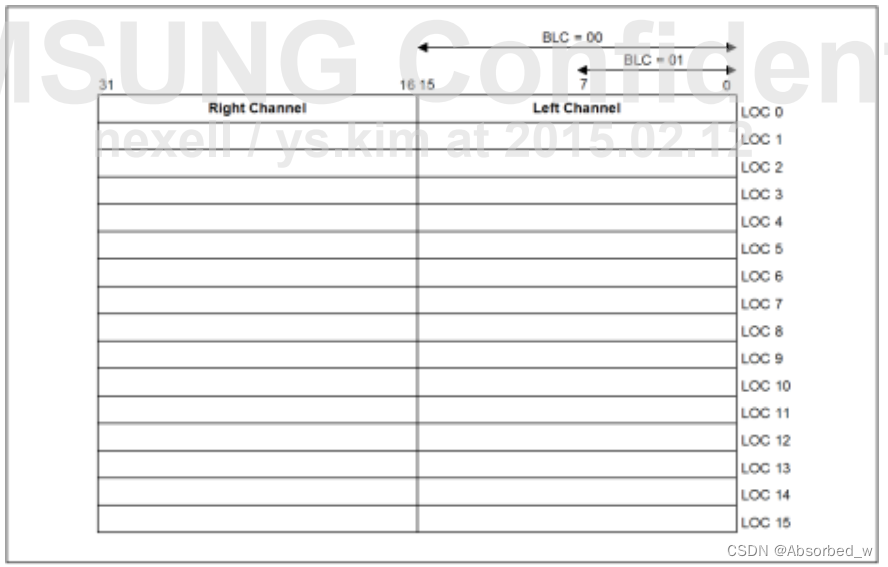

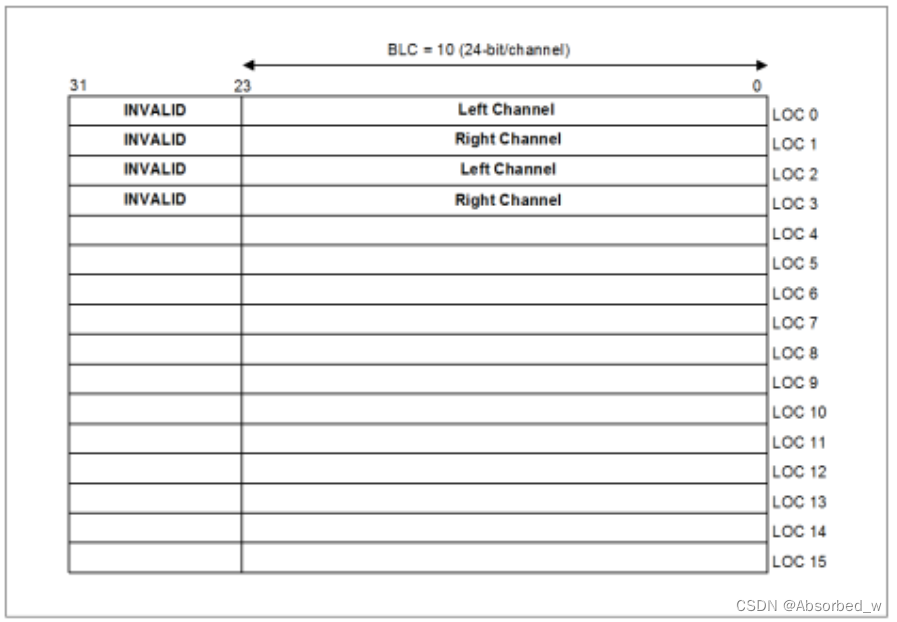

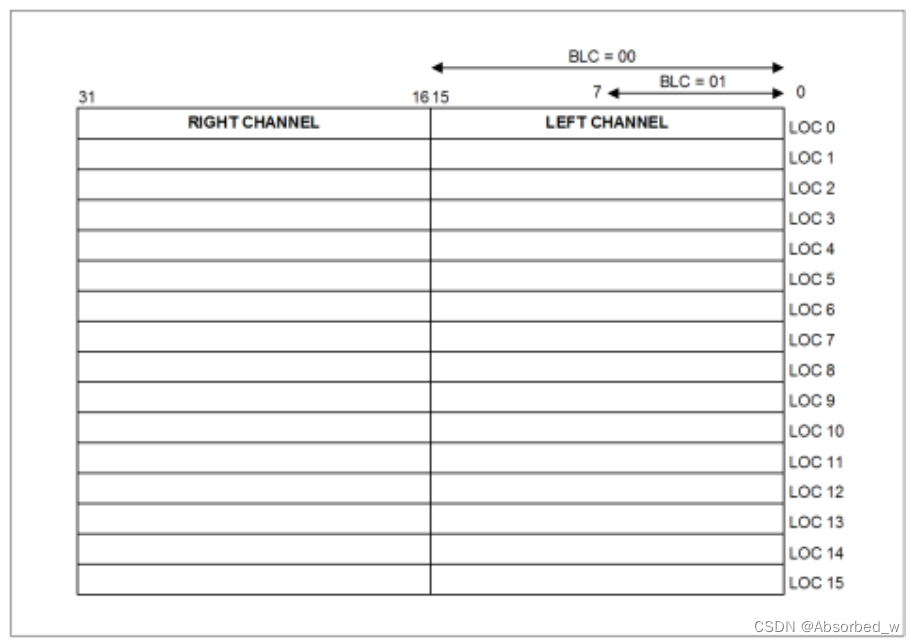

1.4.20 I2S

- 3通道I2S控制器用于5.1声道音频输出

- 16位/24位主设备和从设备模式

- 支持多种接口模式

- I2S、左对齐、右对齐、DSP模式

- 支持TDM模式用于数字MIC接口

- 支持SPDIF接收/发送

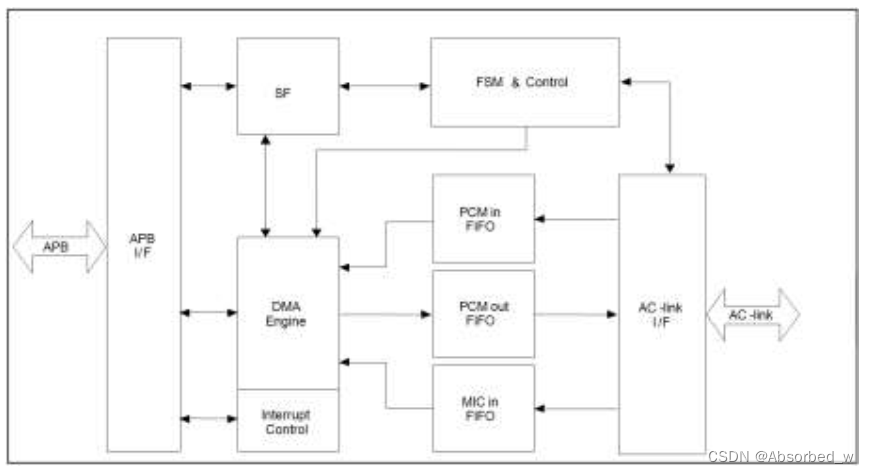

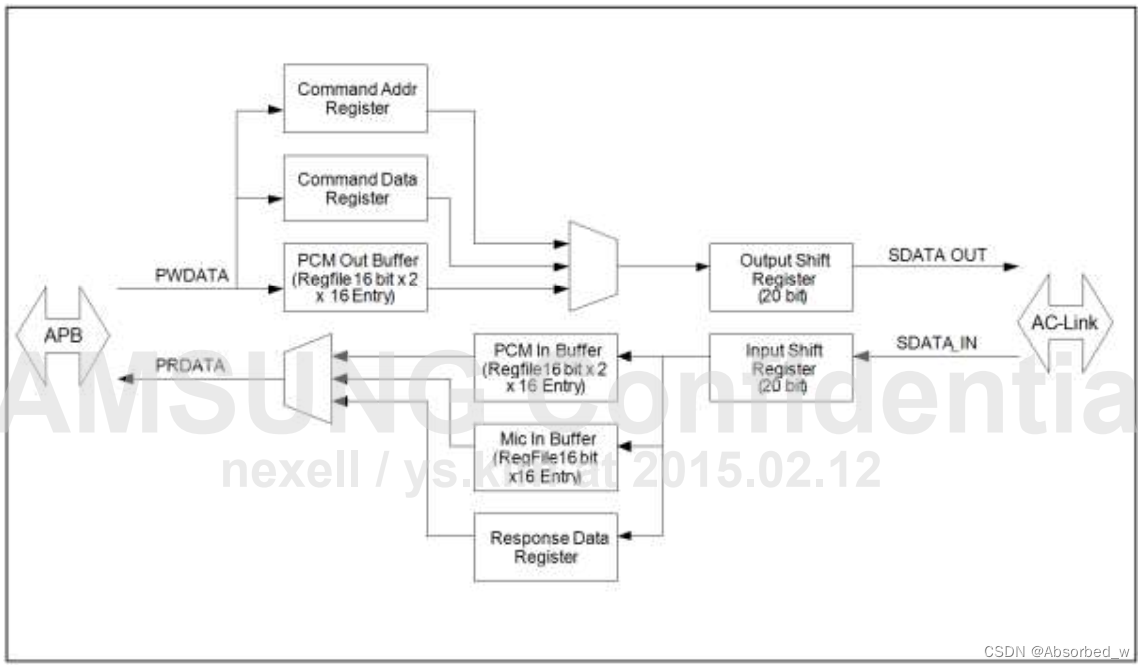

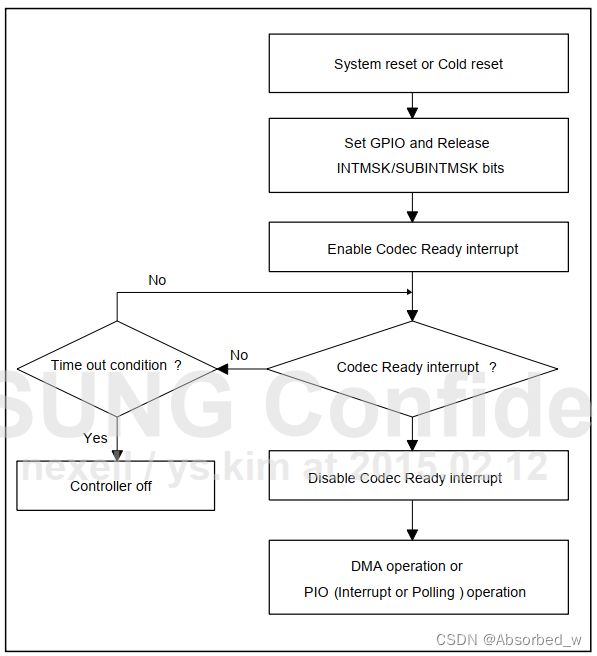

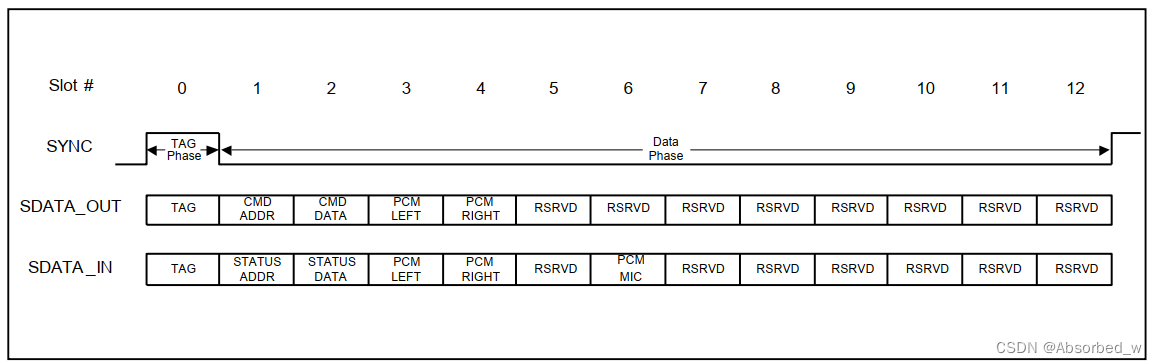

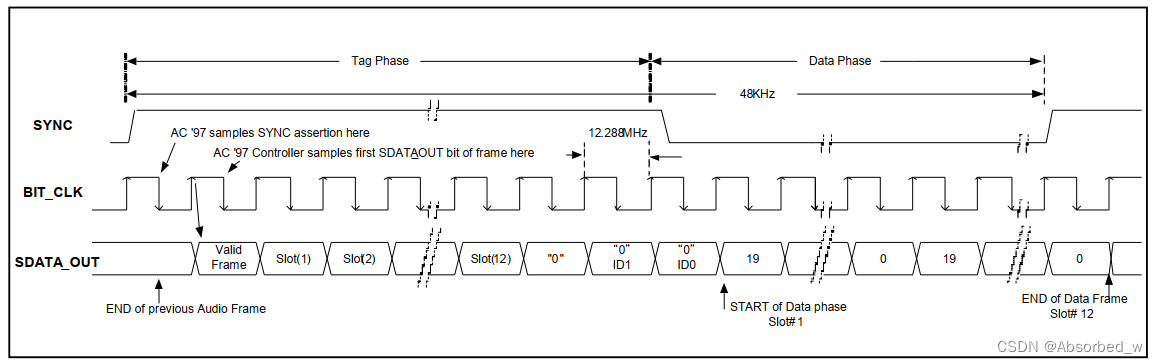

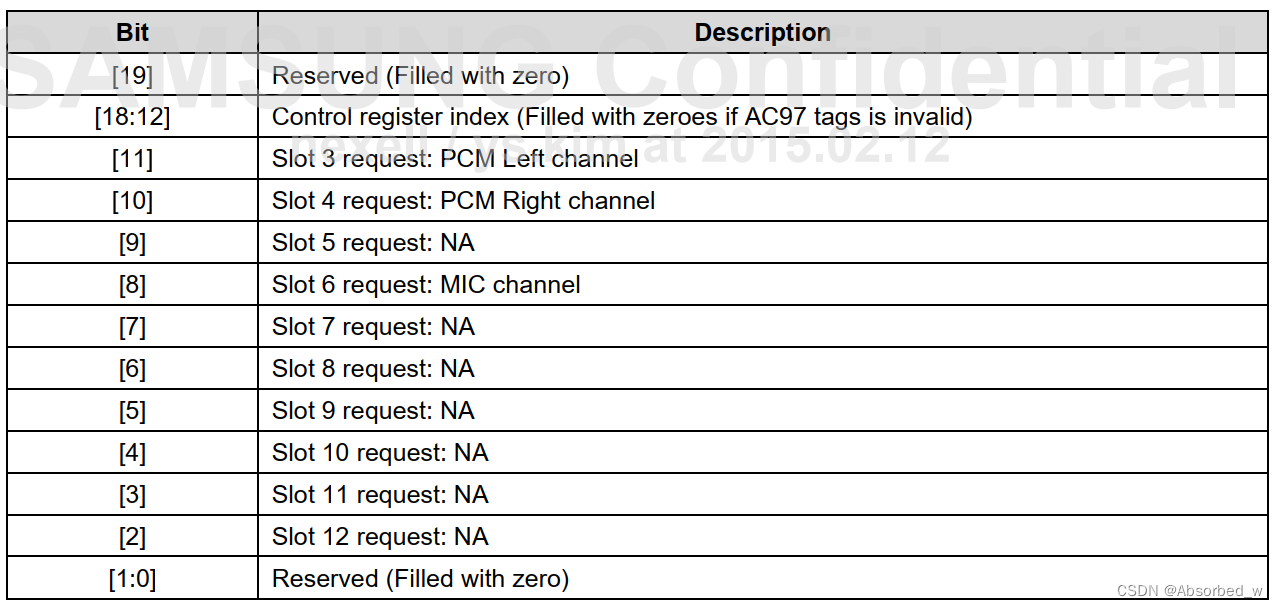

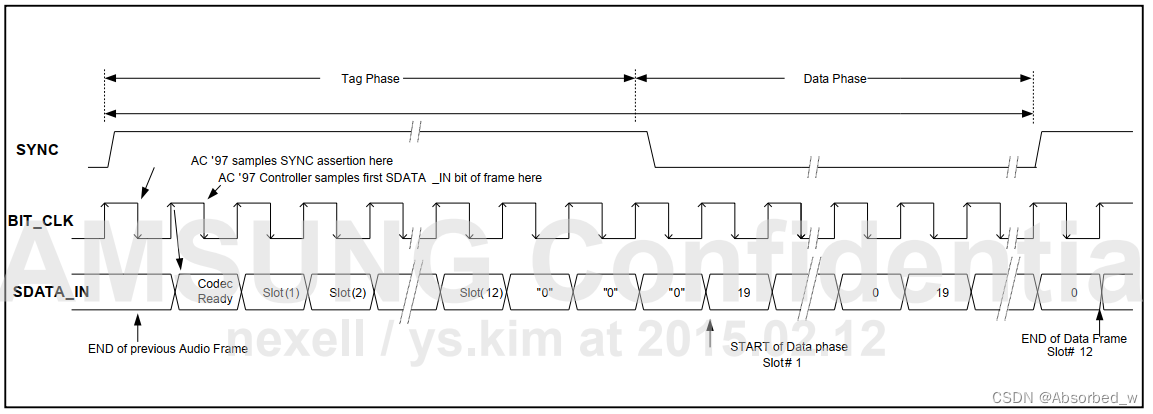

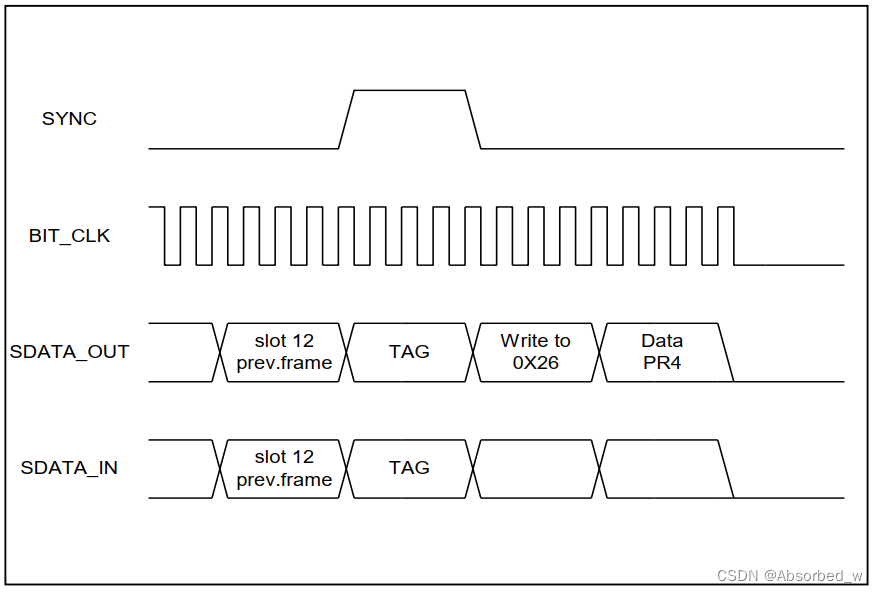

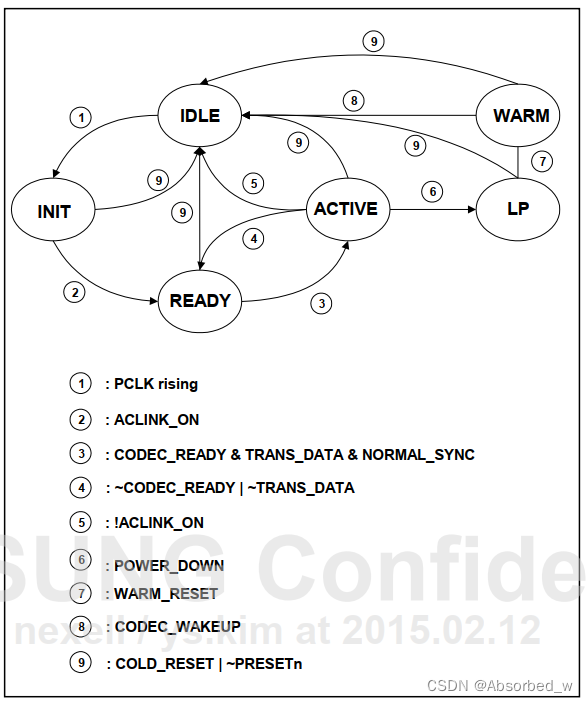

- 1通道AC97

- 独立的立体声PCM输入、立体声PCM输出、单声道MIC输入通道

- 基于DMA操作和中断操作

- 所有通道仅支持16位样本

- 变采样率AC97编解码器接口(48 kHz及以下)

- 每个通道的16位、16个条目FIFO

- 仅支持主要编解码器

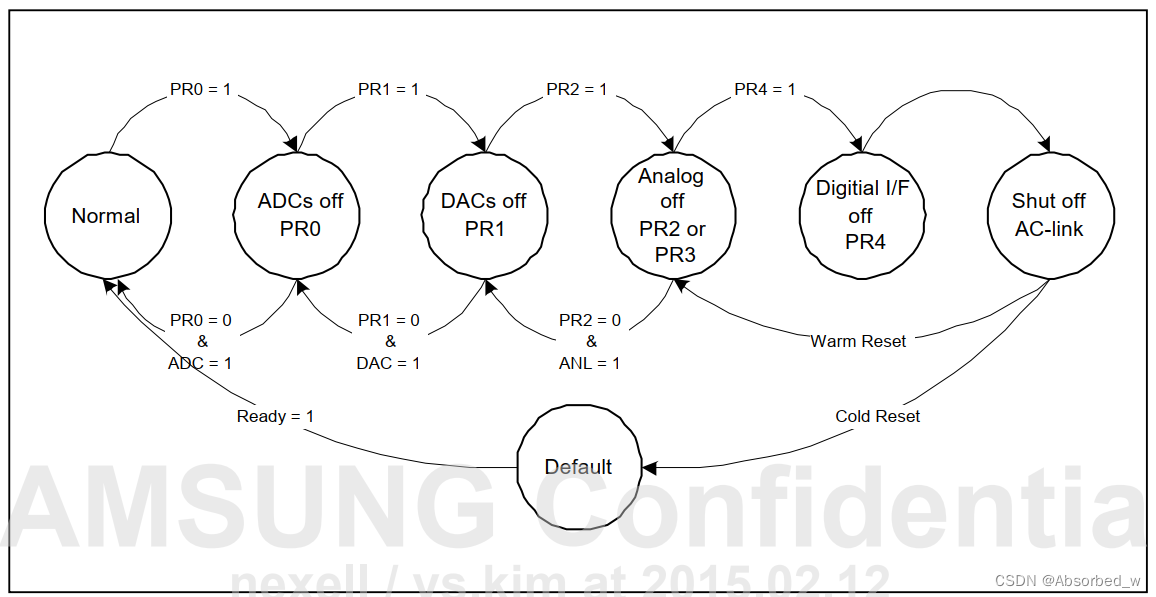

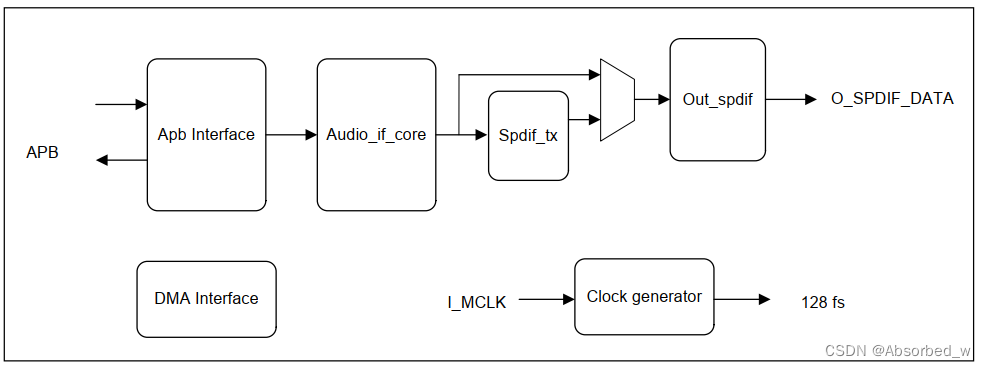

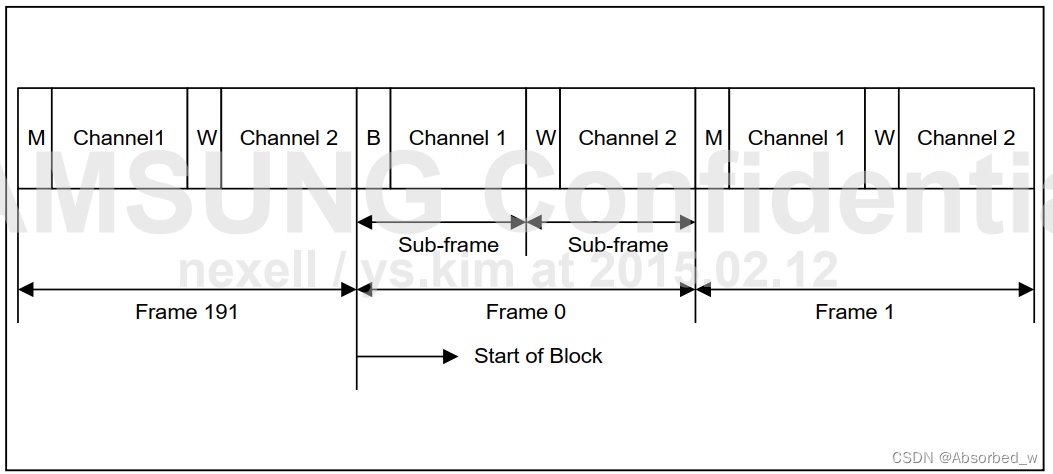

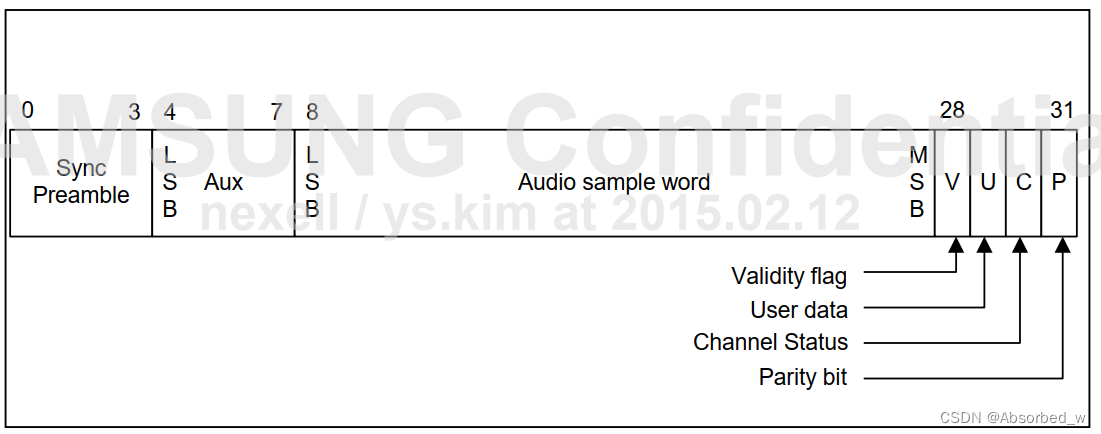

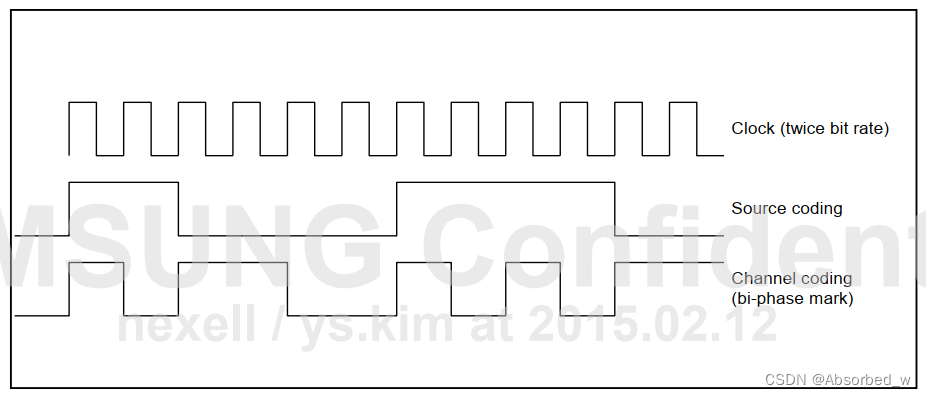

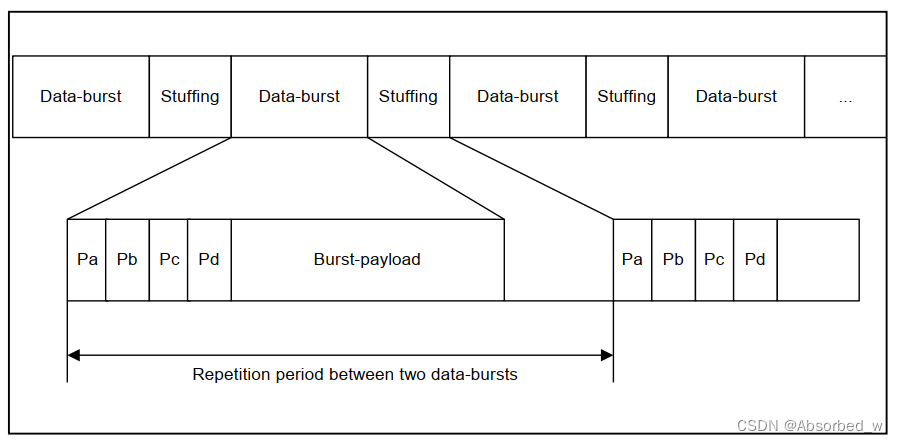

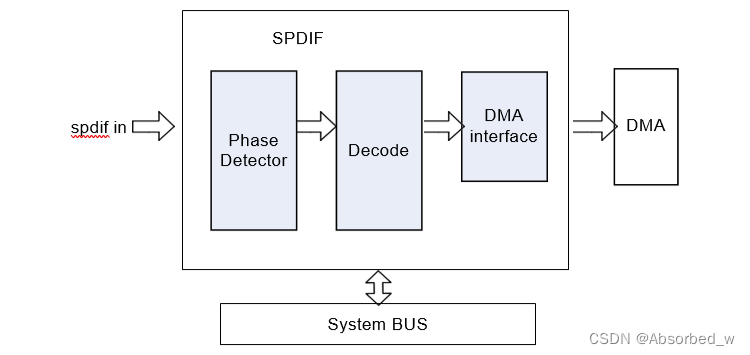

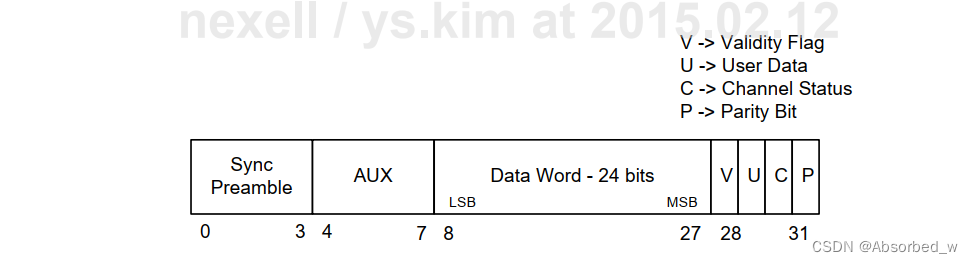

1.4.22 SPDIF发送,接收

- SPDIF发送

- 支持线性PCM,最高24位每样本

- 支持非线性PCM格式,如AC3、MPEG1和MPEG2

- 2×24位缓冲区,交替填充数据

- SPDIF接收

- 串行、单向、自时钟接口

- 单线单信号接口

- 由于极性独立,易于工作

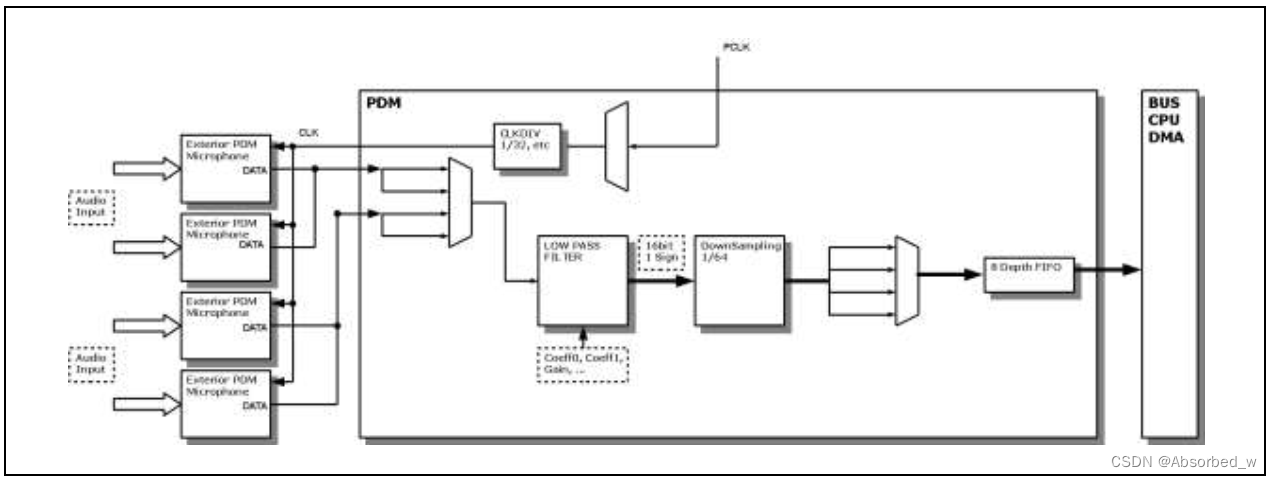

1.4.23 PDM

- 支持用1个数据引脚接收2声道音频数据

- 1个输出时钟引脚

- 2个数据引脚(总共可接受4个声道)

- 固定输出时钟频率

- 支持选择数据捕获的时序

- 支持DMA接口

- 支持用户配置的系数(巴特沃斯低通滤波器)

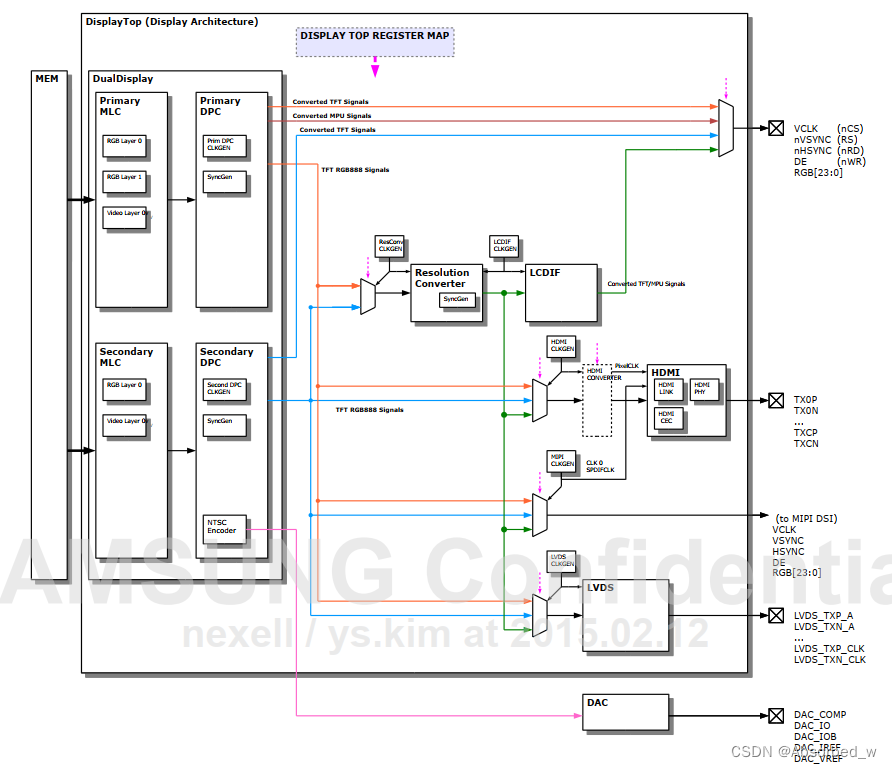

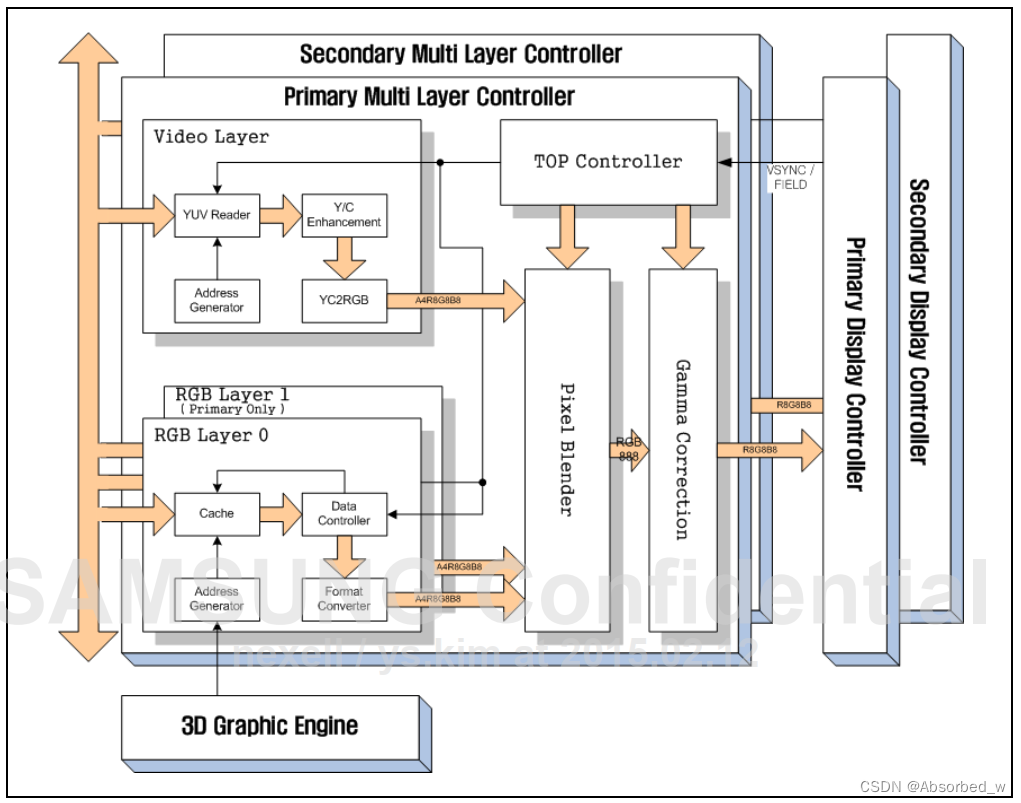

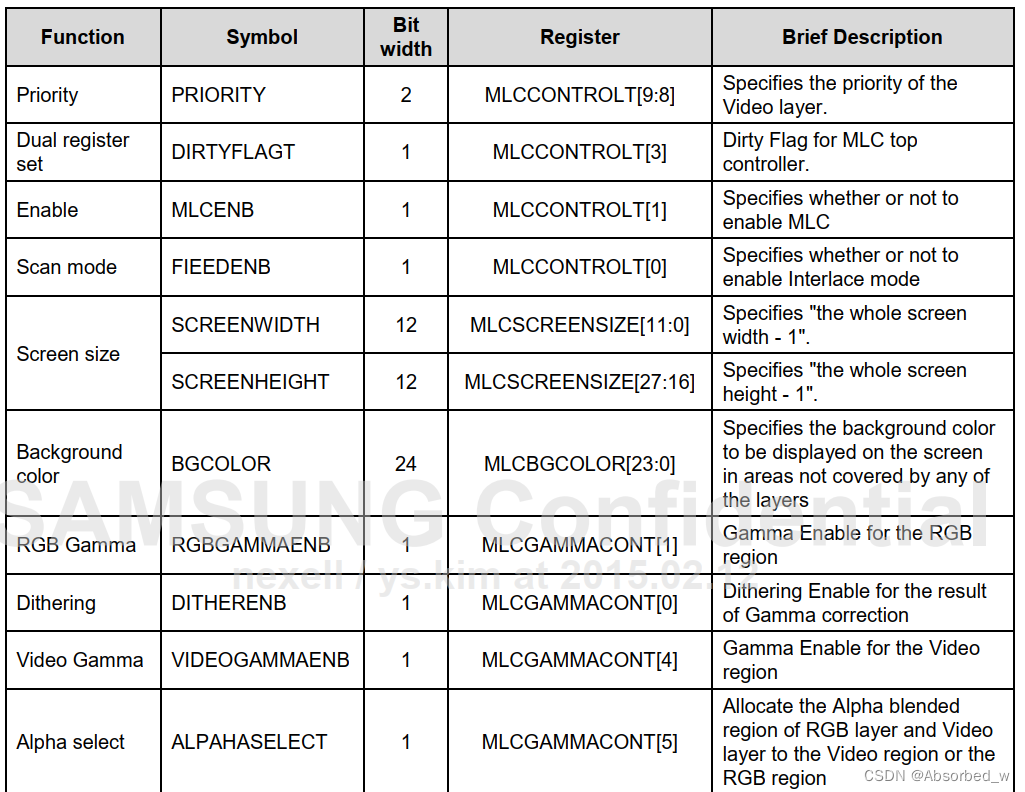

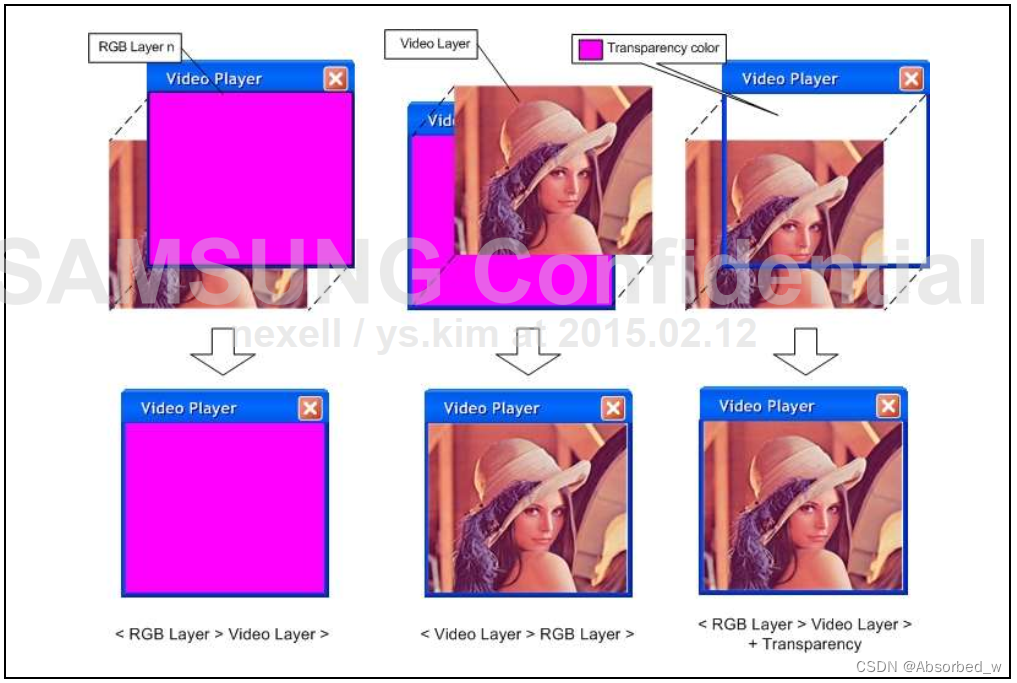

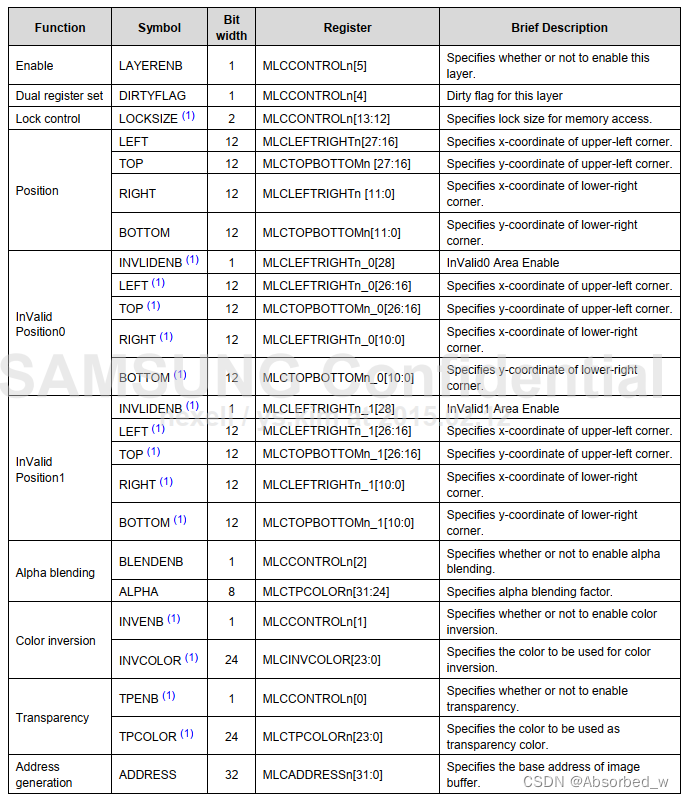

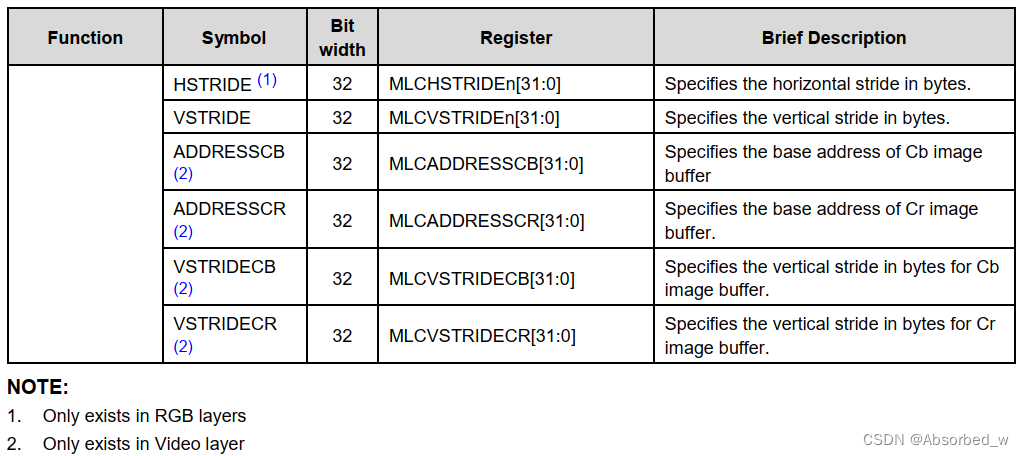

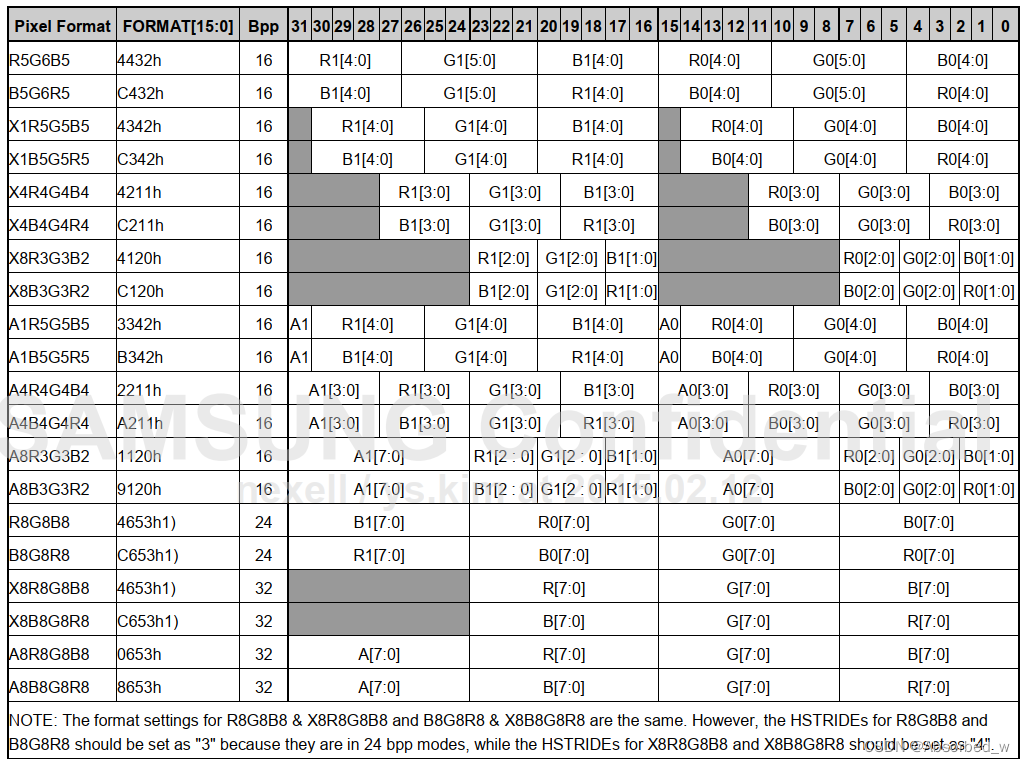

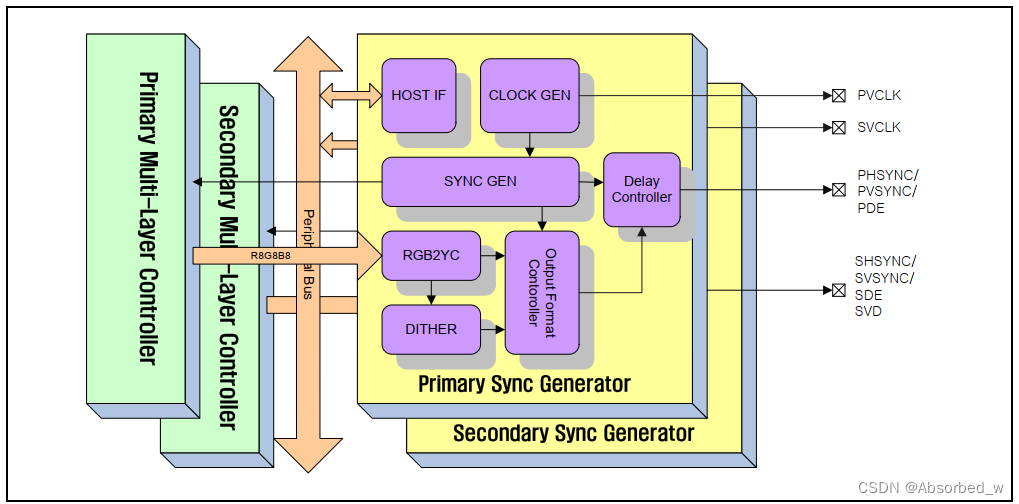

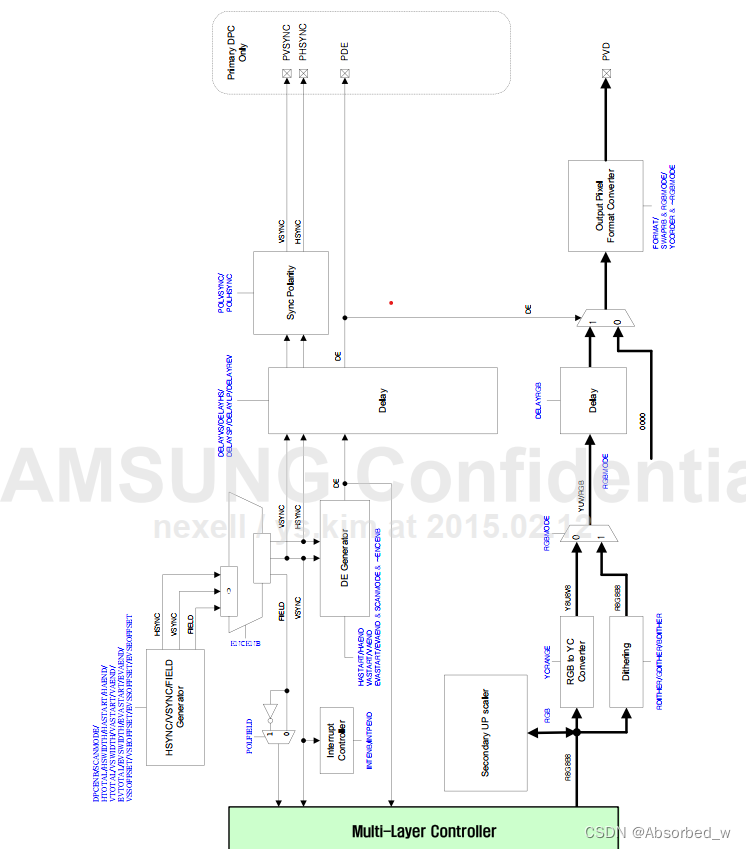

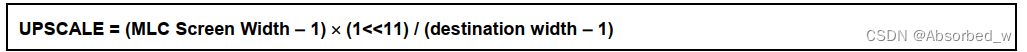

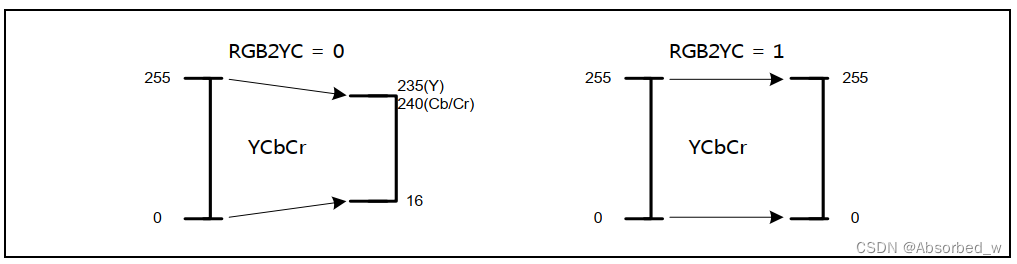

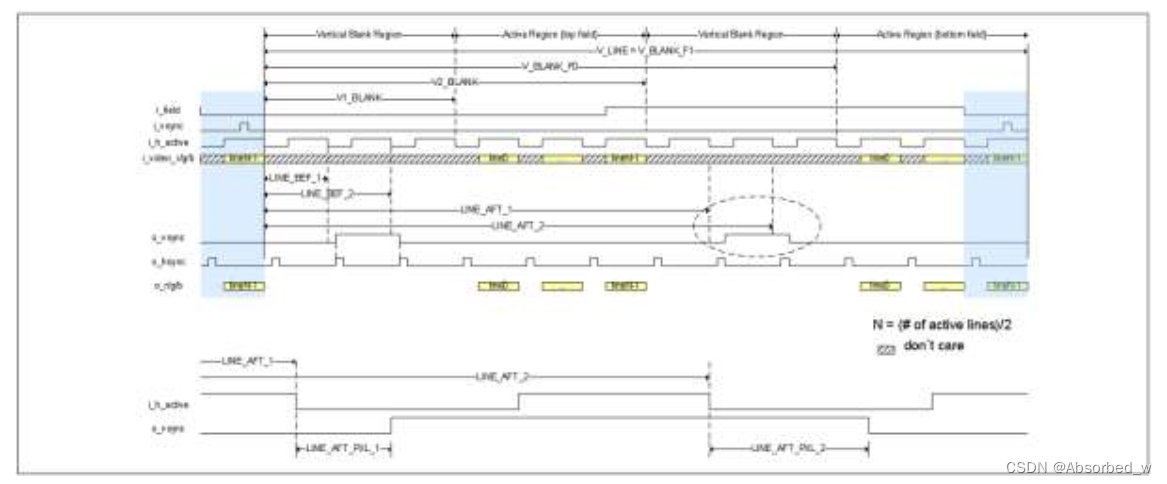

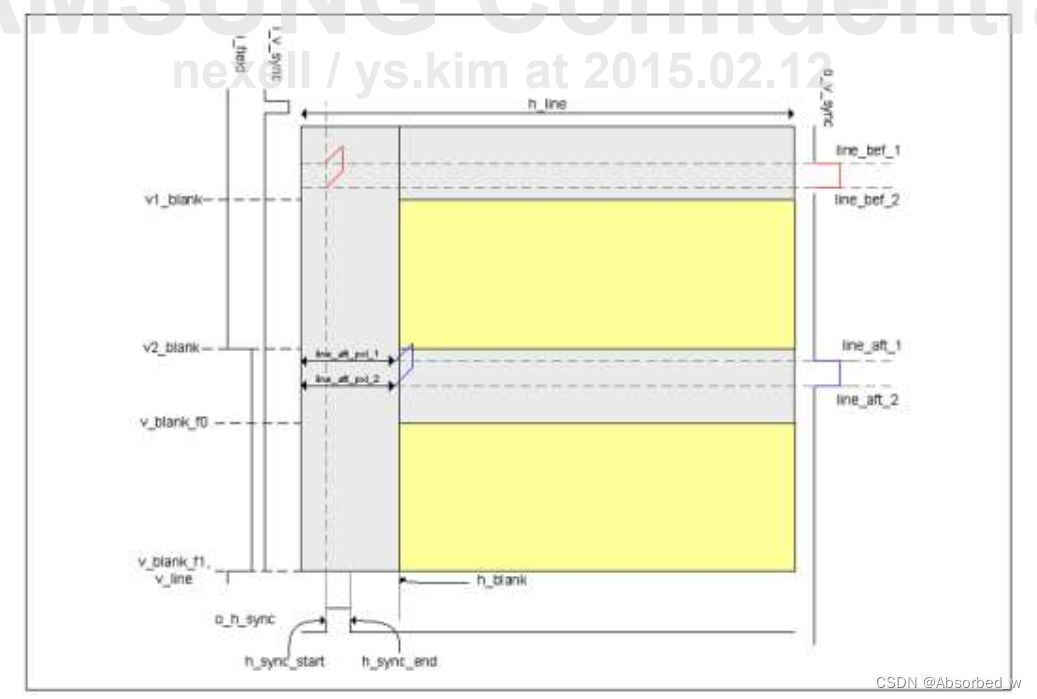

1.4.24 显示控制器

- 支持双显示

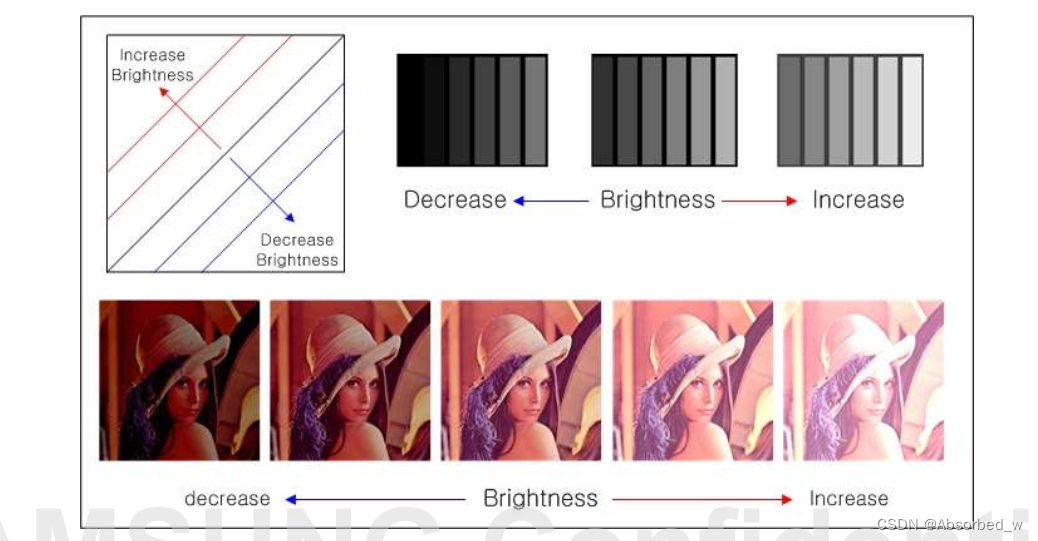

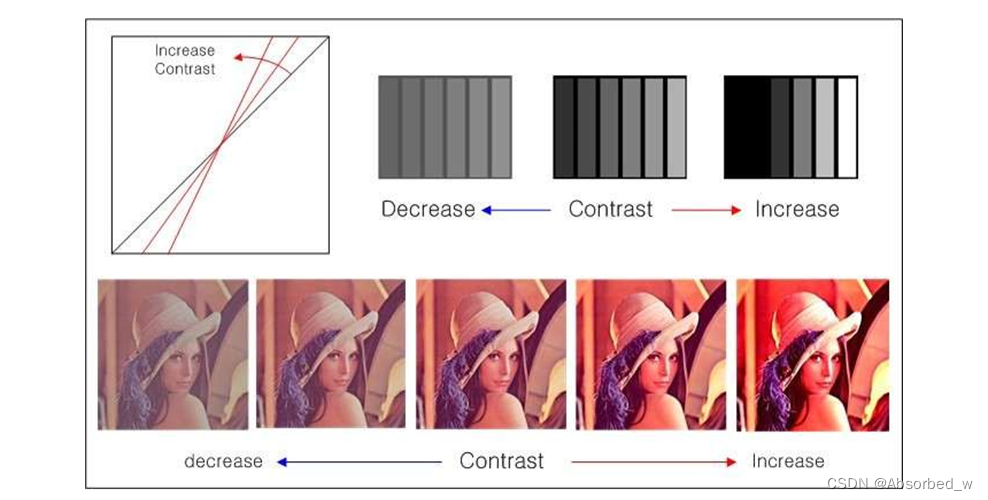

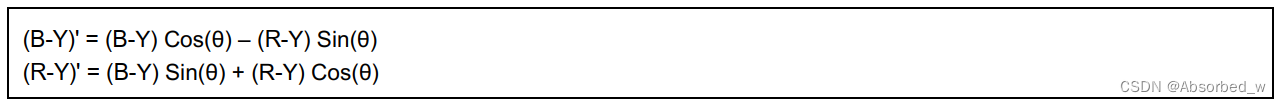

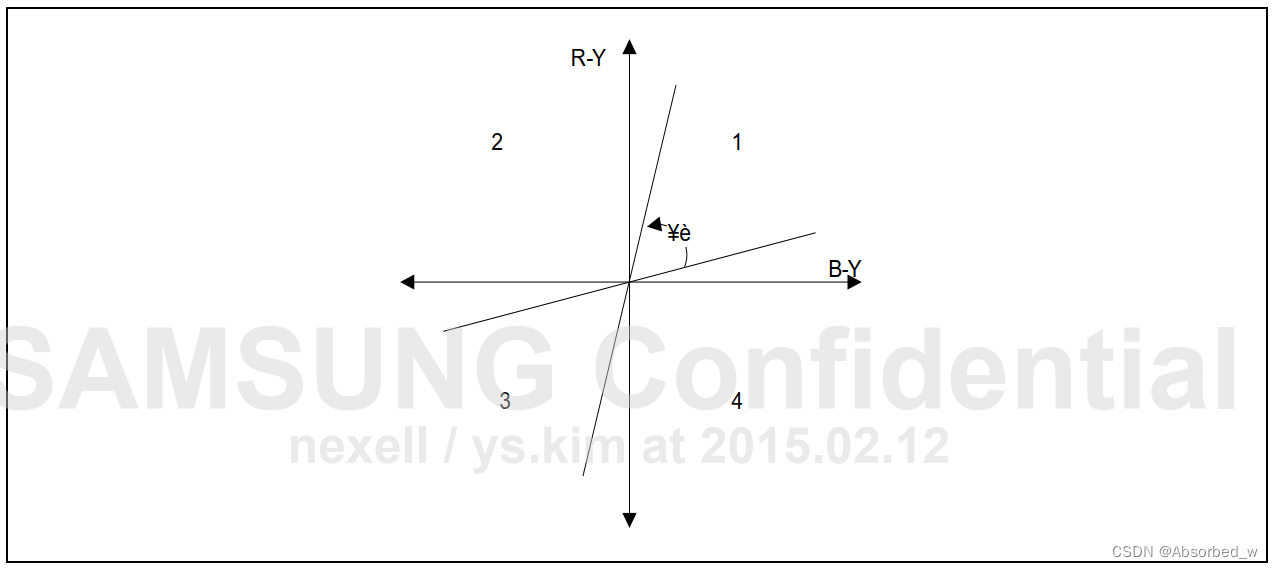

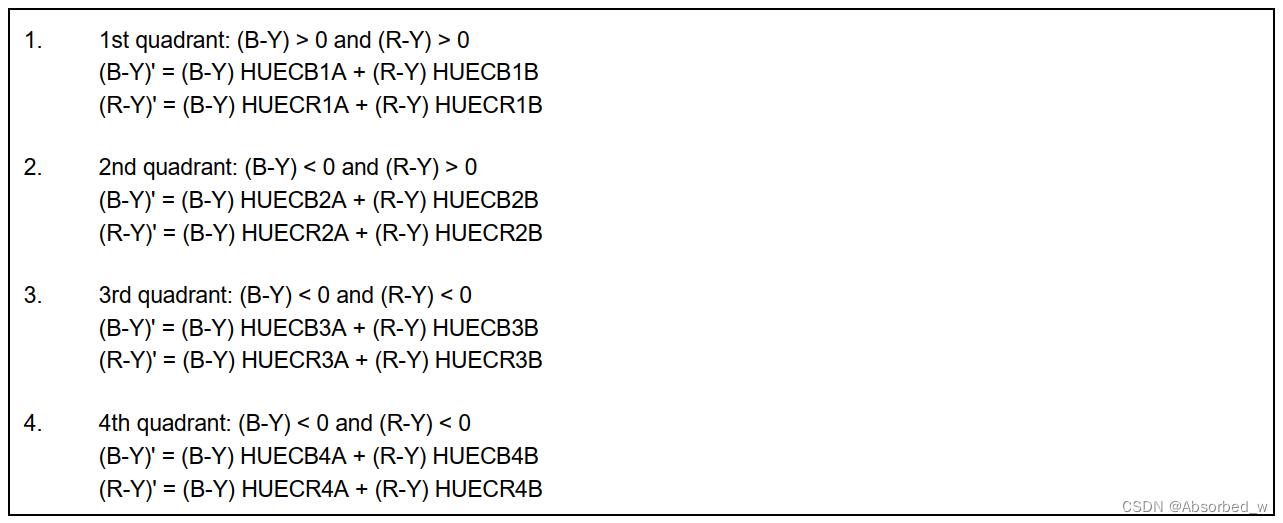

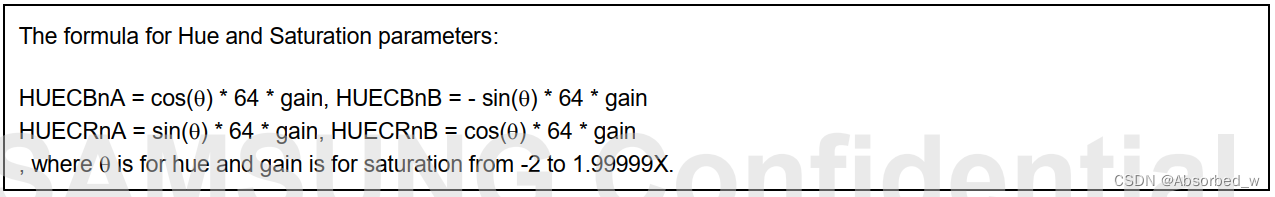

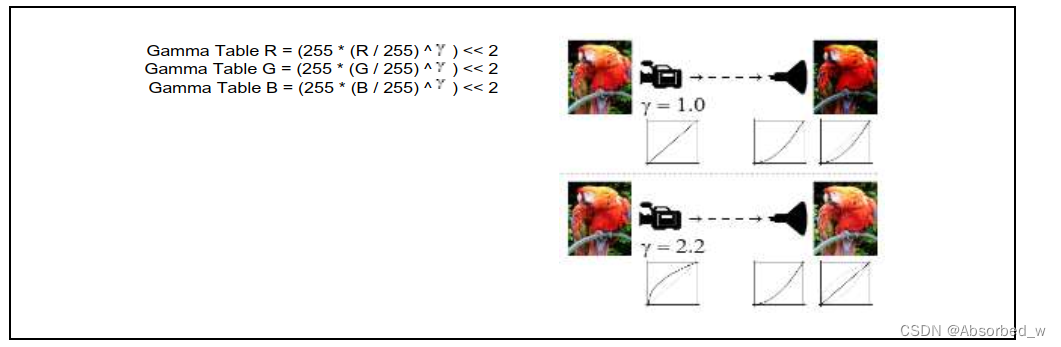

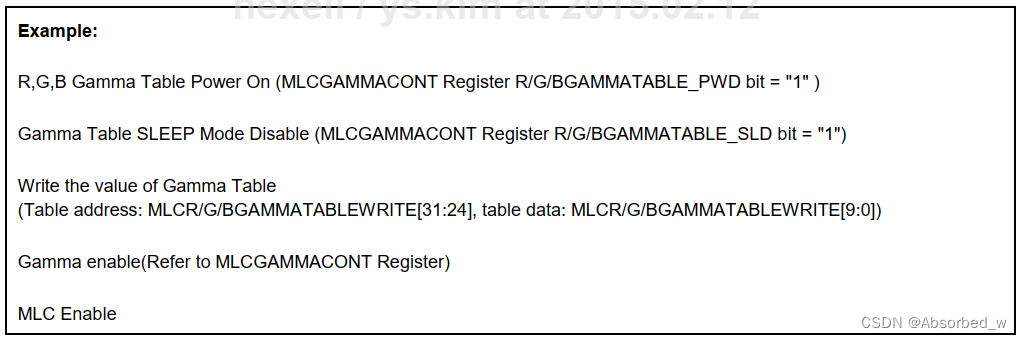

- 支持3层、伽马校正和颜色控制(亮度、对比度、色调和饱和度)

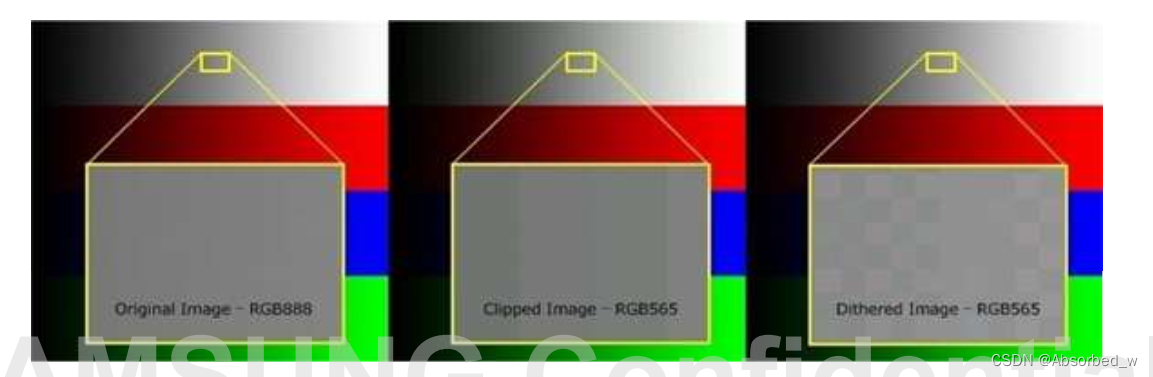

- 支持多种像素格式

- RGB/BGR 444、555、565、888,带或不带Alpha通道

- 分辨率

- 最高1920×1080 @60 Hz

- 支持CVBS输出

- 支持多种LCD

- I80接口、RGB、串行RGB、LVDS输出

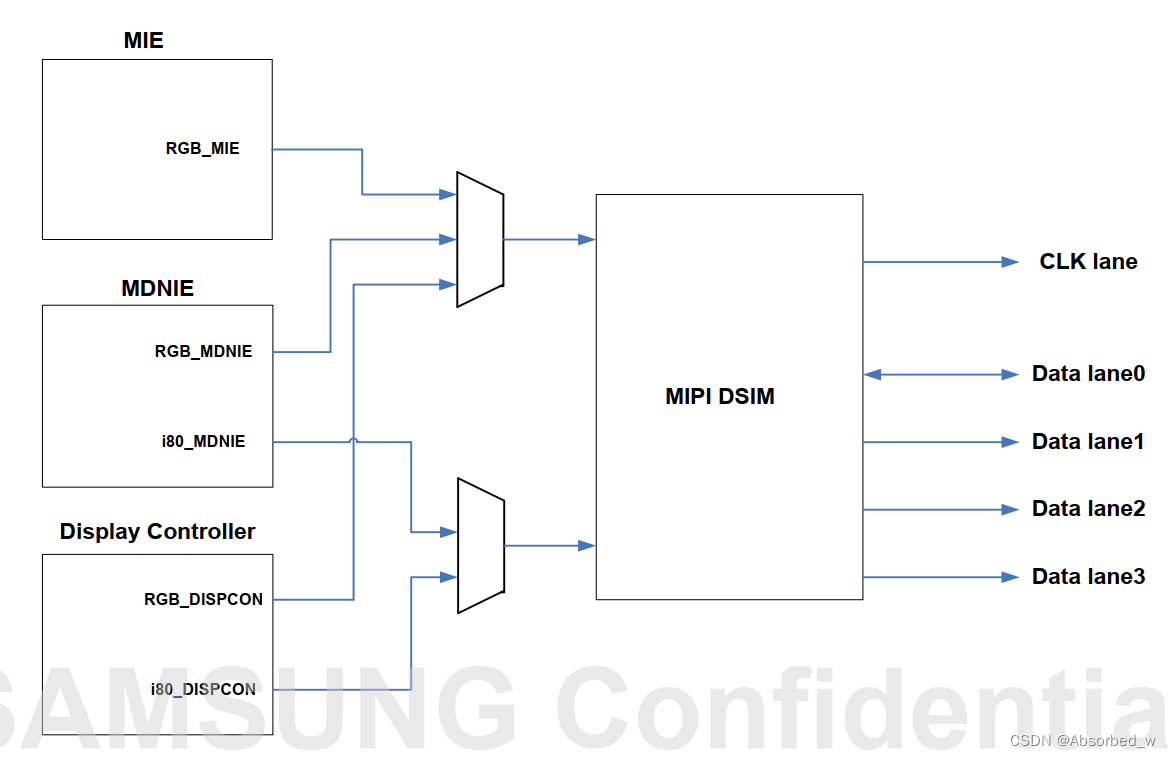

- 支持MIPI-DSI 4数据通道

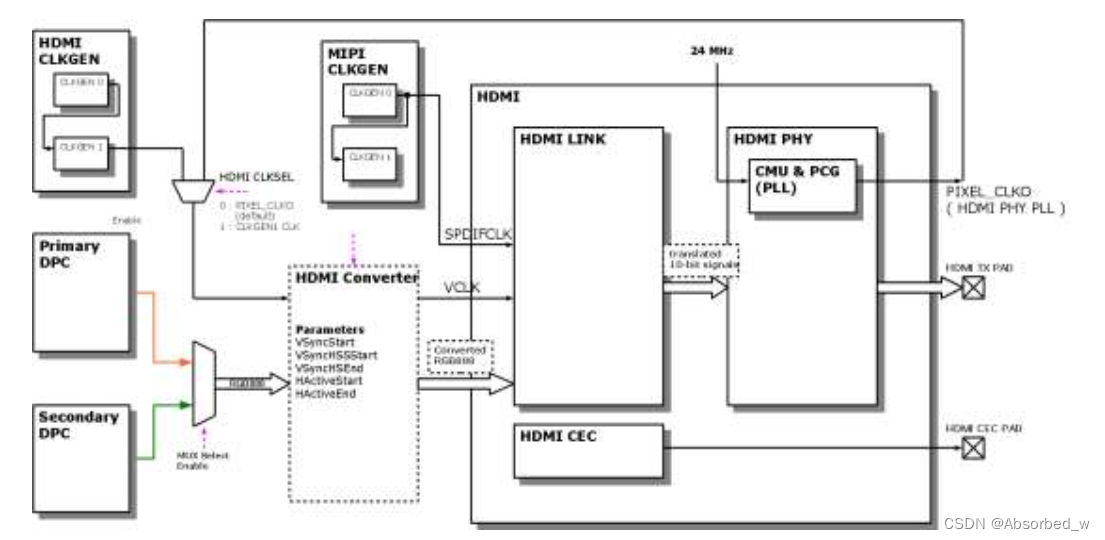

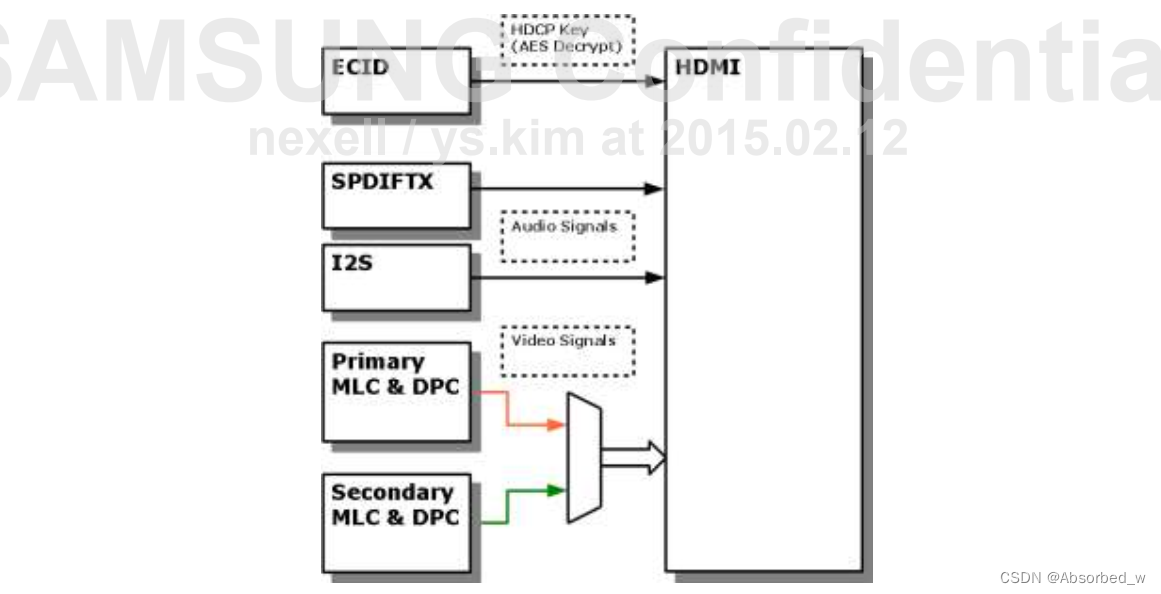

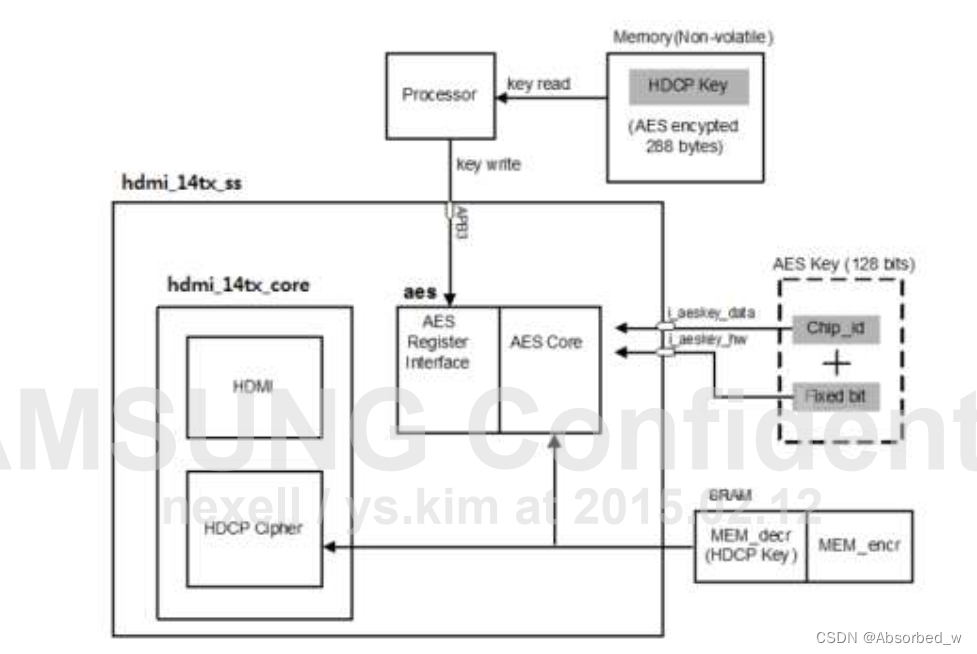

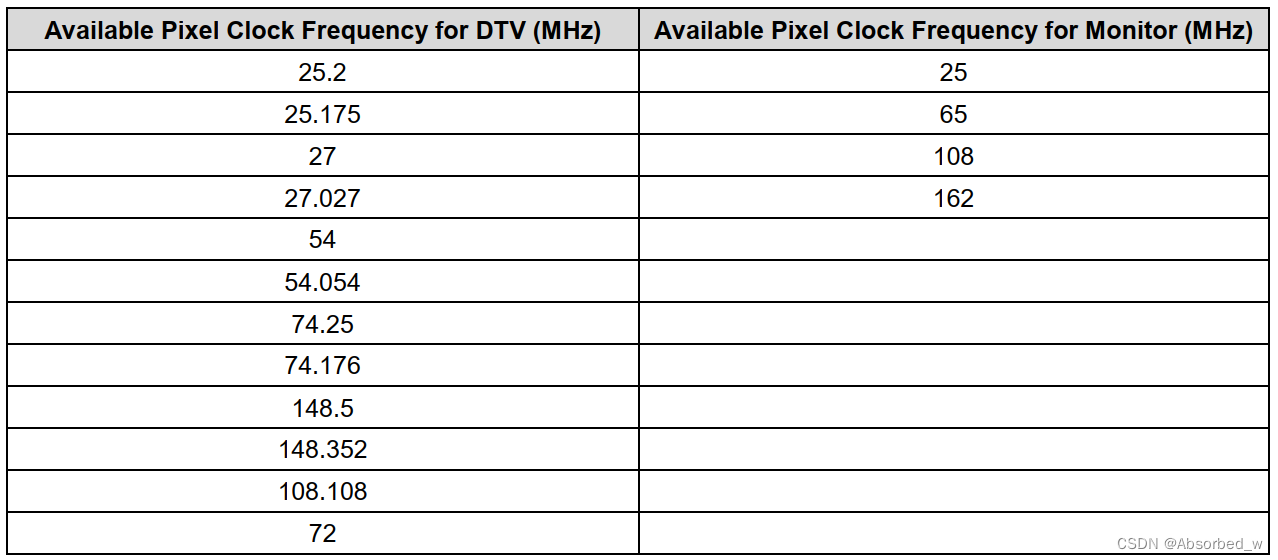

- HDMI 1.4a,HDCP 1.4符合

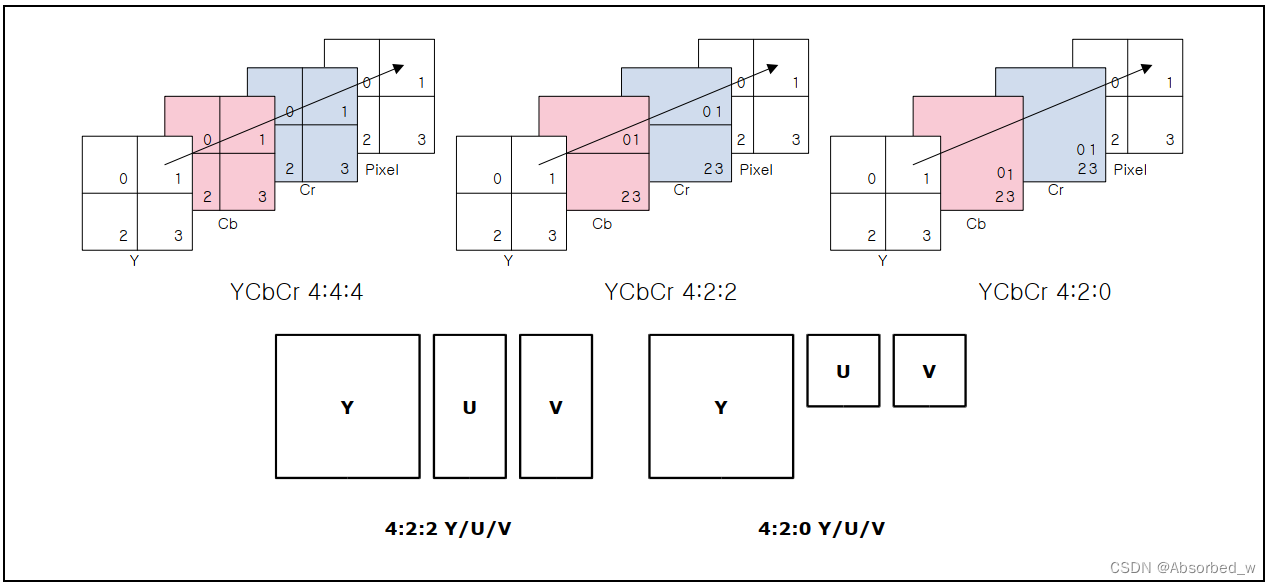

- 支持视频格式:

- 480p/480i @59.94 Hz/60 Hz, 576p/576i@50 Hz

- 720p/720i @50 Hz/59.94 Hz/60 Hz

- 1080p/1080i @50 Hz/59.94 Hz/60 Hz

- 主要3D视频格式

- 其他各种格式,像素时钟最高148 MHz

- 支持颜色格式:4:4:4 RGB/YCbCr,4:2:2 YCbCr

- 像素重复:最高x4

- 支持每颜色位数:8位、10位、12位(注:不支持16位)

- 专用块用于CEC功能

- 支持:线性PCM、非线性PCM和高比特率音频格式(音频样本包和HBR包用于音频传输)

- 集成HDCP加密引擎,用于视频/音频内容保护(认证过程由软件控制,而非硬件)

- 专用CEC模块(分离用于电源/时钟域分离)

- 音频输入的SPDIF接口和I2S接口

- 支持HPD的电平触发中断和SFR

- 支持外部HDCP密钥管理的AES密钥解密功能

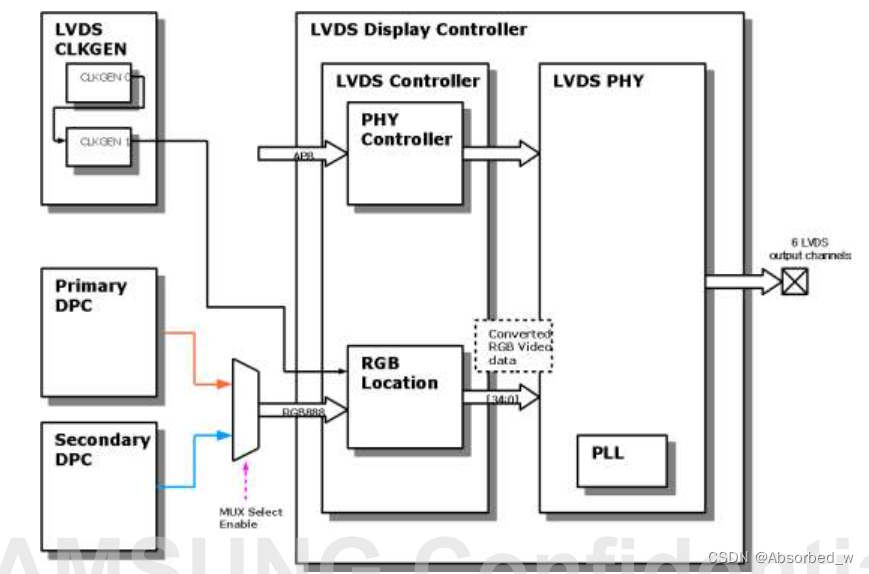

- LVDS接口

- 输出时钟范围:30M至160 MHz

- 每个LVDS通道上最高支持35:7数据通道压缩,速率630 Mbps

- 低功耗模式

- 最高393.75 MB/s带宽

- 最大分辨率:1920×1080 @60 fps

- 下降时钟边缘数据触发

- 窄总线减少了电缆尺寸和成本

- PLL不需要外部组件

- 6个LVDS输出通道(5个数据通道,1个时钟通道)

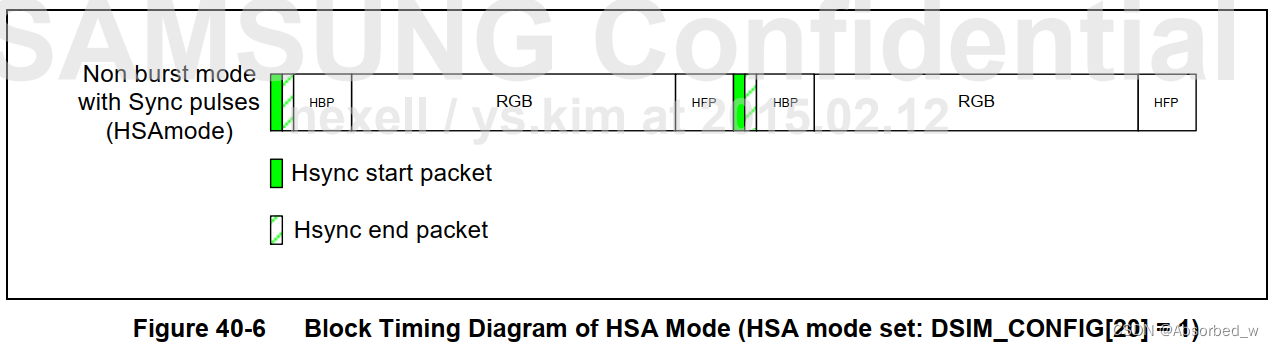

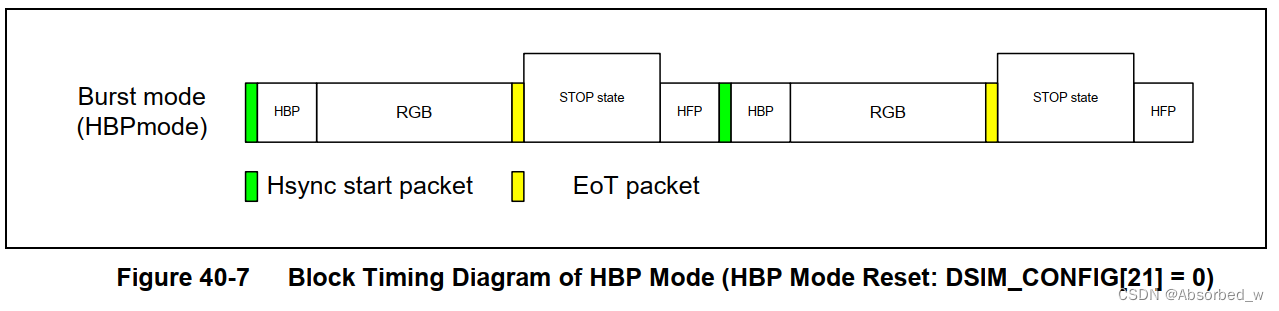

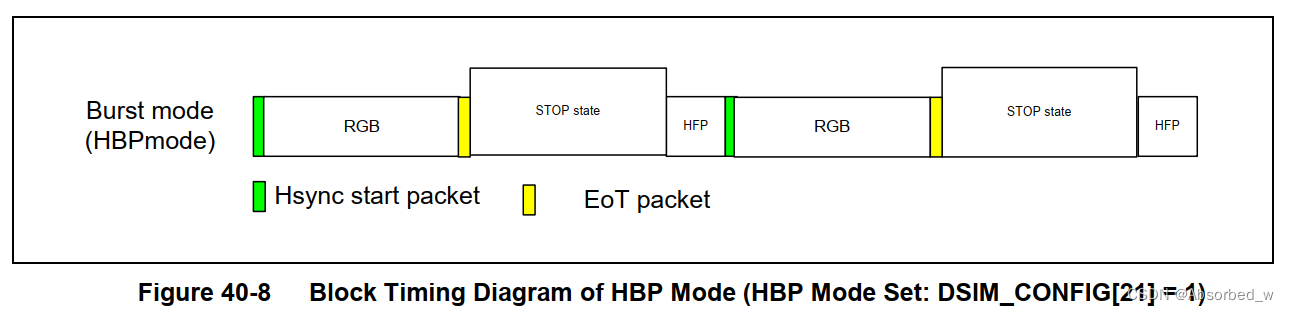

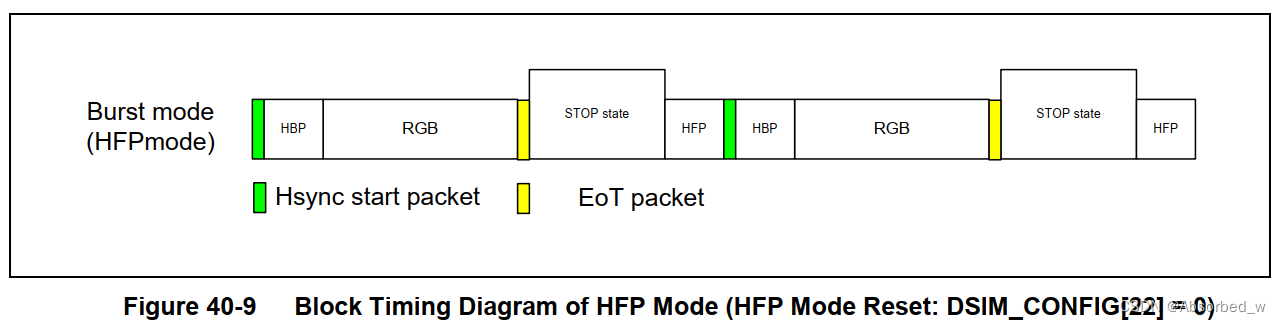

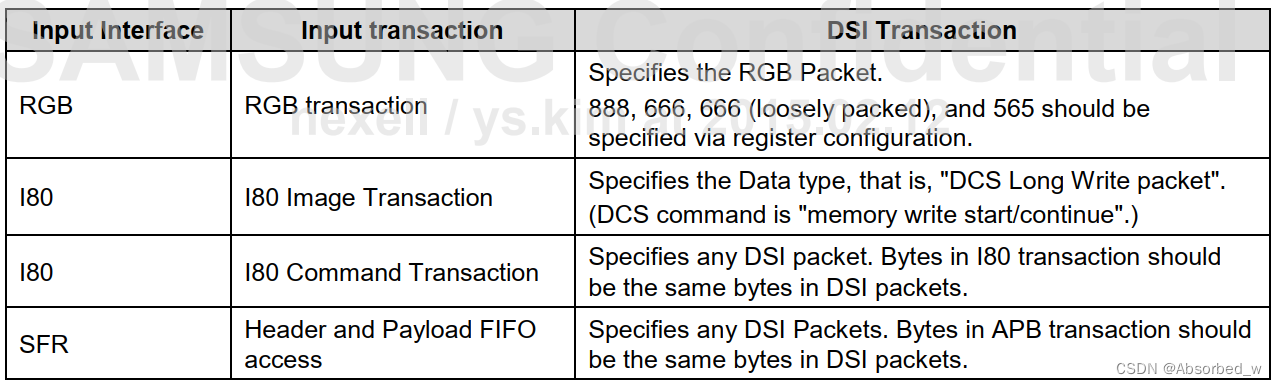

- MIPI-DSI

- 符合MIPI DSI标准规范V1.01r11

- 最大分辨率范围到WUXGA(1920×1200)

- 支持1、2、3或4数据通道

- 支持像素格式:16-bpp、18-bpp打包、18-bpp松散打包(3字节格式)、24-bpp

- 接口

- 符合MIPI D-PHY规范的协议到物理接口(PPI),速率1.5 Gbps

- 支持显示控制器的RGB接口,用于视频图像输入

- 支持显示控制器的I80接口,用于命令模式图像输入

- 支持PLL的PMS控制接口,用于配置字节时钟频率

- 支持预分频器从字节时钟生成逃逸时钟

- 符合MIPI DSI标准规范V1.01r11

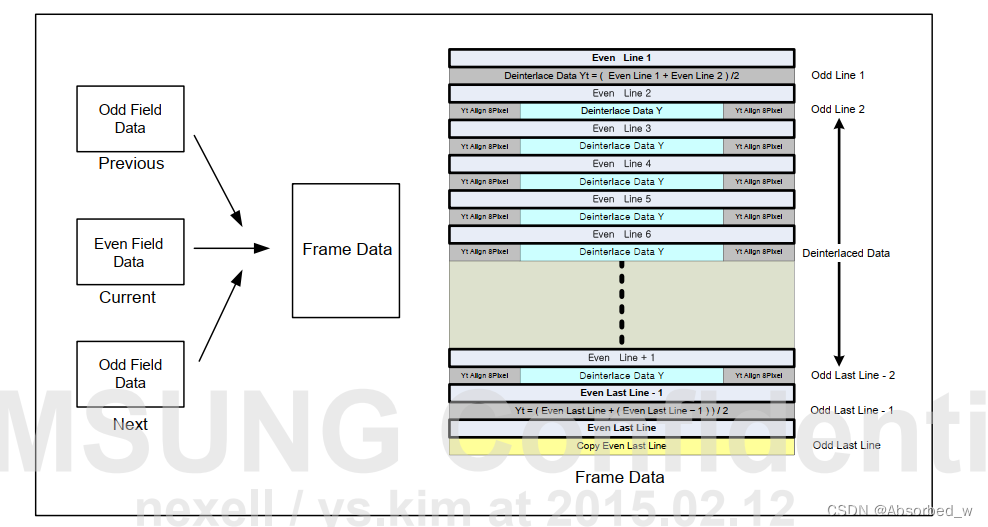

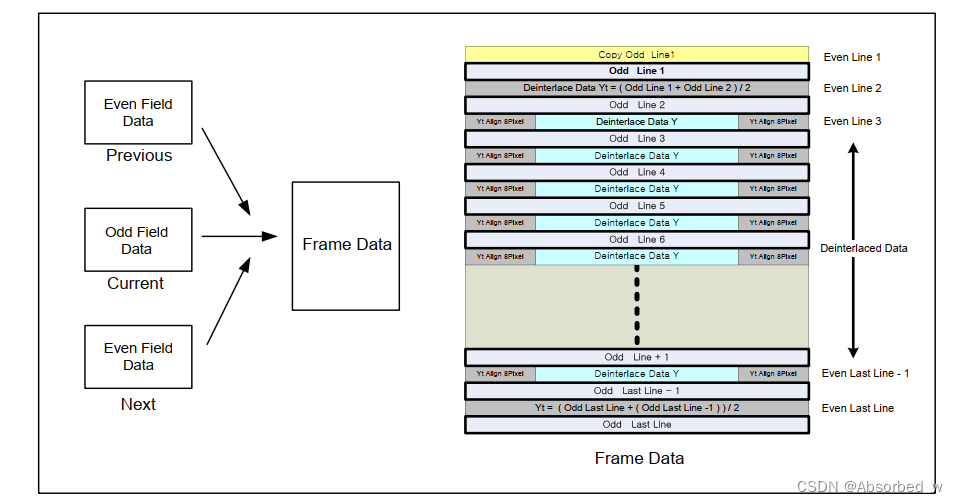

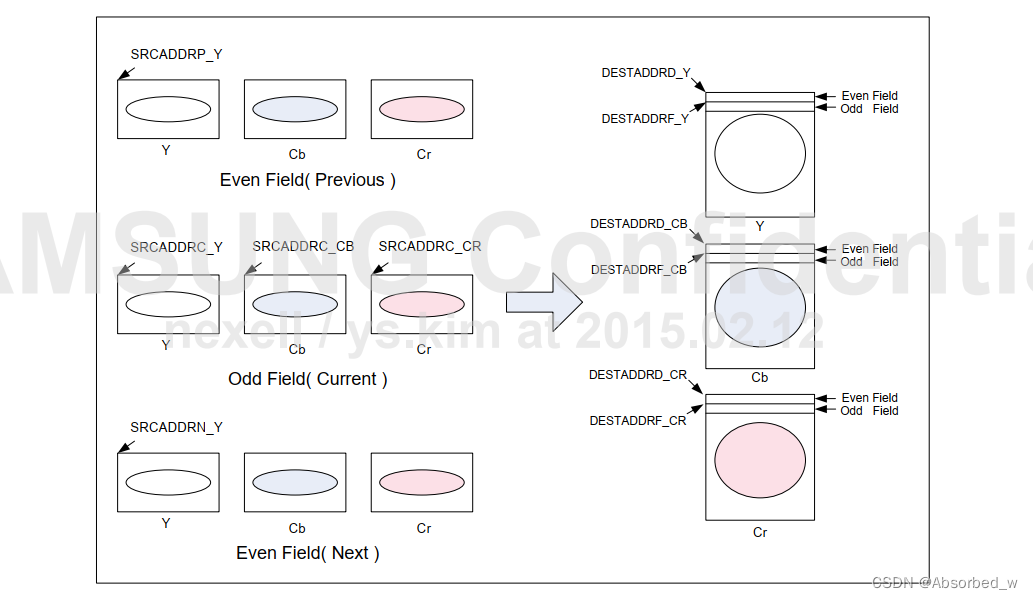

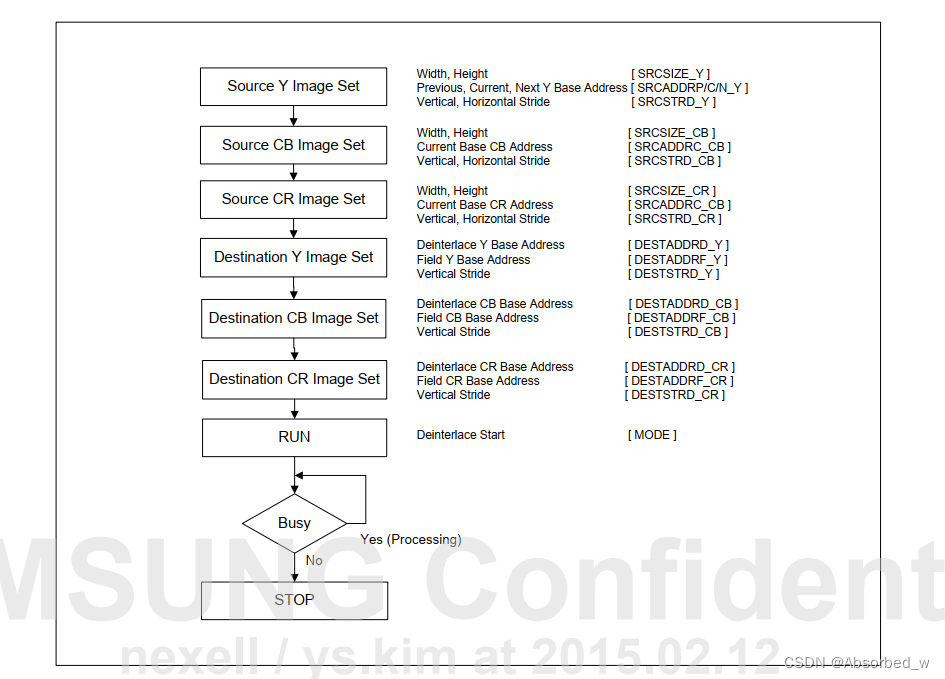

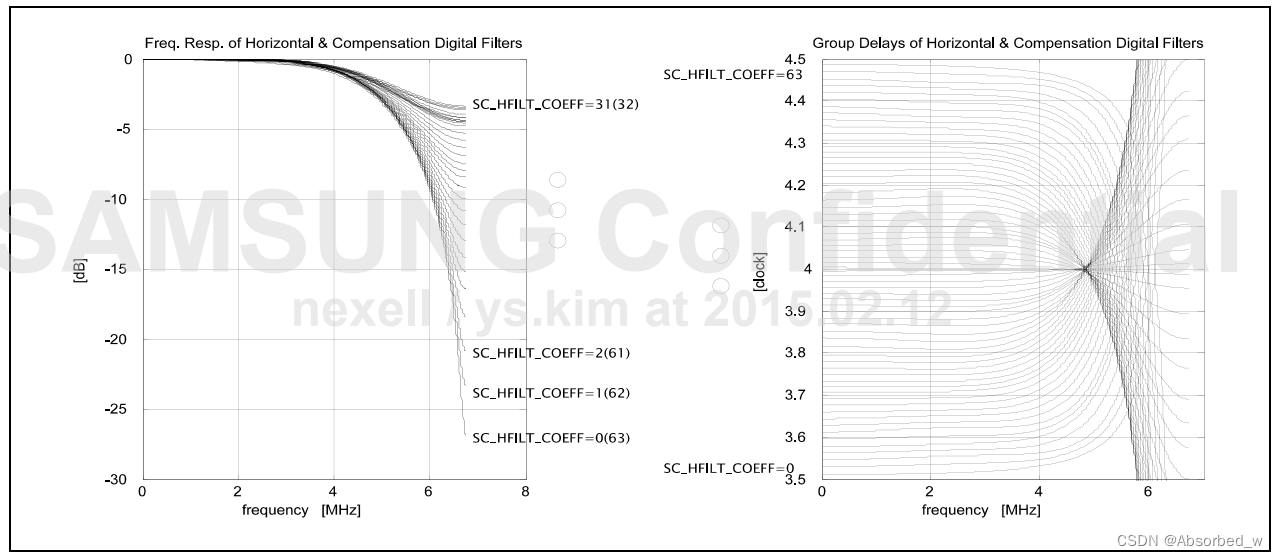

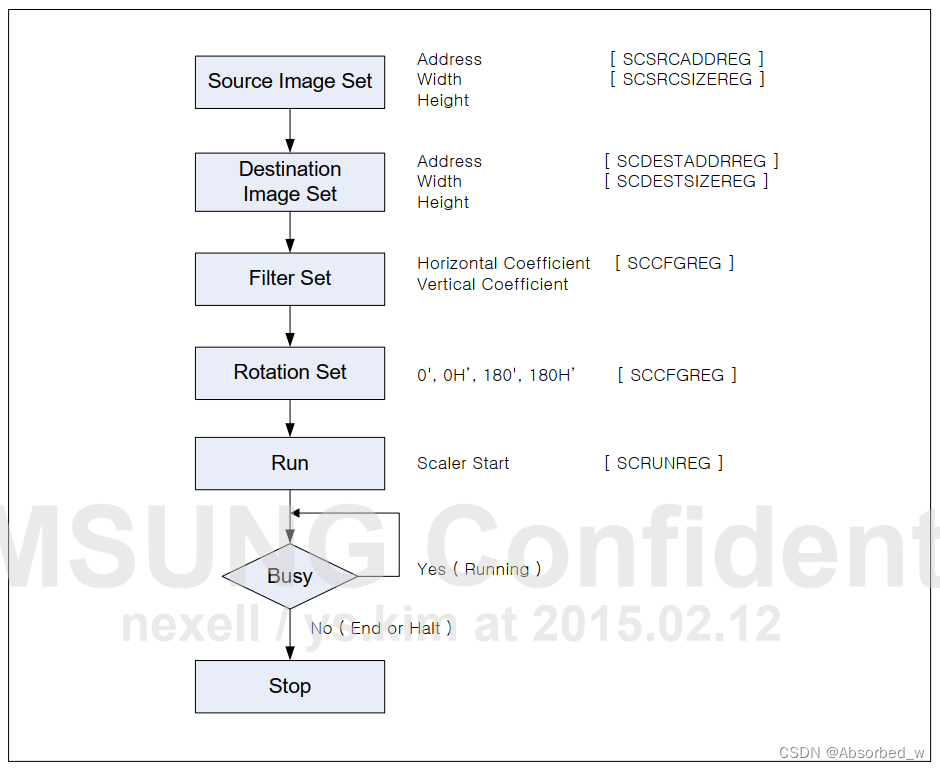

1.4.25 视频后处理器

- 3D去隔行控制器

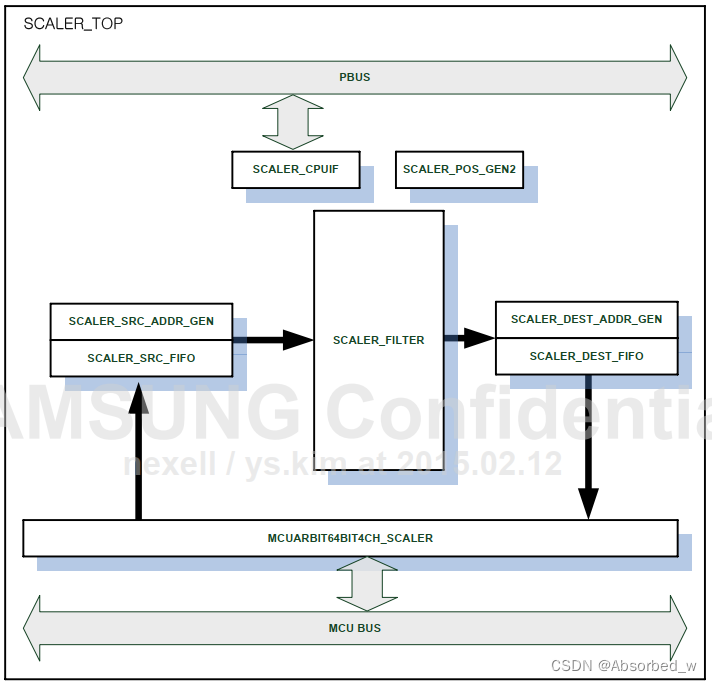

- 视频精细缩放器:多相滤波器

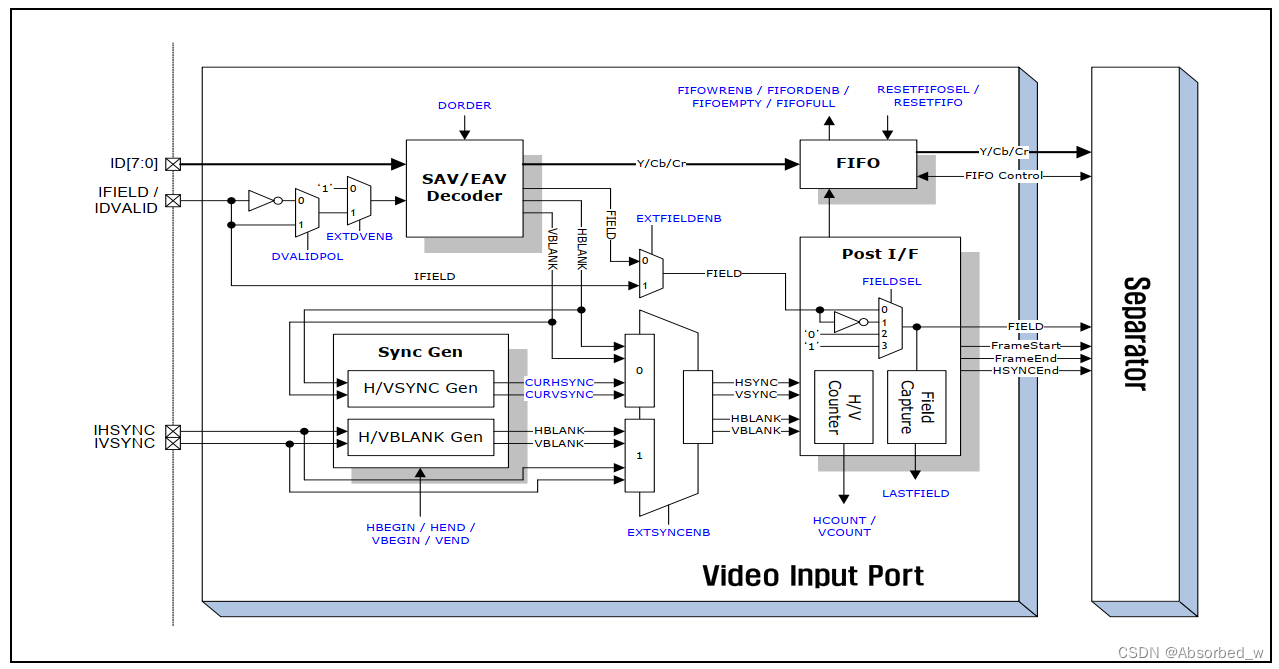

1.4.26 视频输入处理器

- 支持最高8192×8192分辨率

- 同时接收3通道摄像头输入

- 支持3个8位BT656、601格式

- 支持MIPI-CSI

- 通用特性

- 支持主要和次要图像格式

- YUV420、YUV420(Legacy)、YUV420(CSPS)、YUV422,8位和10位

- RGB565、RGB666、RGB888

- RAW6、RAW7、RAW8、RAW10、RAW12、RAW14

- 压缩格式:10-6-10、10-7-10、10-8-10

- 所有用户定义的字节为基础的数据包

- 支持嵌入式字节为基础的非图像数据包和通用短包

- 兼容MIPI D-PHY规范中的PPI(协议到物理接口)

- 支持4通道虚拟通道或数据交错

- 支持主要和次要图像格式

- 标准符合性

- 符合MIPI CSI2标准规范V1.01r06

- D-PHY标准规范V1.0

- 通用特性

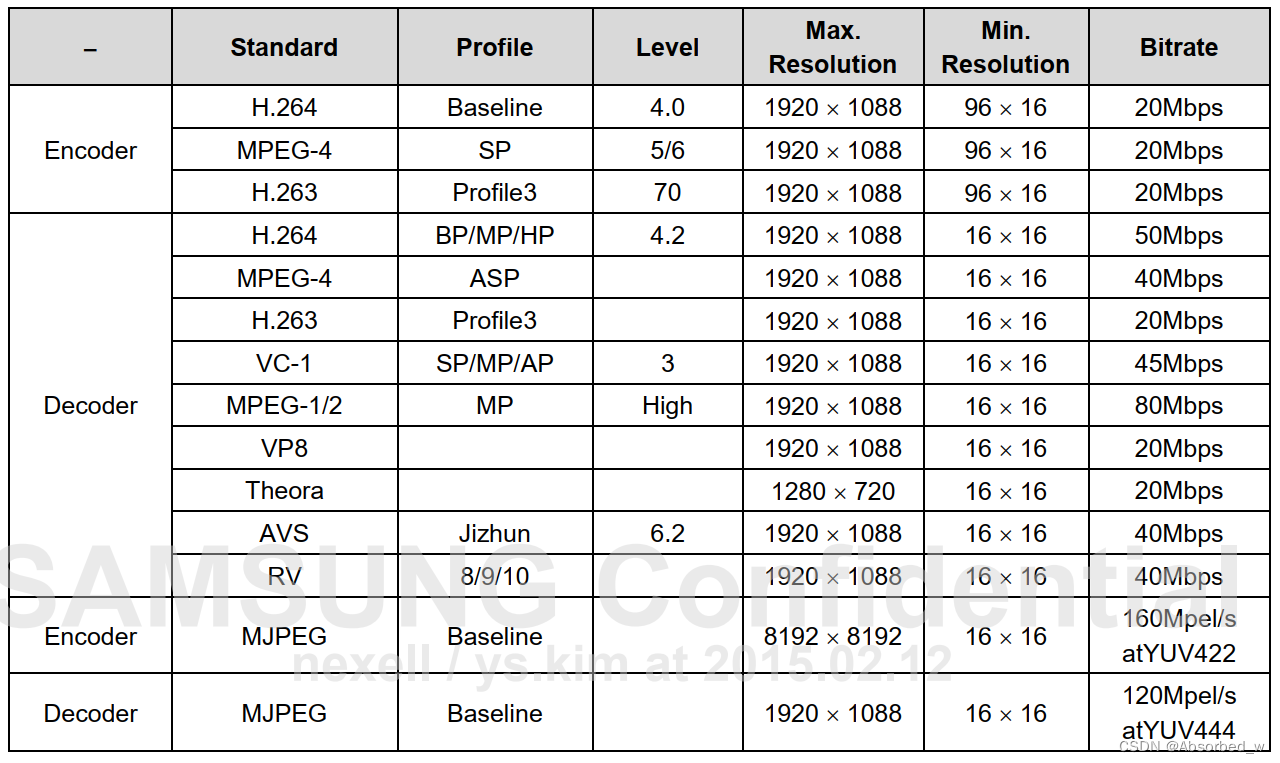

1.4.27 多格式MPEG编解码器

- 解码器

- H.264

- BP、MP、HP配置文件,4.2级,最高1920×1080,50 Mbps

- MPEG4 ASP

- 高级简单配置文件,最高1920×1080,40 Mbps

- H.263

- 3级配置文件,最高1920×1080,20 Mbps

- VC-1

- SP/MP/AP配置文件,3级,最高1920×1080,2048×1024,45 Mbps

- MPEG-1/2

- 主要配置文件,高级级别,最高1920×1080,80 Mbps

- VP8

- 最高1920×1080,20 Mbps

- Theora

- 最高1280×720,20 Mbps

- AVS

- Jizhun配置文件,6.2级,最高1920×1080,40 Mbps

- RV8/9/10

- 最高1920×1080,40 Mbps

- MJPEG

- 基线配置文件,最高8192×8192

- H.264

- 编码器

- H.264

- 基线配置文件,4.0级,最高1080p,20 Mbps

- MPEG4

- 简单配置文件,5.6级,最高1080p,20 Mbps

- H.263

- 3级配置文件,70级,最高1080p,20 Mbps

- MJPEG

- 基线配置文件,最高8192×8192

- H.264

1.4.28 3D图形控制器

- 支持OpenGL ES 1.0和2.0

- 支持OpenVG 1.1

- GPU是2D和3D图形系统的硬件加速器

- GPU由以下部分组成:

- 四个像素处理器(PPs)

- 一个几何处理器(GP)

- 一个2级缓存控制器(L2)

- 每个GP和PP包含一个内存管理单元(MMU)

- 一个电源管理单元(PMU)

- 像素处理器特性

- 每个像素处理器使用不同的流水线,支持更快的周转

- 可编程片段着色器

- Alpha混合

- 完全支持非幂次方2的纹理

- 立方映射

- 快速动态分支

- 快速三角函数,包括反正切

- 完整的浮点运算

- 帧缓冲区混合带目标Alpha

- 索引纹理采样器

- 线、四边形、三角形和点精灵

- 程序长度无限制

- 透视正确纹理

- 点采样、双线性和三线性过滤

- 可编程的mipmap层次细节偏置和替换

- 模板缓冲区,8位

- 双面模板

- 无限依赖纹理读取

- 4级分层Z和模板操作

- 最高512倍全屏抗锯齿(FSAA),4倍多重采样乘以128倍超采样

- 每纹素4位压缩纹理格式

- 几何处理器特性

- 可编程顶点着色器

- 灵活的输入和输出格式

- 自主操作平铺列表生成

- 索引和非索引几何输入

- 点、线、三角形和四边形的原语构建

- 2级缓存控制器特性

- 尺寸为64 KB

- 4路组相连

- 支持最多32个未完成的AXI事务

- 实现标准的伪LRU算法

- 缓存行和行填充突发大小为64字节

- 支持8到64字节非缓存读取突发和写入突发

- 128位接口到内存子系统

- 支持命中下失和失下失,唯一限制是AXI排序规则

- MMU特性

- 通过总线基础设施访问控制寄存器,以配置内存系统

- 每个处理器都有自己的MMU,以控制和翻译GPU发起的内存访问

- PMU特性

- 可编程电源管理

- 分别为每个GP、PP和2级缓存控制器供电和断电

- 控制每个设备的时钟、隔离和电源

- 在所有请求的设备上电时提供中断

1.4.29 安全IP

- 片上安全启动ROM/RAM

- ARM TrustZone:TZPC、TZASC和TZMA

- 硬件加密加速器

- DES/TDES、AES、SHA-1、MD5和PRNG

- 支持安全JTAG

1.4.30 独特芯片ID

- 支持128位独特芯片ID寄存器

1.4.31 操作条件

- 工作电压

- 核心:0.95至1.1 V

- CPU:0.95 V至1.35 V

- DDR内存:1.2至1.5 V

- I/O:3.3 V

- 工作温度

- 环境温度:-25°C至85°C

- 芯片温度:-25°C至85°C

1.4.32 封装

- 537针脚FCBGA封装

- 球间距:0.65毫米

- 体积:17×17毫米

2 机械尺寸和IO功能描述

详情见原文。

3 系统启动

3.1 概述

S5P6818支持多种系统启动模式。启动模式由系统配置在启动复位关闭时确定。

- 外部静态内存启动

- 内部ROM启动

- 带错误校正的NAND启动

- SD/MMC/SDFS(SD FAT文件系统)启动

- SPI串行EEPROM启动

- UART启动

- USB启动

3.2 功能描述

3.2.1 系统配置

| Pins | RST_CFG | Static Memory | SDFS (TBD) | UART | Serial Flash | SD MMC | USB Device | Nand |

| SD0 | RST_CFG0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| SD1 | RST_CFG1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| SD2 | RST_CFG2 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| SD3 | RST_CFG3 | Port_Num0 | Port_Num0 | Port_Num0 | Port_Num0 | SELCS | ||

| SD4 | RST_CFG4 | ADDRWIDTH0 | 0 | |||||

| SD5 | RST_CFG5 | ADDRWIDTH1 | 0 | |||||

| SD6 | RST_CFG6 | BAUD | SPEED | |||||

| SD7 | RST_CFG7 | |||||||

| DISD0 | RST_CFG8 | LATADDR | LATADDR | LATADDR | LATADDR | LATADDR | LATADDR | LATADDR |

| DISD1 | RST_CFG9 | BUSWIDTH | 0 | 0 | 0 | 0 | 0 | 0 |

| DISD2 | RST_CFG10 | NANDPAGE1 | ||||||

| DISD3 | RST_CFG11 | NANDTYPE0 | ||||||

| DISD4 | RST_CFG12 | NANDTYPE1 | ||||||

| DISD5 | RST_CFG13 | NANDPAGE0 | ||||||

| DISD6 | RST_CFG14 | DECRYPT | DECRYPT | DECRYPT | DECRYPT | DECRYPT | DECRYPT | |

| DISD7 | RST_CFG15 | I-Cache | I-Cache | I-Cache | I-Cache | I-Cache | I-Cache | |

| VID1[0] | RST_CFG16 | Next Try | Next Try | Next Try | Next Try | |||

| VID1[1] | RST_CFG17 | Vbus_Level | ||||||

| VID1[2] | RST_CFG18 | Next Port | Next Port | Next Port | Next Port | |||

| VID1[3] | RST_CFG19 | Port_Num1 | Port_Num1 | Port_Num1 | Port_Num1 | |||

| VID1[4] | RST_CFG20 | USE_FS | USE_FS | USE_FS | ||||

| VID1[5] | RST_CFG21 | |||||||

| VID1[6] | RST_CFG22 | |||||||

| VID1[7] | RST_CFG23 | CORE_VOL TAGE | CORE_VOLTAG E | CORE_VOLTAG E | CORE_VOLTAG E | CORE_VOLT AGE | CORE_VOLTA GE |

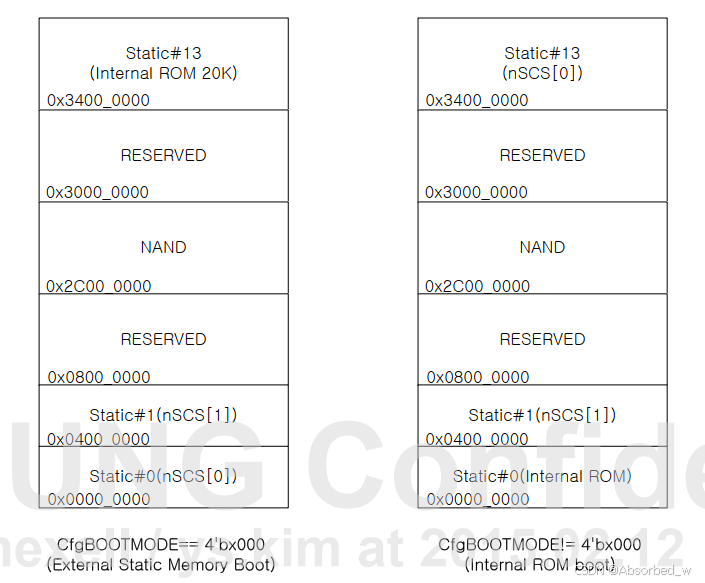

3.3 外部静态内存启动

3.4 内部ROM启动

芯片内置了20 KB的ROM。通过将系统配置中的CfgBOOTMODE设置为“0到2”,可以将内部ROM地址设置为第0地址。复位后,CPU从内部ROM的第0地址获取指令并执行。内部ROM包含支持各种启动方法的代码。此ROM代码通过读取各种介质的用户启动代码并将其加载到特定内存中来执行用户启动代码。这种启动方法定义为内部ROM启动(从现在起称为iROMBOOT)。

iROMBOOT使用内部SRAM存储堆栈或数据。因此,在执行iROMBOOT之后,内部SRAM的内容可能会发生变化。

3.4.1 特点

- 支持五种启动模式:SPI串行EEPROM启动、UART启动、USB启动、SDHC启动和带错误校正的NAND启动。

- 支持CPU异常向量重定向,以便在不使用MMU的操作系统中使用。

- 支持快速电源控制:将VDDPWRON和VDDPWRON_DDR设置为高电平。

3.4.2 内部ROM启动的系统配置

iROMBOOT支持五种启动模式,如USB启动、UART启动、SPI串行EEPROM启动、SDHC启动和带错误校正的NAND启动。每种启动模式通过参考SD[15:0]的复位状态来支持各种启动方法。下表显示了每种启动模式的系统配置。

| Pins | nexell / ys.kim atiRO2M0BO1OT5.02.12 | ||||||

| SDFS | UART | SPI Serial Flash | SDMMC | USB Device | NANDBOOT with Error Correction | ||

| RST_CFG[2:0] | BOOTMODE=1 | BOOTMODE=3 | BOOTMODE=4 | BOOTMODE=5 | BOOTMODE=6 | BOOTMODE=7 | |

| RST_CFG[12:11] | Don't care | NANDTYPE[1:0] | |||||

| RST_CFG[13, 10] | PAGESIZE[1:0] | ||||||

| RST_CFG[3] | SELCS | ||||||

| RST_CFG[17] | Don't care | OTG Session Check | Don't care | ||||

| RST_CFG[6] | Don't care | Baud Rate | Speed | Should be Zero | Don't care | ||

| RST_CFG[5:4] | Don't care | ADDRWIDTH[1:0] | Don't care | ||||

| RST_CFG[19, 3] | Port Number | ||||||

| RST_CFG[14] | DECRYPT | ||||||

| RST_CFG[15] | I-CACHE | ||||||

| RST_CFG[8] | LATADDR | ||||||

| RST_CFG[9] | Should be Zero (BUSWIDTH) | ||||||

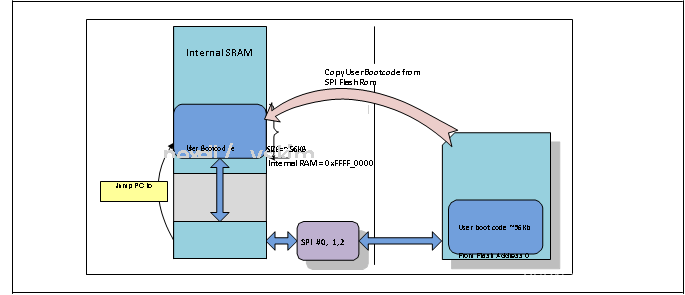

3.4.3 SPI 启动

iROMBOOT可以从SPI闪存ROM加载用户启动代码到内存并执行该代码,这种启动方法称为SPI启动(SPIBOOT)。

3.4.3.1 特点

- 支持地址步进2、3、4

- 启动速度为16 MHz

- 支持SPI端口0、1、2

- 最大启动大小为56 KB

- 检查启动签名和启动镜像CRC

3.4.3.2 操作

3.4.4 UART 启动

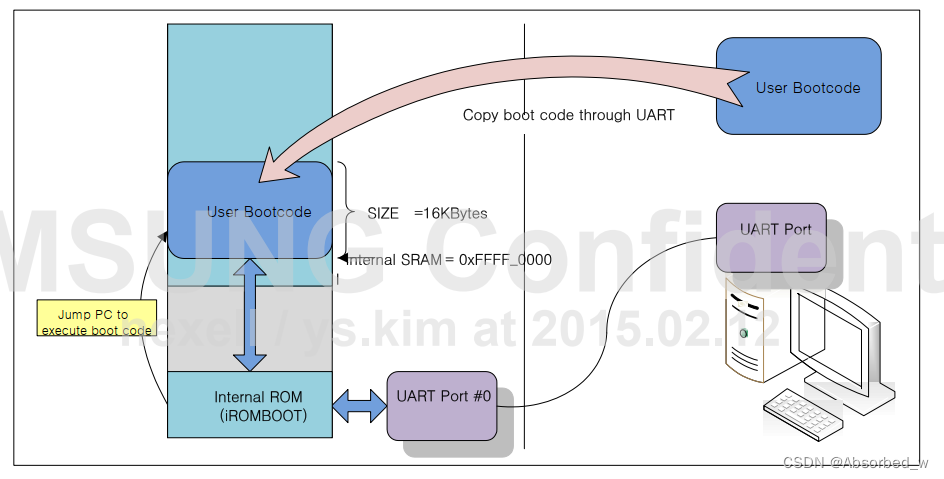

iROMBOOT可以通过UART将用户启动代码加载到内存并执行该代码,这种启动方法称为UART启动(UARTBOOT)。

3.4.4.1 特点

- 支持19200 bps、115200 bps。

- 支持UART端口0、1。

- 检查启动签名和启动镜像CRC。

3.4.4.2 操作

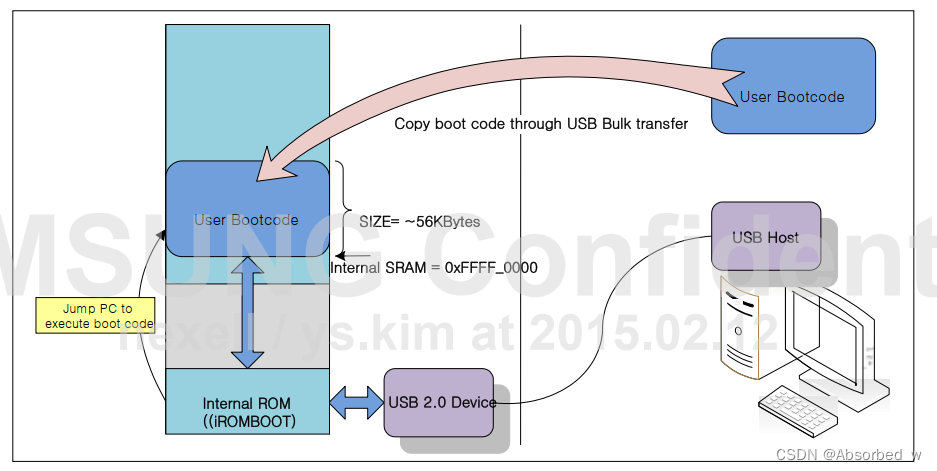

3.4.5 USB 启动

iROMBOOT可以通过USB将用户启动代码加载到内存并执行该代码,这种启动方法称为USB启动(USBBOOT)。

3.4.5.1 特点

- 支持全速或高速USB连接。

- 使用USB批量传输。

- 最大数据包大小为全速64字节和高速512字节。

3.4.5.2 操作

USB主机程序应通过USB设备的EP2端点使用批量传输来传输用户启动代码。最大数据包大小根据端点的USB连接速度可变。在全速连接中,USB主机程序可以以每个数据包最多64字节的速度传输数据包;在高速连接中,可以以每个数据包最多512字节的速度传输数据包。即使可以传输最大尺寸的数据包或小于最大尺寸的数据包,USB主机程序也应传输偶数大小的数据包。

USBBOOT从USB主机程序写入用户启动代码,并在接收到最大56 KB的用户启动代码后,通过将PC更改为0xFFFF0000来执行用户启动代码。

3.4.5.3 USB描述符

USB主机程序可以使用Get_Descriptor请求获取USBBOOT的描述符。表3-6显示了USBBOOT的描述符。USBBOOT有一个配置,一个接口,和两个附加端点(不包括控制端点)。然而,端点1仅为兼容性存在。因此,USBBOOT仅通过端点2接收数据。

详情见原文

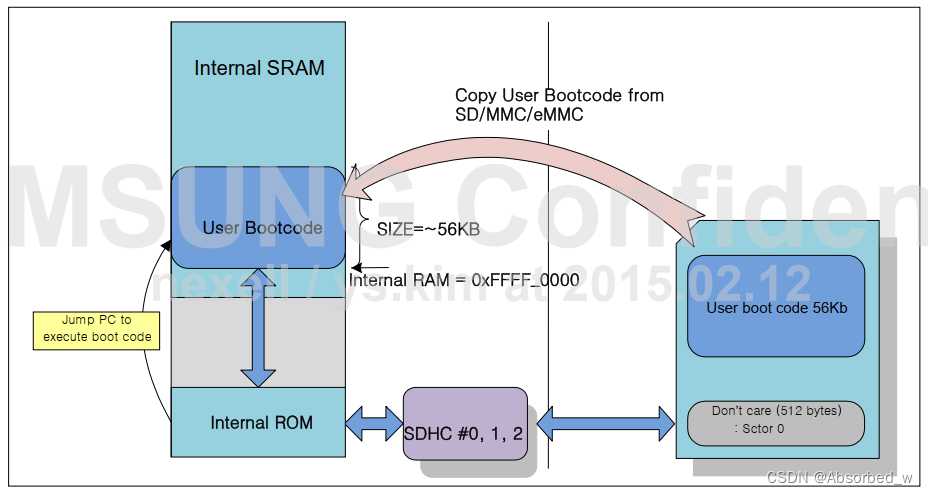

3.4.6 SDHC 启动

iROMBOOT可以通过SDHC模块从SD存储卡、MMC存储卡和eMMC读取用户启动代码并将其加载到内存中执行。这种方法称为SDHC启动(SDHCBOOT)。

3.4.6.1 特点

- 支持SD/MMC存储卡和eMMC

- 支持高容量SD/MMC存储卡

- 支持SD端口0、1、2

- 在识别阶段输出400 kHz SDCLK,在数据传输阶段输出24 MHz SDCLK

3.4.6.2 操作

SDHCBOOT 使用所有 SDHC #0、1、2 模块。

SDHCBOOT 提供了根据 CFG 引脚的各种启动方法,建议参考 [通过 RST_CFG 引脚的系统配置] 了解每种方法的规范。用户启动代码应按照下表写入存储设备以使用 SDHCBOOT。

| Sector | Name | Description |

| 0 | Reserved | SDHCBOOT不关心第0扇区的数据。因此,可以使用第0扇区存储MBR(主引导记录),并将用户启动代码和文件系统一起包含到一个物理分区中。 |

| 1 to 32 | User Bootcode | 用户制作的启动代码从第2扇区开始,大小约为56 KB。 |

SDHCBOOT启动过程如下:

- 当CfgSDHCBM为“0”时,执行正常的SDMMC启动。

- 进入空闲状态

- SDHCBOOT识别卡的类型并初始化。

- 卡的状态变为数据传输模式。

- SDHCBOOT从第1扇区读取用户启动代码,并将其加载到内部SRAM中执行。

3.4.7 SDFS 启动

iROMBOOT可以使用FAT32文件系统启动。只能使用SD卡的第一个分区作为FAT文件系统,分区名称字符串必须是"FAT32"。需要两个启动文件,一个是"NXDATA.SBH",另一个是"NXDATA.SBL"。首次启动时,读取MBR并搜索分区和文件系统。如果分区存在且文件系统为FAT32,则搜索第一个启动文件"NXDATA.SBH"。找到第一个文件后,搜索下一个启动文件"NXDATA.SBL"。NXDATA.SBL的最大大小为56 KB。

- 支持SD/MMC存储卡和eMMC

- 支持高容量SD/MMC存储卡

- 支持SD端口0、1、2

- 在识别阶段输出400 kHz SDCLK,在数据传输阶段输出24 MHz SDCLK

- 支持FAT12、FAT16、FAT32

- 不支持FAT32的长文件名

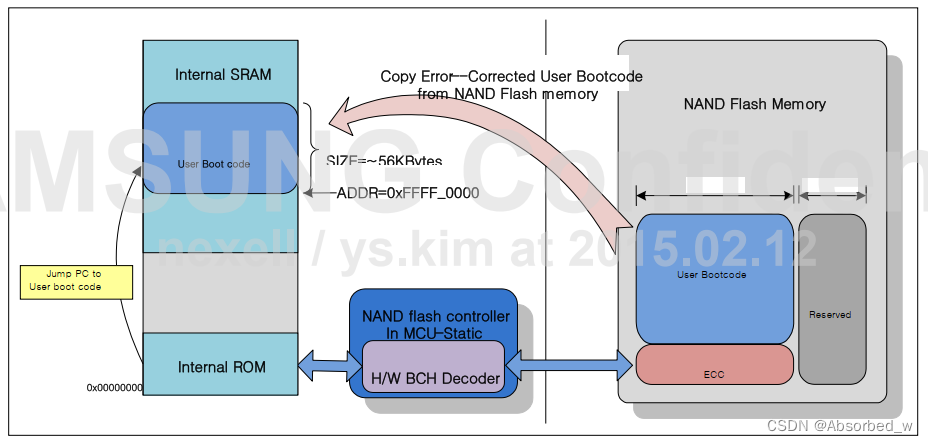

3.4.8 带错误校正的NAND启动

iROMBOOT提供了一种启动方法,可以校正存储在NAND闪存中的用户启动代码中的任何错误。这种启动方法称为带错误校正的NAND启动(简称为NANDBOOTEC)。

3.4.8.1 特点

- 支持每551字节最多24位错误的错误校正:用户启动代码512字节+校验39字节和每1129字节最多60位错误的错误校正:用户启动代码1024字节+校验105字节。

- 支持512B、2 KB、4 KB、8 KB、16 KB及以上作为NAND闪存的页面大小。

- 支持需要复位命令初始化的NAND闪存。

- 不支持坏块管理。

3.4.8.2 操作

NANDBOOTEC可以校正存储在NAND闪存中的用户启动代码中发生的错误。每当NANDBOOTEC以512字节或1024字节为单位从NAND闪存中读取用户启动代码时,它通过MCU-S中包含的硬件BCH解码器的错误检测功能,了解数据是否存在任何错误。如果数据中存在错误,通过硬件错误校正最多可以校正24个或60个错误。

3.4.8.3 如何将用户启动代码存储到NAND闪存中

下表显示了将用户启动代码写入NAND闪存中的格式。NANDBOOTEC使用NAND闪存的主存储区,不使用其备用区。

详情见原文

3.4.9 附加信息

3.4.9.1 启动头

所有启动(除了UART启动)都会检查512字节的启动头。这个启动头假定首先从启动设备接收或加载到SRAM的地址0xFFFF0000。首先,romboot在接收到的512字节启动头的末尾检查启动签名。这个签名值必须是0x4849534E。如果不相等,romboot会尝试下一个启动。此外,所有启动都必须包含有效的三个数据:LOADSIZE、LOADADDR和LAUNCHADDR。这些数据是关于第二启动镜像的信息。启动镜像的大小和加载地址必须以16字节对齐。如果是SPI启动,Romboot会检查CRC32。CRC是关于启动代码的,除了启动头以外。

启动头格式见原文

3.4.9.2 ALIVE电源控制

iROMBOOT在复位后将VDDPWRON和VDDPWRON_DDR引脚更改为高电平状态,以支持对nVDDPWRTOGGLE按钮的快速响应。表显示了iROMBOOT执行后的ALIVE模块状态。

| Function | State | Description |

| VDDPWRON | High | Enable Core Power |

| VDDPWRON_DDR | High | Enable DDR Memory Power |

3.4.9.3 异常向量重定向

ARM CPU的异常处理程序应按4字节依次存在于第0地址。用户通常将跳转到用户异常处理程序的例程放置在第0地址处的异常处理程序中。然而,在iROMBOOT的情况下,由于ROM存在于第0地址,用户的异常处理程序无法设置在第0地址。使用MMU时,可以通过将任意内存映射到第0地址来处理CPU异常。然而,iROMBOOT为不使用MMU的系统提供了异常处理程序重定向功能。

iROMBOOT使用内部SRAM的最低地址的32字节作为用户异常向量表。当发生异常时,iROMBOOT中的ROM异常处理程序让PC跳转到从用户异常向量表中获取的用户异常处理程序地址。因此,通过用户将用户异常处理程序的地址设置到内部SRAM中存在的用户异常向量表(即高向量地址),即使在物理地址系统中也可以处理异常。

3.4.9.4 CRC32 错误检查

UART和SPI启动使用CRC32进行检查,如果是UART启动,则在传输有效载荷的最后添加CRC32 FCS数据,然后CRC32 FCS检查将成功。在SPI启动中,CRC32数据必须插入启动头。

3.4.9.5 使用隐藏密钥进行AES128 ECB模式数据解密

所有启动模式的数据都可以选择使用隐藏密钥通过AES128 ECB模式进行解密。启动模式DISD6可以选择是否解密数据。

3.4.9.6 启动场景

如果任何设备启动失败,所有启动最终尝试USB启动。您可以选择在USB启动之前是否尝试从所有三个SD设备启动。并且可以选择SD原始扇区启动或SD文件系统启动。

3.4.9.7 多CPU启动

在上电启动时,只有CPU 0启动,CPU 1、2、3、4、5、6、7通过复位被锁定。可以通过CPU 0选择其他CPU的启动复位向量。因此,可以选择其他CPU在romboot或SRAM启动。

4 系统控制

4.1 概述

S5P6818的时钟大致分为FCLK、HCLK、MCLK、BCLK和PCLK,分别用于ARM CPU核心、AXI总线外设和APB总线外设。此外,BCLK是S5P6818系统总线的时钟,MCLK是SDRAM内存的时钟。S5P6818的两个PLL分别称为PLL0和PLL1。2-PLL和EXTCLK用于生成上述时钟(即FCLK、HCLK、PCLK、BCLK、MCLK)。所有PLL均设计为与24MHz的X-TAL输入一起操作。

4.2 特点

- 嵌入式4个独立运行的PLL

- 输出频率范围

- PLL0:40M至2.5 GHz(非抖动PLL)

- PLL1:40M至2.5 GHz(非抖动PLL)

- PLL2:35M至2.2 GHz(抖动PLL)

- PLL3:35M至2.2 GHz(抖动PLL)

- 频率通过可编程分频器(PDIV、MDIV、SDIV)进行更改

- 为芯片中的所有模块生成时钟

- 可以通过程序将PLL切换到掉电模式

- 支持32.768 kHz用于电源管理

- 各种掉电模式

- IDLE模式和STOP模式

- 各种唤醒源

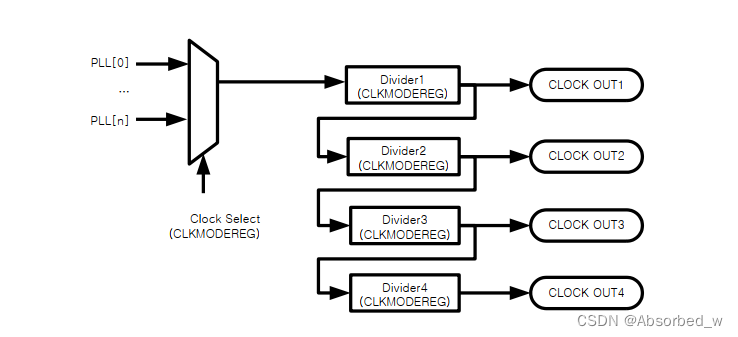

4.3 模块图

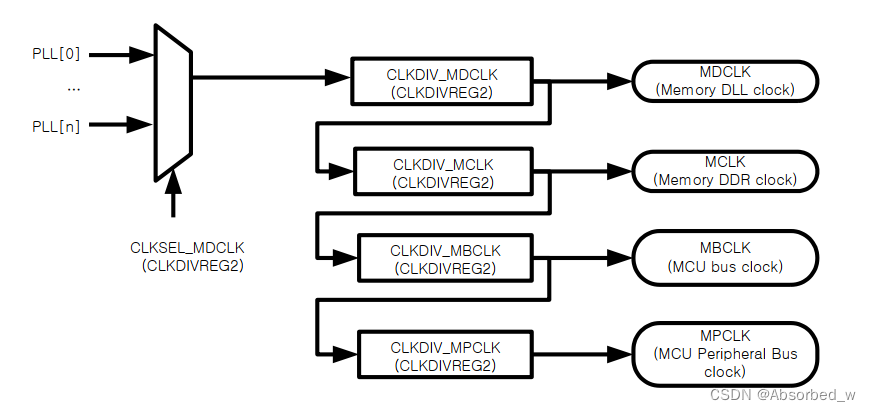

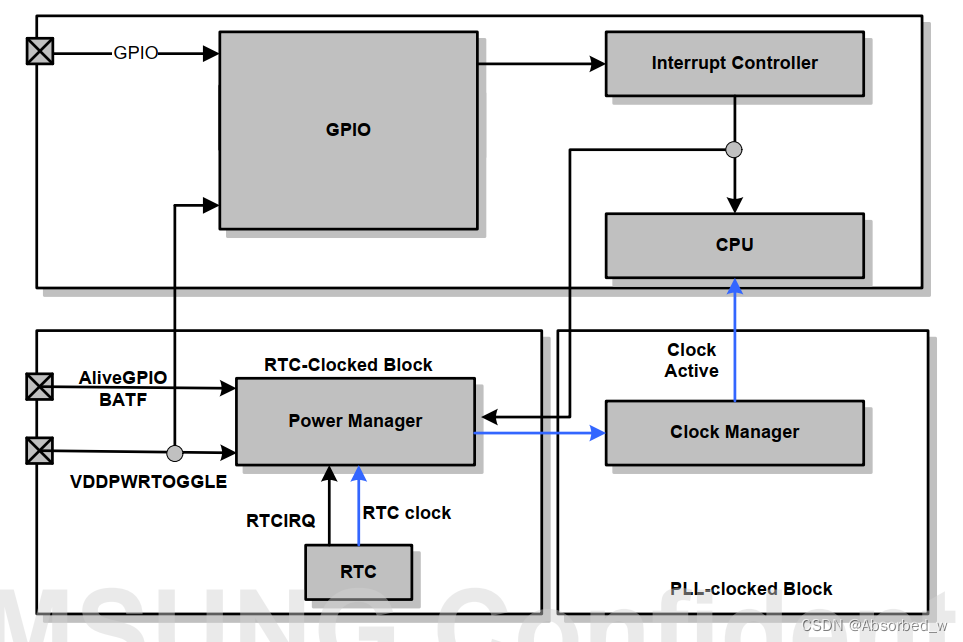

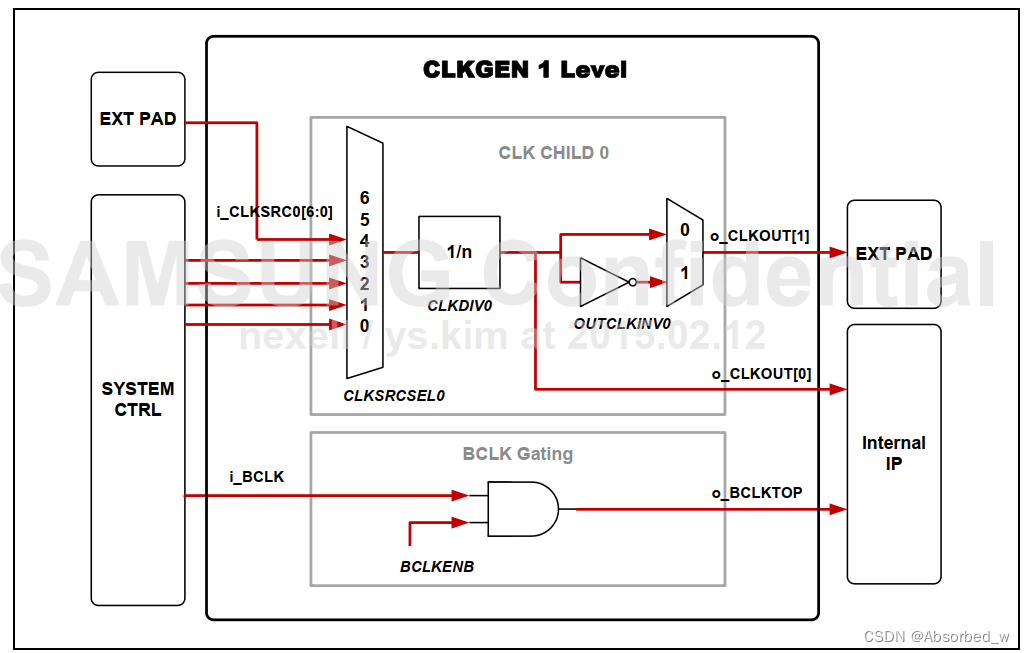

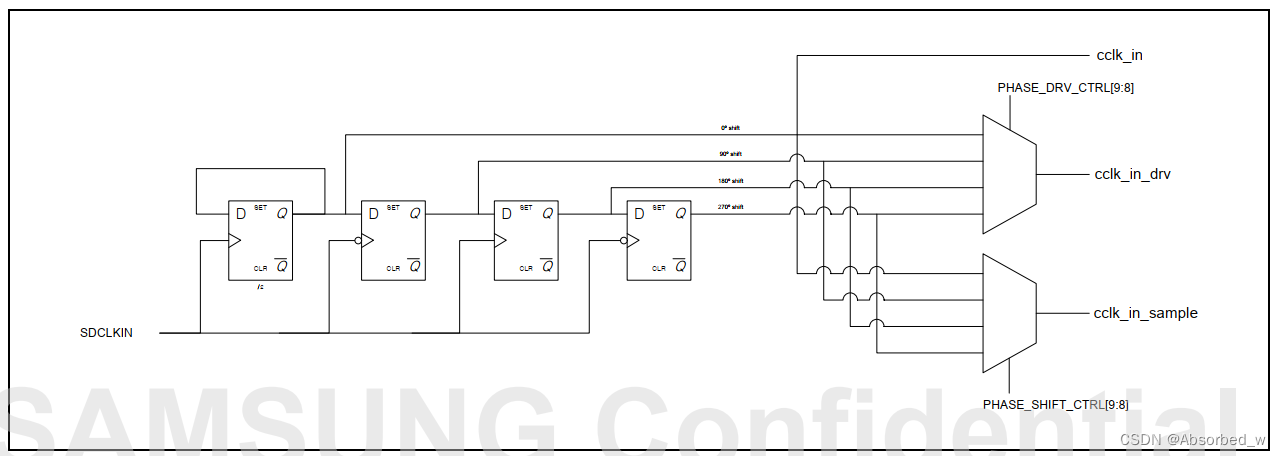

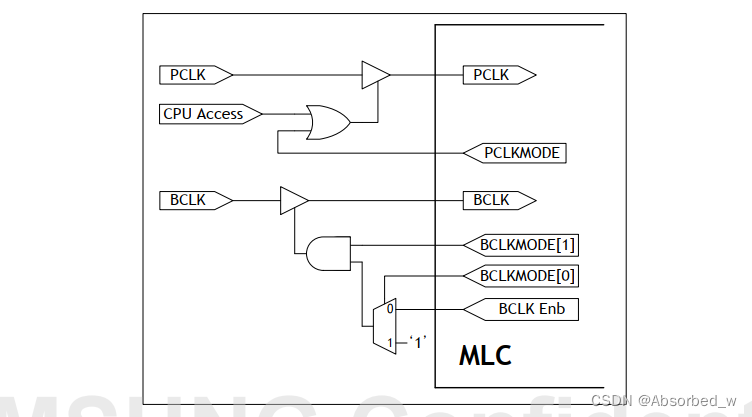

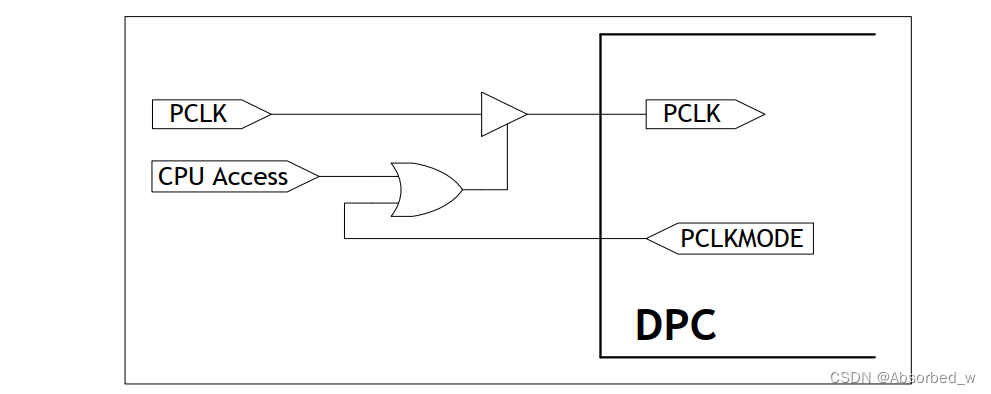

上述图示展示了S5P6818中时钟管理器的结构图。如图所示,S5P6818具有四个PLL。S5P6818接收这些PLL的输出,并生成所有系统时钟、内存时钟和CPU时钟,其输出频率从多个PLL中选择。

4.4 时钟管理器功能描述

4.4.1 PLL(锁相环)

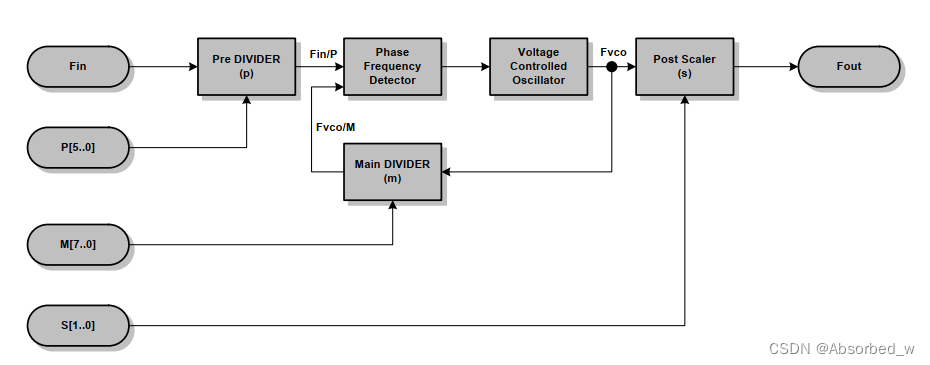

4.4.1.1 PMS值

从PLL结构的角度来看,上图显示了一个PLL的框图。Fin和Fout分别表示输入频率和输出频率。S5P6818具有多个PLL,可以通过使用每个PLL生成各种可编程时钟。

如果前分频器接收到24 MHz的Fin输入,它将Fin除以“P”。之后,相位频率检测器(PFD)比较Fin/P(参考时钟)和Fvco/M(反馈时钟)之间的差异。电压的幅度根据参考时钟和反馈时钟之间的比较结果的差异而变化。如果参考时钟比反馈时钟快,电压控制振荡器(VCO)的频率会根据差异增加。如果参考时钟比反馈时钟慢,VCO的频率会降低,并生成Fvco时钟。这是因为VCO的频率由电压值控制,起到加快或减慢时钟速度的作用。在此过程中,电压值由参考时钟和反馈时钟之间的差异决定。如果Fvco不是所需的时钟,通过主分频器重新生成反馈并在PFD中比较。这些步骤重复进行,直到参考时钟和反馈时钟相等。如果产生了合适的Fvco,通过后分频器的分频值生成最终的Fout时钟。最后,所需的时钟频率由p、m和s值决定。

如上所述,Fout可以通过Fin和p/m/s值来设置,指定p/m/s值的公式如下:(请注意,所有PLL0/1/2/3表示Fout。公式可能因情况而异。)

- PLL x = (m × Fin)/(p × 2^s)

- (x = 0,1,2,3, m = MDIV, p = PDIV, s = SDIV = 0, 1, 2, 3)

- PLL x的MDIV和PDIV值范围如下:

- MDIV值范围:64 ≤ MDIV ≤ 1023

- PDIV值范围:1 ≤ PDIV ≤ 63

PDIV和MDIV值应考虑VCO值和S5P6818的稳定操作来选择。S5P6818具有多个PLL,每个PLL具有不同的默认值和工作范围。

S5P6818的基本频率如下表所示:

| PLL | INITIAL FREQUENCY | RECOMMENDED FREQUENCY (Fvco) | RECOMMENDED FREQUENCY (Fout) | INITIAL PDIV/ MDIV/ SDIV VALUE | ||

| PDIV | MDIV | SDIV | ||||

| PLL0 | 550.000000Mhz | 1250 to 2500 MHz | 40 to 2500 MHz | 3 | 275 | 2 |

| PLL1 | 147.5 MHz | 1250 to 2500 MHz | 40 to 2500 MHz | 3 | 295 | 4 |

| PLL2 | 96 MHz | 40 to 2200 MHz | 1100 to 2200 MHz | 3 | 192 | 4 |

| PLL3 | 125 MHz | 40 to 2200 MHz | 1100 to 2200 MHz | 3 | 250 | 4 |

对于除CPU之外的所有模块,在更改PLL输出频率之前,应检查内存控制器的运行状态(运行/停止)。此外,在PLL更改(PLLSETREG0, PLLSETREG1)后,应将PLL更改位(PWRMODE.CHGPLL)设置为“1”。

PMSK设置指南

- p、m、s和k分别是P[5:0]、M[8:0]、S[2:0]和K[15:0]的十进制值。

- p = P[5:0],m = M[8:0],s = S[2:0],k = K[15:0]

- FFVCO和FFOUT按以下公式计算。

- FFVCO = ((m + k/65536) FFIN)/p

- FFOUT = ((m + k/65536) FFIN)/(p × 2^s)

- 虽然寄存器P[5:0]、M[8:0]和S[2:0]的范围是无符号整数,K[15:0]是二进制补码整数。

- 6’b00 0001 ≤ P[5:0] ≤ 6’b11 1111,且2 MHz ≤ FFREF(FFIN/p) ≤ 30 MHz

- 9’b0 0100 0000 ≤ M[8:0] ≤ 9’b1 1111 1111

- 3’b000 ≤ S[2:0] ≤ 3’b101

- 16’b1000 0000 0000 0000 ≤ K[15:0] ≤ 16’b0111 1111 1111 1111

- 当RESETB为逻辑高时,严格禁止将P[5:0]或M[8:0]设置为全零(6’b00 0000/9’b0 0000 0000)。

- 分频器的分频比由S[2:0]控制,具体如下表所示。

- 严格禁止将S[2:0]设置为下表中灰色行的值。

| S[2:0] | Division Ratio |

| 000 | 20 = 1 |

| 001 | 21 = 2 |

| 010 | 22 = 4 |

| 011 | 23 = 8 |

| 100 | 24 = 16 |

| 101 | 25 = 32 |

| 110 | Prohibited |

| 111 | Prohibited |

4.4.1.2 SSCG_EN、SEL_PF、MFR和MRR的设置指南

- 当SSCG_EN设置为逻辑高时,扩频模式启用。

- sel_pf、mfr和mrr分别是SEL_PF[1:0]、MFR[7:0]和MRR[5:0]的十进制值。

- sel_pf = SEL_PF[1:0],mfr = MFR[7:0],mrr = MRR[5:0]

- 调制频率(MF)由以下公式确定。

- MF = FFIN/p/mfr/25 Hz

- 调制率(MR)由以下公式确定。

- MR = mfr × mrr/m/26 × 100 %

- 调制模式由sel_pf确定。

- 00: 向下扩展

- 01: 向上扩展

- 1x: 中心扩展

- 寄存器范围。

- 8’b0000 0000 ≤ MFR[7:0] ≤ 8’b1111 1111

- 6’b00 0001 ≤ MRR[5:0] ≤ 6’b11 1111

- 0 ≤ mrr × mfr ≤ 512

- 2’b00 ≤ SEL_PF[1:0] ≤ 2’b10

详情见原文

4.4.1.5 PLL掉电

S5P6818支持PLL掉电模式以最小化功耗。例如,如果所有系统时钟都由PLL0生成且不需要使用PLL1,则无需向PLL1供电。在这种情况下,S5P6818将PLL1切换到掉电模式以减少功耗。然而,PLL0不能进入掉电模式。通过向CLKMODEREG0.PLLPWDN1写入“1”可以实现PLL0掉电。

4.4.2 更改PLL值

当CPU需要更改PLL分频值时,在将PLL设置复位(PLLSETREG0, PLLSETREG1)设置为适当的值后,必须将PLL更改位(PWRMODE.CHGPLL bit)设置为1。

电源管理和时钟控制器模块在更改PLL分频值时会阻塞时钟供应,因为PLL在更改分频值时是不稳定的。在锁定时间之后,这些模块会重新供应时钟。CPU必须检查这些模块是运行还是停止,如STOP模式。

4.4.3 时钟生成器

4.4.3.1 时钟摘要

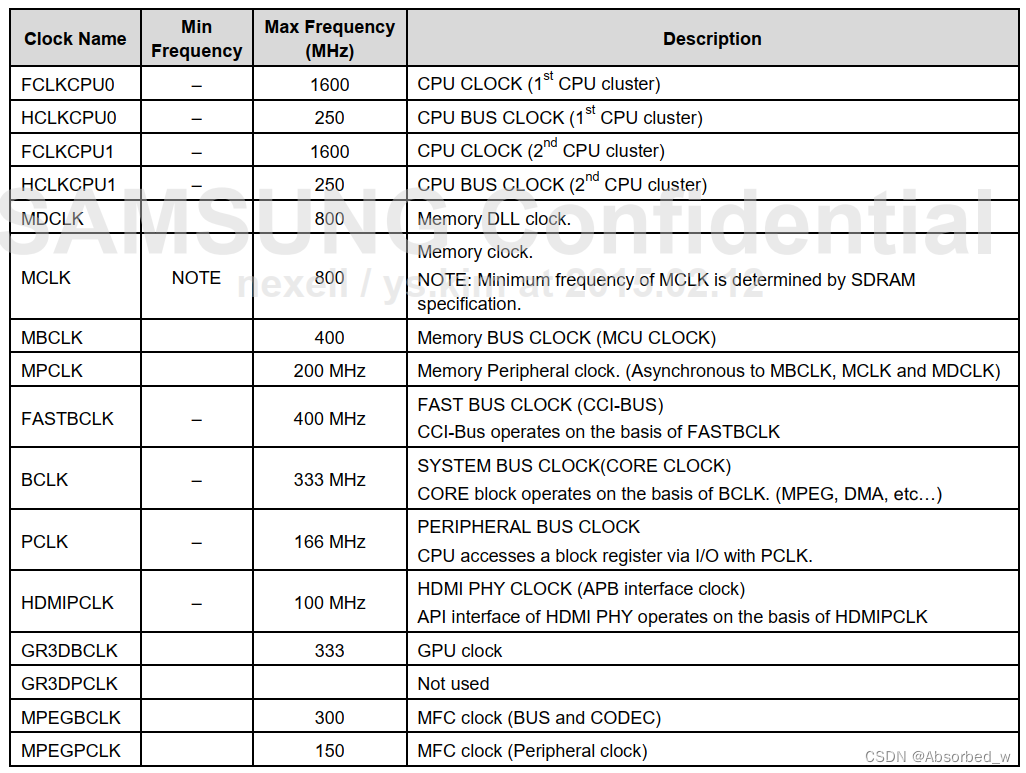

S5P6818中生成的5个时钟及每个时钟的最大频率列在下表中。最小频率不受PLL可生成的时钟频率限制。

4.4.3.2 CPU0 时钟

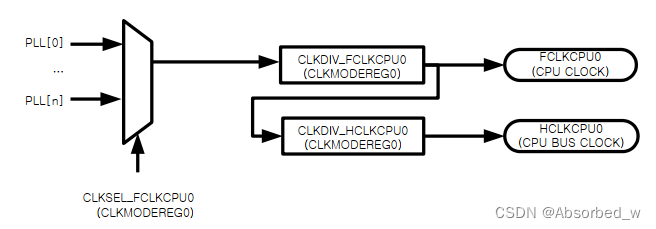

在上图中,显示了一个创建供给FCLKCPU0的时钟的框图,FCLKCPU0是S5P6818的主CPU。CLKMODEREG0从多个PLL中选择所需的PLL输出。使用从所选PLL创建的时钟,CLKDIV_FCLKCPU0寄存器和CLKDIV_HCLKCPU0生成供给CPU核心模块的FCLKCPU0和供给AXI总线时钟的HCLKCPU。请注意不要将HCLKCPU设置为超过最大速度。FCLKCPU和HCLKCPU的频率不能相同。

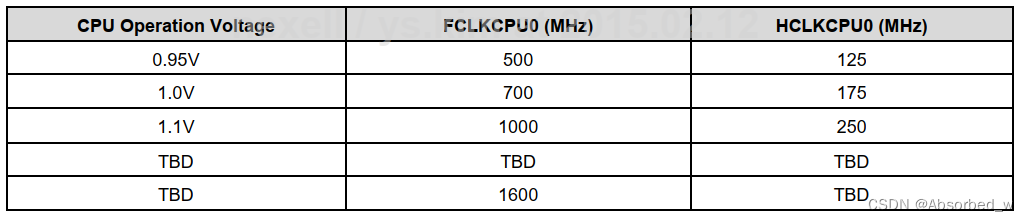

任何PLL都可以用于生成CPU时钟,但推荐使用PLL0,推荐的时钟频率如下:

4.4.3.3 系统总线时钟(核心时钟)

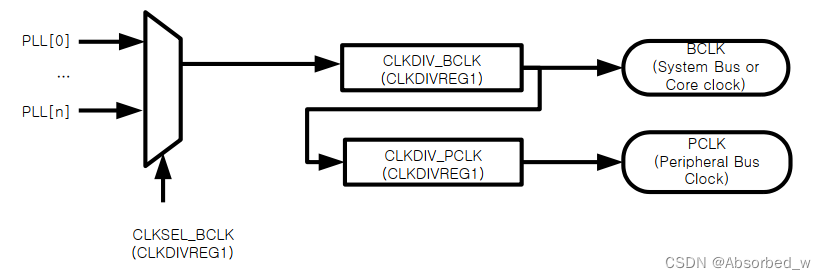

系统总线时钟(BCLK)用作核心时钟。系统总线时钟称为[BCLK],BCLK的一半时钟称为[PCLK]。BCLK用于所有SOC核心操作。PCLK在CPU通过I/O访问每个块寄存器时使用。因此,不应将PCLK应用于未使用的块。每个块都有PCLK启用/禁用寄存器。PCLK应用的块(请参阅各部分)。这些寄存器决定PCLK是否仅在CPU访问相应块寄存器时应用,还是始终应用。

时钟频率比例应如下:

| Mode | BCLK (MHz) | PCLK (MHz) |

| Max operation | 333 | 166 |

4.4.3.4 内存总线时钟(MCU时钟)

内存总线时钟(MCLK)用作SDRAM和MCU核心时钟。MDCLK是内存控制单元(MCU)的DLL时钟。MCLK是DDR接口时钟。MBCLK是MCU的总线时钟。MPCLK是MCU的外设总线时钟。MCLK的频率应是MBCLK频率的两倍。(BCLK与MCLK的比率为1:2)

| Mode | MDCLK (MHz) | MCLK (MHz) | MBCLK (MHz) | MPCLK (MHz) |

| Fast | 800 (NOTE) | 800 | 400 | 200 |

| Slow | 800 | 200 | 100 | 50 |

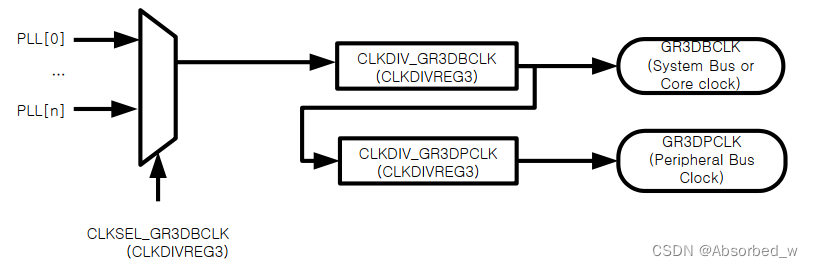

4.4.3.5 GPU(图形处理单元)时钟

GPU时钟(GR3DBCLK)用作GPU核心时钟。GR3DPCLK未使用(保留)。推荐的时钟频率如下:

| Mode | GR3DBCLK (MHz) | GR3DPCLK (MHz) |

| Max operation. | 333 | 166 (not used) |

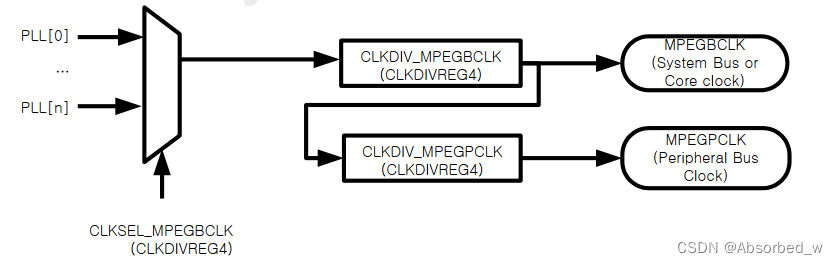

4.4.3.6 MFC(多功能编解码器)时钟

MFC时钟(MPEGBCLK)用作多功能编解码器时钟。MPEGPCLK用作MFC单元的外设总线时钟。

推荐的时钟频率如下:

| Mode | MPEGBCLK (MHz) | MPEGPCLK (MHz) |

| Max operation | 300 | 150 |

4.5 电源管理器

4.5.1 电源管理器概述

S5P6818的电源管理器提供以下功能,以确保系统稳定运行并减少功耗。

- 上电顺序

- 复位生成

- 电源管理

- 更改PLL值

电源管理器的主要功能是控制上电顺序,使S5P6818在系统供电后保持稳定,并有效管理电源。此外,它还控制初始操作中的复位配置。

此外,该模块生成各种复位信号,例如外部复位输出(nRSTOUT)、AliveGPIO复位和软复位。

- S5P6818提供多种掉电模式以减少系统功耗。S5P6818提供的三种电源模式如下:

- 正常模式

- 空闲模式(IDLE Mode)

- 停止模式(STOP Mode)

- 睡眠模式(SLEEP Mode)(详见“ALIVE”部分的睡眠模式)

4.5.2 电源降耗模式操作

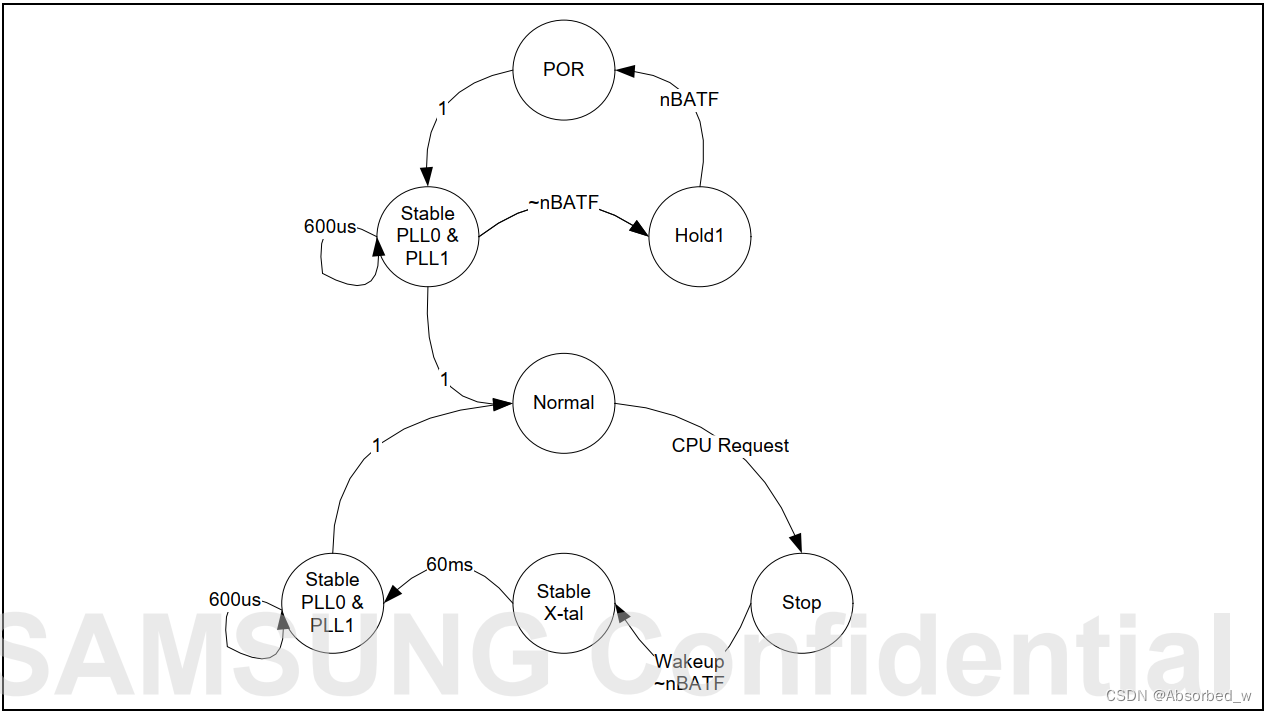

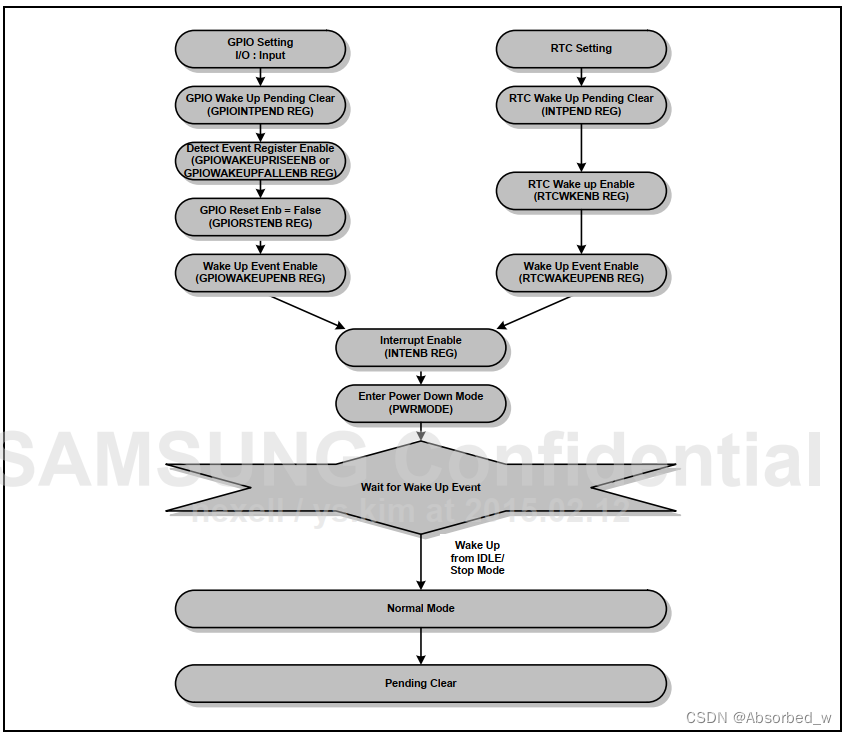

下图显示了电源管理模块的状态图。该图示了每种电源降耗模式的进入条件以及所有唤醒条件。

-

S5P6818 状态

- POR: 上电复位状态

- StablePLL: 等待PLL锁定时间

- NORMAL: 正常操作状态

- STOP: 停止操作模式

- StableX-tal: 等待晶体稳定振荡

- Hold: 等待nBATF=高电平

-

唤醒源

- SWRST: 软件复位

- SWRSTEN: 软件复位使能

- ALIVEGPIOEvent: ALIVE GPIO唤醒事件

- CPUIRQ: 来自CPU的中断(IDLE模式)

- RTCIRQ: 来自RTC的中断

- BAFT: 电池故障

- VDDPWRTOGGLE: VDDPWRTOGGLE开关按钮

- WRST: 看门狗复位

4.5.2.1 IDLE模式

在IDLE模式下,除CPU时钟外,所有模块的电源和时钟均正常供应,从而可以减少一些功耗。要进入IDLE模式,需要将PWRMODE.IDLE寄存器设置为“1”。在IDLE模式下,CPU时钟不供应,但电源正常供应,PLL正常运行。

唤醒源可以使用由中断控制器生成的所有S5P6818中断:GPIO中断、ALIVE GPIO中断、外部中断和RTC中断。唤醒源的中断应在进入IDLE模式之前启用。CPU在IDLE模式中被唤醒后立即返回到之前的状态。

4.5.2.2 STOP模式

在STOP模式下,包括ARM核心在内的所有模块都不供应时钟,因为如果不供应时钟,PLL也不会在时钟控制器中运行。然而,S5P6818在进入STOP模式之前将DRAM转换为自刷新模式以保护内存数据。与IDLE模式一样,需要将PWRMODE.STOP设置为“1”以进入STOP模式。

在STOP模式下,唤醒源有所限制。可用的唤醒源包括RTC中断、ALIVE GPIO中断等。唤醒源受到限制,因为除电源管理器和RTC模块外,不向所有其他模块供应时钟。由于RTC模块使用独立的电源和时钟,因此只有由RTC时钟生成的中断可以用作唤醒源。

与IDLE模式不同,当系统在STOP模式中被唤醒时,所有PLL都会停止运行,因此系统不能立即返回到之前的状态。因此,唤醒时间比IDLE模式长约70毫秒,以稳定内部PLL。

| Power Down Mode | Power Supply | CPU Clock Supply | Other Clock Supply | SDRAM Mode | Wake Up Condition |

| IDLE Mode | ON | OFF | ON | NORMAL | RTC Interrupt, AliveGPIO Interrupt, All Interrupt to Interrupt Controller, External IRQ |

| STOP Mode | ON | OFF | OFF | Self Refresh | RTC Interrupt, AliveGPIO Interrupt |

4.5.2.3 睡眠模式1和睡眠模式2

请参阅“ALIVE”部分了解睡眠模式1和睡眠模式2的详细信息。

上图显示了进入电源降耗模式和唤醒过程的顺序。首先,唤醒源选择所需的事件(中断)并指定事件的属性。如果唤醒源是GPIO,则将设置更改为输入并执行挂起清除。此外,检测到指定的事件(中断)的状态并将软件复位使能设置为False以应对最坏情况(如果硬件未实现软件复位使能开关,则无需指定为False)。最后,系统启用相关中断(如果使用中断)并进入电源降耗模式。

在这种电源降耗模式下,S5P6818等待唤醒事件(中断)。如果发生唤醒事件(中断),S5P6818返回正常模式并在软件层面清除相关的中断挂起。

4.5.2.4 GPIO作为唤醒源

GPIO可用于所有电源降耗模式。然而,由于内部电源和时钟状态在各个电源模式下不尽相同,因此在每种电源模式下的操作状态会有所不同。

如上图所示(唤醒模块图),电源管理器使用不同的时钟。由于RTC时钟始终供应给电源管理器模块,因此PADs(GPIO引脚)可以用作唤醒源。

在电源降耗模式下唤醒过程的描述如下:

-

IDLE模式下的唤醒 在IDLE模式下,除CPU时钟外,其他模块的时钟和电源正常供应。因此,GPIO接收到的输入会应用于中断控制器并唤醒CPU。

-

STOP模式下的唤醒 在STOP模式下,除RTC时钟外,所有时钟(包括PLL和XTI)都不供应。中断控制器在STOP模式下不工作。这时,如果信号输入到电源管理器,电源管理器首先唤醒时钟管理器。由于这一唤醒,所有时钟(如PLL和PCLK、BCLK、MCLK和FCLK)被启用并供应给CPU和整个系统。换句话说,系统被唤醒。为了稳定PLL,唤醒时间比IDLE模式长约70毫秒。

4.6 复位生成

4.6.1 上电复位序列

电源管理块具有复位生成块。复位生成块使用在RTC时钟(32.768 kHz)下采样的nPORST。RTC时钟作为电源管理的主时钟使用。因此,即使不使用RTC功能,也必须供应RTC时钟。

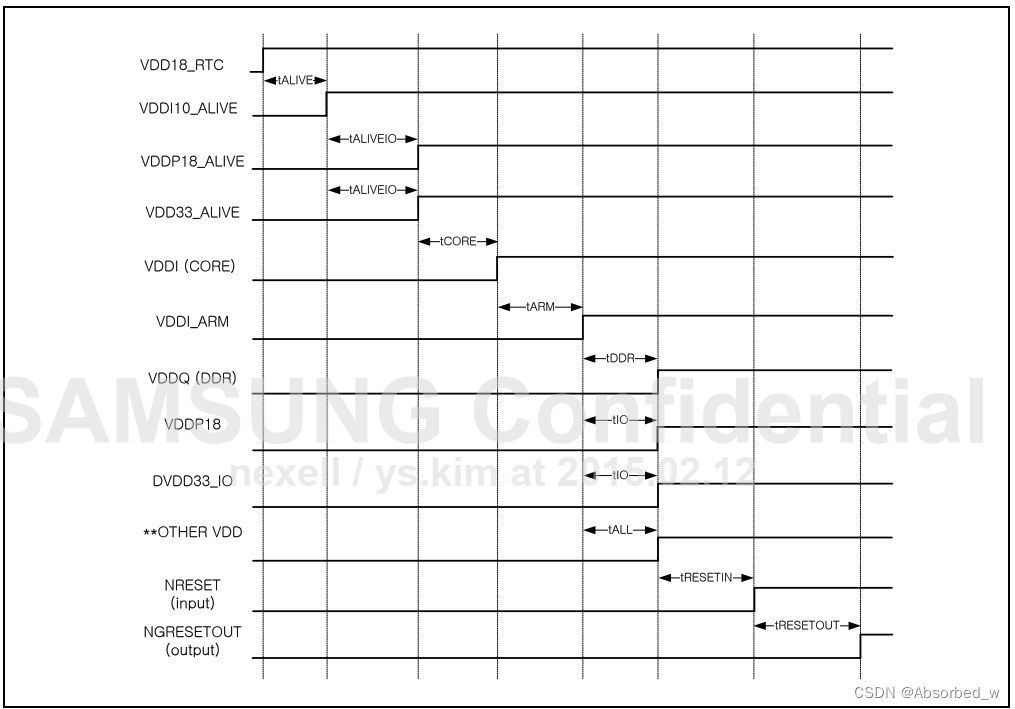

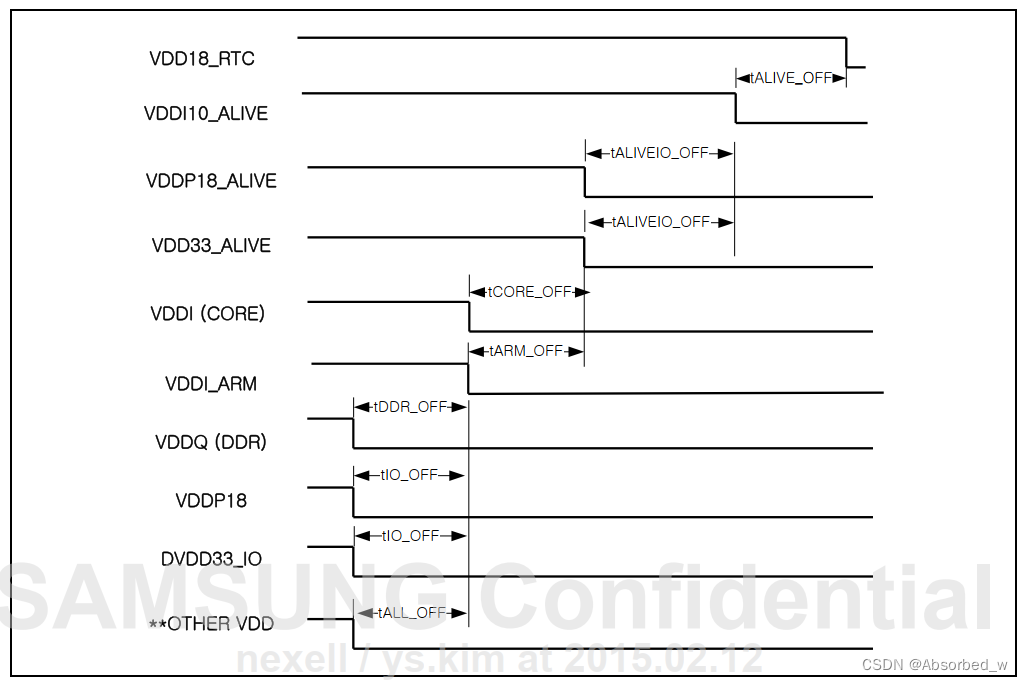

下图显示了上电复位序列期间的时钟和复位行为。

| Symbol | Min. (msec) | Max. (msec) | Description |

| tALIVE | –50 | Infinity | RTC to VDDI10_ALIVE |

| tALIVEIO | 0 | 50 | VDDI10_ALIVE to ALIVE IO power |

| tCORE | 0 | Infinity | VDDP18_ALIVE/VDD33_ALIVE to VDDI |

| tARM | 0 | 50 | VDDI to VDDI_ARM |

| tDDR | 0 | 150 | VDDI_ARM to VDDQ (DDR IO power) |

| tIO | 0 | 150 | VDDI_ARM to DVDD33_IO (normal IO power) |

| tALL | 0 | 150 | VDDI_ARM to DVDD33_IO (normal IO power) |

| tRESETIN | 0 | Infinity | All power on to assert nRESET |

| tRESETOUT | 200 | 200 | NRESET to NGRESETOUT |

4.6.2 睡眠模式唤醒序列

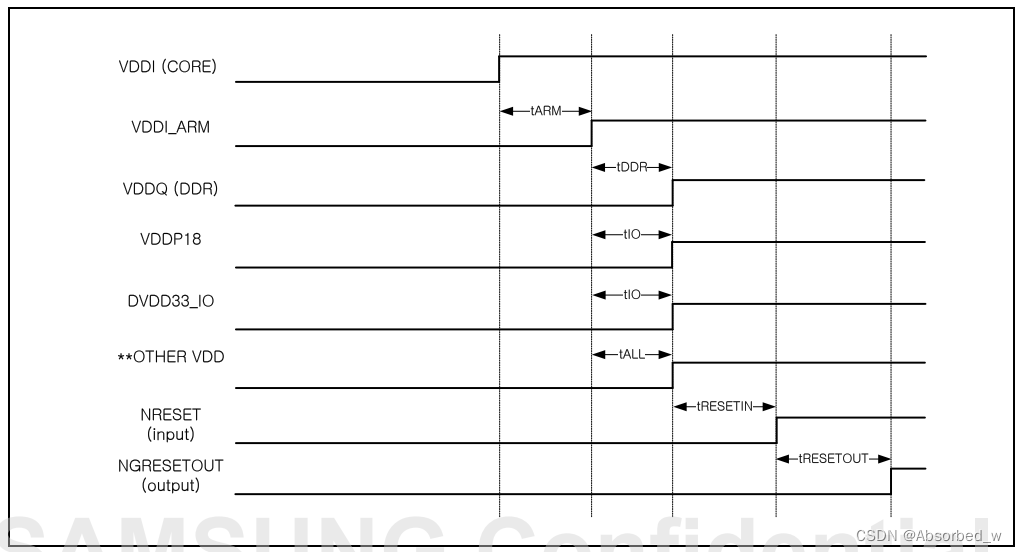

在启动睡眠模式唤醒序列之前,所有ALIVE和RTC电源应开启。

| Symbol | Min. (msec) | Max. (msec) | Description |

| tARM | 0 | 50 | VDDI to VDDI_ARM |

| tDDR | 0 | 150 | VDDI_ARM to VDDQ (DDR IO power) |

| tIO | 0 | 150 | VDDI_ARM to DVDD33_IO (normal IO power) |

| tALL | 0 | 150 | VDDI_ARM to DVDD33_IO (normal IO power) |

| tRESETIN | 0 | Infinity | All power on to assert nRESET |

| tRESETOUT | 200 | 200 | NRESET to NGRESETOUT |

4.6.3 关机序列

| Symbol | Min. (msec) | Max. (msec) | Description |

| tALIVE_OFF | –50 | Infinity | ALIVE IO power to ALIVE CORE |

| tALIVEIO_OFF | 0 | 50 | ALIVE IO power to ALIVE core power |

| tCORE_OFF | 0 | Infinity | VDDI to ALIVE power |

| tARM_OFF | 0 | Infinity | VDDI_ARM to ALIVE power |

| tDDR_OFF | 0 | 50 | VDDQ(DDR IO power) to VDDI |

| tIO_OFF | 0 | 50 | DVDD33_IO (normal IO power) to VDDI |

| tALL_OFF | 0 | 50 | Other VDD power to VDDI |

4.6.4 软件复位和GPIO复位

S5P6818支持软件复位,CPU可以通过软件复位自我复位。要生成软件复位,必须先将SWRSTENB位设置为1,然后再设置PWRMODE.SWRST位。与上电复位不同,软件复位请求在稳定状态下进行,因此不需要时钟稳定时间。

S5P6818支持用户定义的GPIO复位。当定义为GPIO复位源的AliveGPIO引脚被置位或复位时,电源管理模块会生成复位信号。定义为GPIO复位源的AliveGPIO引脚在唤醒源寄存器中定义。将GPIORSTENB位设置为1启用AliveGPIO复位源功能。

4.6.5 看门狗复位

看门狗定时器模块用于在控制器操作受到系统错误等故障干扰时恢复操作。当电源管理模块检测到看门狗定时器事件时,它生成与上电复位完全相同的复位信号,因为看门狗复位事件发生在故障和未知状态下。

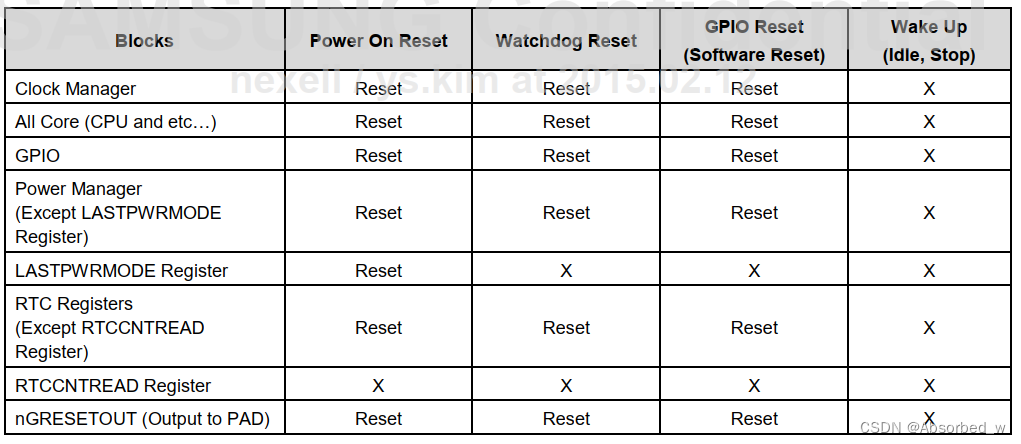

4.6.6 nPORST、软件复位、看门狗复位和GPIO复位

S5P6818有以下四种复位状态:

4.7 TIE OFF

Tieoff块是一组寄存器,包括在正常模式操作中不需要设置的特殊寄存器。Tieoff块包括用于ARM、HDMI、DRAM控制器、UART、USB 2.0主机控制器/Phy、USB 2.0 OTG控制器/Phy、以太网控制器、AXI总线和内部SRAM时序裕量控制的特殊功能寄存器。

4.8 AXI总线

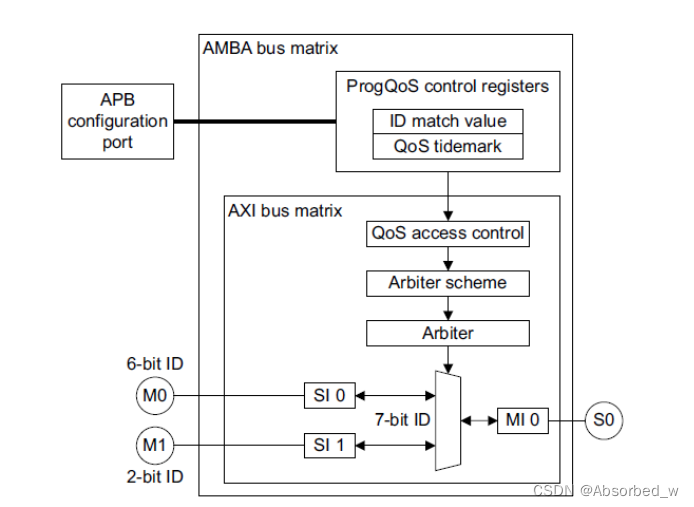

ARM PL301(AXI3总线互连)为AXI总线提供可编程功能,其中包括QoS和可编程循环优先级。

4.8.1 可编程服务质量(ProgQoS)

QoS方案通过跟踪未完成事务的数量工作,当达到指定数量时,仅允许来自特定指定主控的事务。

QoS方案仅支持具有组合接受能力的从控,如PrimeCell动态内存控制器(PL340)。

直到AXI总线矩阵计算出在特定MI处存在与QoS标高寄存器中存储的值相等数量的未完成事务时,QoS方案才会生效。然后,它仅接受来自QoS访问控制寄存器中指定的从端口的事务。此限制将一直保持,直到未完成事务的数量再次小于QoS标高寄存器中存储的值。

建议将需要QoS支持的MI分配低MI编号。这种方法与循环优先级方案很好地对齐,因为需要QoS支持的MI通常是可以被认为是高排名从控的那些。详见PrimeCell高性能矩阵(PL301)技术参考手册。

4.8.2 仲裁方案

可以分别为每个MI配置可编程或固定的循环优先(RR)仲裁方案。

AW和AR通道有独立的仲裁器,可以通过APB编程接口进行编程(如果适用)和单独查询,但AW和AR通道配置是相同的。由于AW和AR通道是独立仲裁的,MI可以允许来自不同SI的同时读写事务。

仲裁机制记录仲裁决策,以便在随后的周期中使用。当前周期内做出的仲裁决策不会影响当前周期。

如果没有SI处于活跃状态,仲裁器采用默认仲裁,即最高优先级SI。如果这种情况发生,并且最高优先级接口在同一周期内或在任何其他SI之前变为活跃状态,则这不构成对活跃SI的授权,仲裁方案也不会因该传输而改变其状态。

如果启用了QoS规定并且处于活跃状态,则仅允许某些SI赢得仲裁,不能保证默认仲裁在这些SI中。在这种情况下,不允许任何事务使用默认仲裁,必须在有活跃SI时进行仲裁。

4.8.2.1 RR方案

在这些方案中,您可以在设计时选择:

- 使用的槽数

- 分配给它们的SI

- 它们的顺序

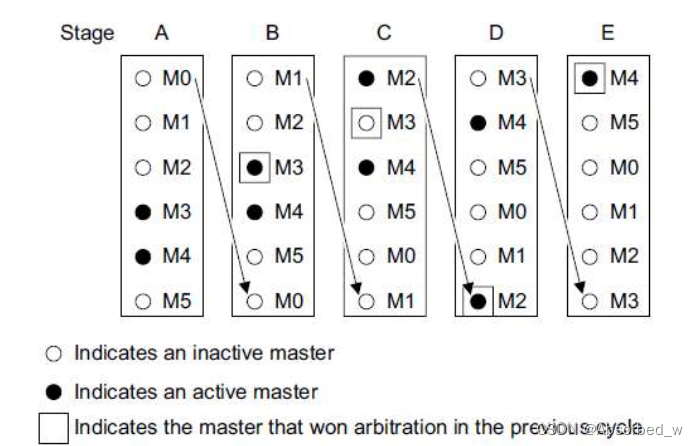

每个连接的SI至少有一个槽,最多可以有32个槽。通过为SI分配多个槽,您可以按槽数的比例分配对从端的访问。如果槽的顺序适当,这也可以减少在保证授权之前的最长时间。如果选择可编程的RR方案,可以通过APB编程接口查询并更改与槽关联的SI。

每当仲裁授权给一个活跃SI时,槽会轮换,以使当前处于最高优先级位置的槽成为最低优先级,所有其他槽移动到更高优先级,但保持它们的相对顺序。这意味着,如果一个SI是最高优先级的活跃SI,但不是最高优先级接口,那么它会继续赢得仲裁,直到它成为最高优先级接口,然后成为最低优先级接口。

由于仲裁值是已注册的,本周期内做出的仲裁决策将在下一个周期中使用。这意味着,如果当前持有仲裁权的SI在本周期内仍然是最高优先级活跃SI,它将再次赢得仲裁,无论它在下一个周期内是否活跃,如下图A、B和C阶段所示的M3状态。

4.9 寄存器描述

4.9.1 寄存器映射摘要

- 基地址:0XC001_0000

详情见原文

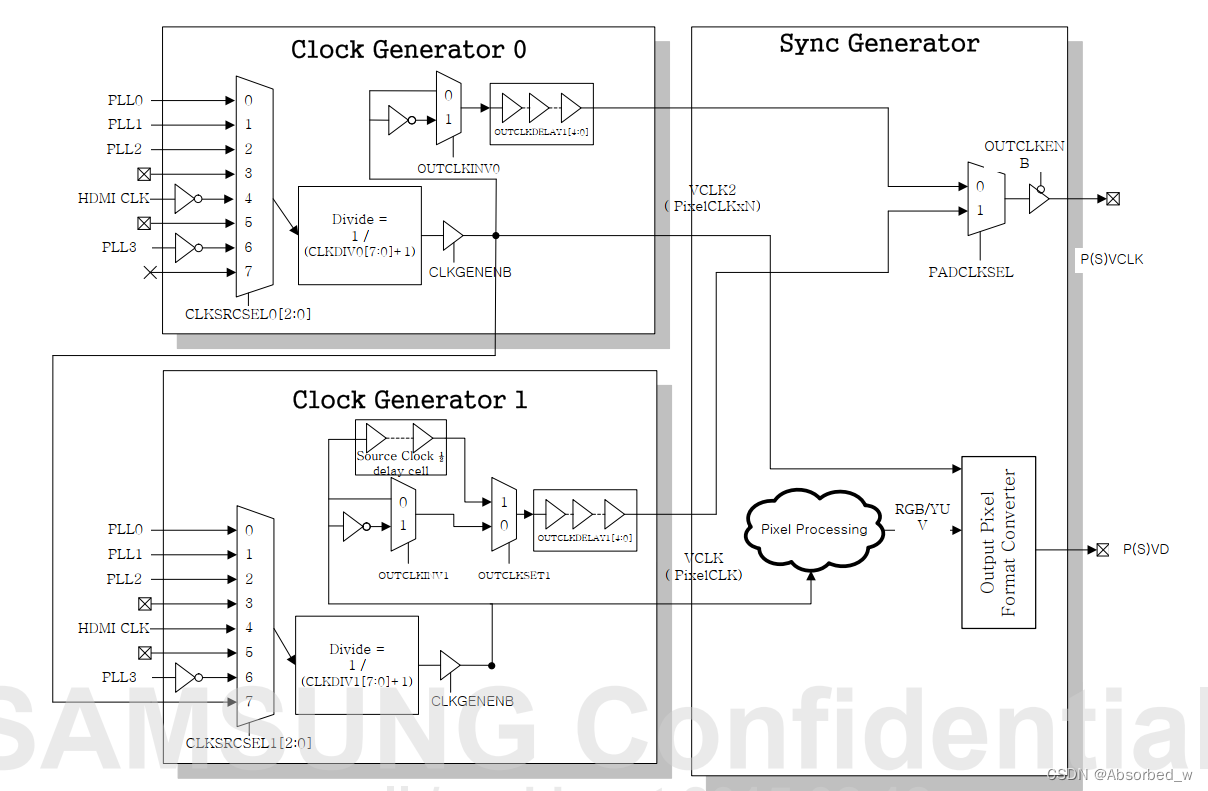

5 时钟生成器

5.1 IP时钟生成器概述

IP时钟生成器可以生成分频时钟。每个IP都有时钟方案,同时需要几个不同的分频比。因此,每个IP时钟生成器为各个IP提供所需的时钟。这些IP时钟生成器使用来自SYSCTRL的PLL或来自PAD的外部时钟。它可以通过2-n分频器对每个IP的所需时钟进行分频。

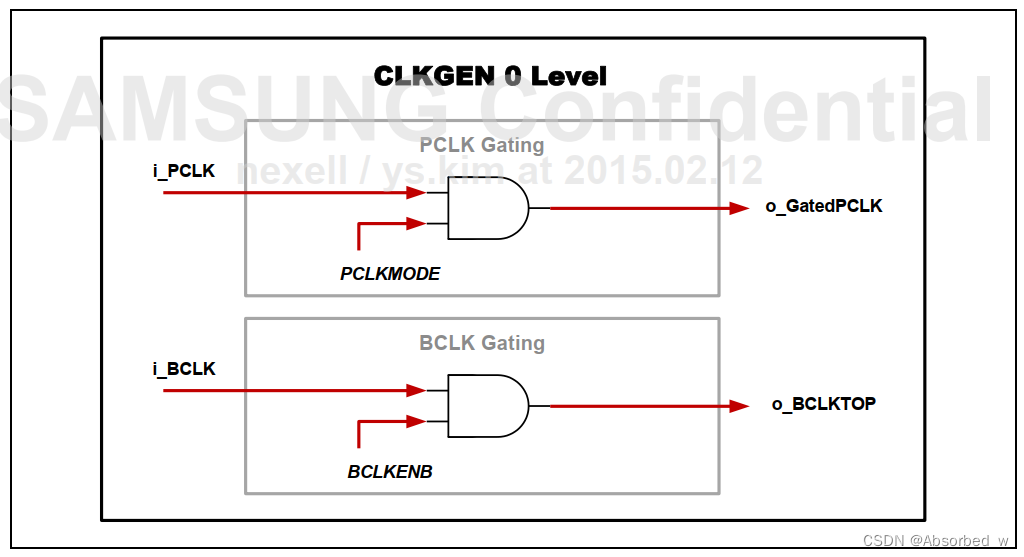

5.2 时钟生成器等级0

时钟生成器等级0没有时钟分频器。它只能进行时钟门控。它使用PCLK或BCLK门控。以下外设使用等级0时钟生成器:

- CODA960

- Crypto

- I2C

- 3D GPU

- MPEGTSI

- PDM

- SCALLER

- DEINTERLACE

- MLC

寄存器描述见原文

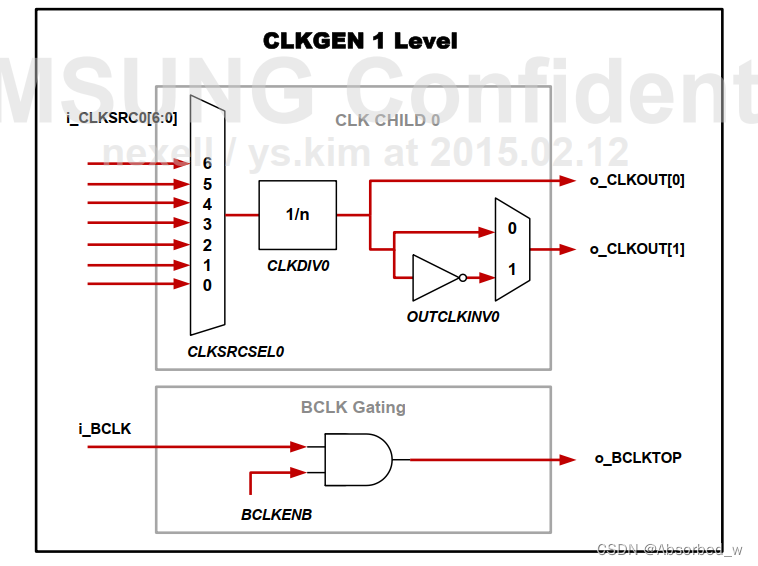

5.3 时钟生成器等级1

时钟生成器等级1有一个时钟分频器。时钟分频器具有8位分频寄存器。分频寄存器可以达到256级,可以进行最多256级分频。

以下外设使用等级1时钟生成器:

- MIPICSI

- PPM

- PWMTIMER

- SDMMC

- SPDIFTX

- SSP

- UART

- VIP

寄存器描述见原文

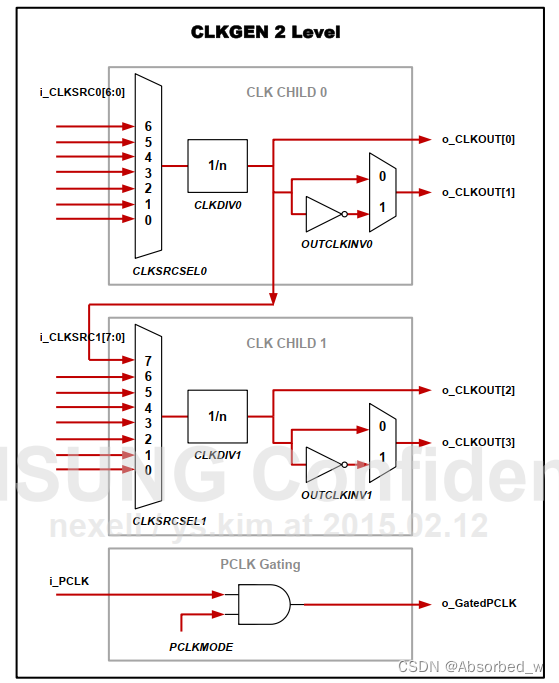

5.4 时钟生成器等级2

时钟生成器等级2有两个时钟分频器。每个时钟分频器具有8位分频寄存器,每个寄存器可以达到256级分频,两个时钟分频器串联,因此时钟生成器等级2可以进行最多65,536级分频。

以下外设使用等级2时钟生成器:

- GMAC

- I2S

- USBHOSTOTG

- DPC

- LVDS

- HDMI

- MIPIDSI

寄存器描述见原文

6 总线

6.1 概述

ARM PL301 提供 AXI3 总线、AHB 总线和 APB 总线。

AXI3 总线互连提供 AXI 总线的可编程功能,包括 QoS 和可编程循环优先。

CCI-400(缓存一致互连)将互连和一致性功能结合在一个模块中。

6.2 特点

- 顶部总线:AXI 总线,主 1 通道,辅 4 通道

- 底部总线:AXI 总线,主 1 通道,辅 4 通道

- 显示总线:AXI 总线,主 1 通道,辅 2 通道

- 静态总线:AXI 总线,主 2 通道,辅 3 通道

- IOPER 总线:AXI 总线,主 3 通道,辅 4 通道

- SFR 总线:AXI 总线,主 3 通道,辅 2 通道

- SFR0 总线:AXI 到 APB 总线,辅 1 通道

- SFR1 总线:AXI 到 APB 总线,辅 1 通道

- SFR2 总线:AXI 到 APB 总线,辅 1 通道

- CCI 总线:AXI 主 3 通道,AXI 辅 5 通道

6.3 描述

6.3.1 AXI 总线描述

ARM PL301(AXI3 总线互连)提供 AXI 总线的可编程功能,包括 QoS 和可编程循环优先。

6.3.2 可编程服务质量(ProgQoS)

QoS 方案通过跟踪未完成事务的数量工作,当达到指定数量时,仅允许来自特定指定主控的事务。

QoS 方案仅支持具有组合接受能力的从控,如 PrimeCell 动态内存控制器(PL340)。在 AXI 总线矩阵计算出在特定 MI 处存在与 QoS 标高寄存器中存储的值相等数量的未完成事务之前,QoS 方案没有效果。然后,它仅接受来自 QoS 访问控制寄存器中指定的从端口的事务。此限制将一直保持,直到未完成事务的数量再次小于 QoS 标高寄存器中存储的值。

建议将需要 QoS 支持的 MI 分配低 MI 编号。这种方法与循环优先方案很好地对齐,因为需要 QoS 支持的 MI 通常是可以被认为是高排名从控的那些。详见 PrimeCell 高性能矩阵(PL301)技术参考手册。

寄存器描述见原文

7 TrustZone 保护控制器 (TZPC)

7.1 概述

TZPC(TrustZone 保护控制器)控制 PL301 AXI 总线的信任区。

每个 AXI 到 APB 桥提供一个 AXI 从接口,并可以调解其本地 APB 总线上多达 16 个外设的访问。桥包含地址解码逻辑,根据传入的 AXI 事务生成 APB 外设选择。桥包括每个总线上的外设的单个 TZPCDECPROT 输入信号。该信号用于确定外设是否配置为安全或非安全;桥将拒绝非安全事务对安全外设地址范围的访问。

7.2 特点

- 7 个 TZPC 模块

- 每个 TZPC 模块提供 TZPCDECPROT0、TZPCDECPROT1、TZPCDECPROT2、TZPCDECPROT3、TZPCR0SIZE

寄存器描述见原文

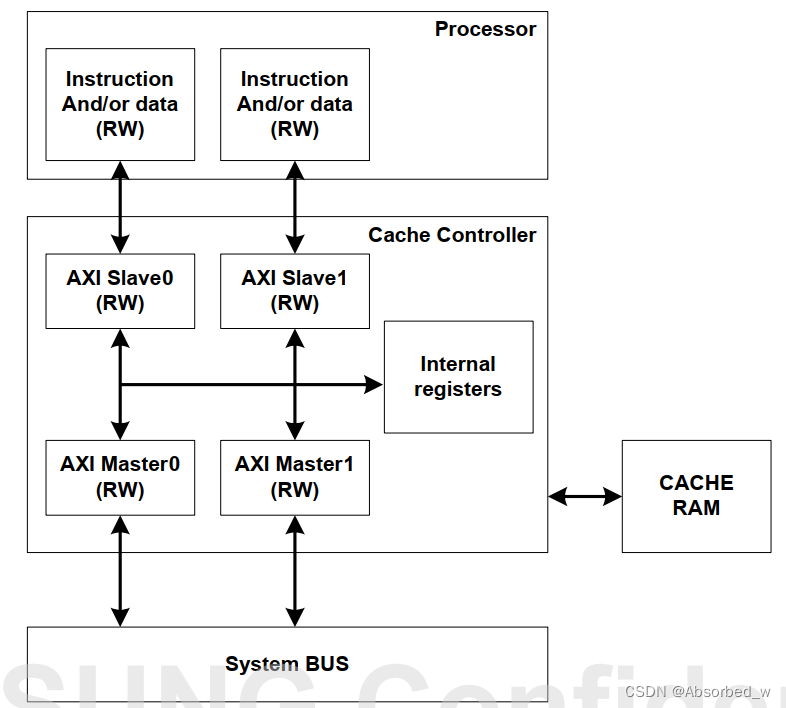

8 系统L2缓存(PL-310 L2C)

8.1 概述

在片上添加二级缓存,也称为L2缓存,是在处理器生成大量内存流量时提高ARM系统性能的公认方法。二级缓存假定存在一级或一级缓存,紧密耦合或内部处理器。

内存访问速度最快的是L1缓存,其次是L2缓存。L3主内存的内存访问通常明显较慢。

8.2 特点

缓存控制器的特点:

- 为高性能系统设计的从属和主AMBA AXI接口。

- 支持C格式锁定,用于数据和指令。

- 支持按行锁定。

- 支持按主ID锁定。

- L2缓存可用大小可配置为16 KB到8 MB,具体取决于配置和锁定寄存器的使用。

- 固定行长度为32字节、8字或256位。

- 与数据RAM的接口是字节可写的。

- 支持所有AXI缓存模式:

- 写通和写回

- 读分配、写分配、读写分配。

- 强制写分配选项始终将可缓存写入分配到L2缓存,用于不支持此模式的处理器。

- 正常内存不可缓存共享读取被视为可缓存不可分配。正常内存不可缓存共享写入被视为可缓存写通不可写分配。有一个选项,Shared Override,可覆盖此行为。

- 支持关键字优先行填充。

- 伪随机或循环优先受害者选择策略。使用锁定寄存器可以使其确定性。

- 四个256位行填充缓冲区(LFB),由主端口共享。这些缓冲区从主内存捕获行填充数据,等待完整行写入L2缓存。

- 每个从端口有两个256位行读取缓冲区(LRB)。这些缓冲区在L2内存中持有一行缓存命中。

- 三个256位驱逐缓冲区(EB)。这些缓冲区持有从L2缓存驱逐的行,写回主内存。

- 三个256位存储缓冲区(STB)。这些缓冲区在排空到主内存或L2缓存之前持有可缓冲写入。它们允许将多个写入合并到同一行。

- 软件选项启用独占缓存配置。

- 配置寄存器可通过从端口中的地址解码访问。

- 主端口中的地址过滤允许将某一地址范围重定向到一个主端口,而所有其他地址重定向到另一个端口。

8.3 模块图

8.4 功能描述

8.4.1 L2缓存用户配置

- 系统L2缓存基地址:基地址:0xCF000000

- 关闭和开启L2C:

- 关闭偏移:0x100(基地址 + 0x100)设置为0

- 开启偏移:0x100(基地址 + 0x100)设置为1

- 早期写响应:

- AXI协议规定,只有当最后一个写数据被接受时,写响应才能发送回AXI主控。此优化使L2C-310能够在存储缓冲区接受写地址后立即发送某些写事务的写响应。这种行为与AXI协议不兼容,默认情况下禁用。可以通过在辅助控制寄存器的位[30]中设置Early BRESP Enable位来启用此优化。L2C-310从端口仅在输入信号AWUSERSx[11],x=0或1,对于相应的写事务设置为1'b1时发送早期写响应。

8.4.2 初始化顺序

例如,典型的缓存控制器启动编程顺序包括以下寄存器操作:

- 使用读-修改-写操作写入辅助、标签RAM延迟、数据RAM延迟、预取和功率控制寄存器,以设置全局配置:

- 关联性,方式大小

- RAM访问的延迟

- 分配策略

- 预取和功率功能

- 使用偏移0x77C进行安全写操作,按方式无效所有缓存条目:

- 向0x77C写入0xFFFF

- 轮询缓存维护寄存器,直到无效操作完成

-

如果需要,写入锁定D和锁定I寄存器9。

-

写入中断清除寄存器以清除任何残留的原始中断。

-

如果需要启用中断,写入中断掩码寄存器。

-

将最低有效位设置为1写入控制寄存器1以启用缓存。

如果在启用L2缓存的情况下写入辅助、标签RAM延迟或数据RAM延迟控制寄存器,将导致SLVERR错误。必须在写入辅助、标签RAM延迟或数据RAM延迟控制寄存器之前,通过写入控制寄存器1禁用L2缓存。

寄存器描述见原文

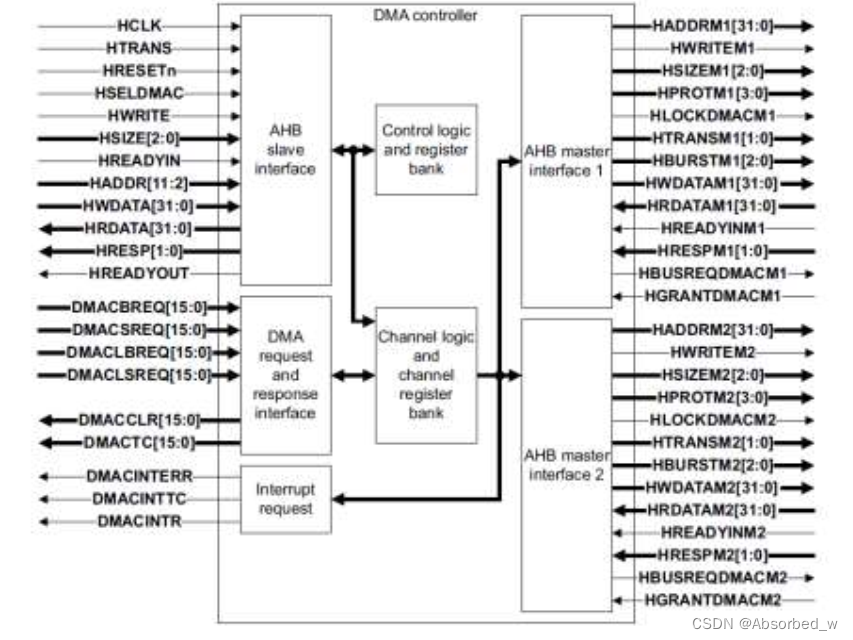

9 DMA

9.1 概述

DMA控制器(DMAC)是一个高级微控制器总线架构(AMBA)模块,连接到高级高性能总线(AHB)。DMAC有一个用于编程的AHB从接口和两个用于数据传输的AHB主接口。S5P6818中有两个DMAC,每个DMAC有八个通道,每个通道最多可以缓冲4个字。每个通道可以通过任一AHB主接口以编程的数据宽度和字节序传输数据。DMAC支持16个DMA请求者,并为每个通道生成单独可屏蔽的终端计数和传输错误中断。

9.2 特点

- 16个DMA通道。每个通道可以支持单向传输。

- 16个DMA请求。DMAC提供16个外设DMA请求线路。

- 单个DMA和突发DMA请求信号。连接到DMAC的每个外设可以发出突发DMA请求或单个DMA请求。您可以通过编程DMAC设置DMA突发大小。

- 内存到内存、内存到外设、外设到内存和外设到外设的传输。

- 通过使用链接列表支持散播或收集DMA。

- 硬件DMA通道优先级。每个DMA通道有特定的硬件优先级。DMA通道0具有最高优先级,通道7具有最低优先级。如果两个通道的请求同时变为活跃,优先处理具有最高优先级的通道。

- AHB从DMA编程接口。您可以通过AHB从接口写入DMA控制寄存器来编程DMAC。

- 两个用于传输数据的AHB总线主接口。当DMA请求变为活跃时,使用这些接口传输数据。

- 源和目的地址的递增或不递增寻址。

- 可编程DMA突发大小。您可以编程DMA突发大小以更有效地传输数据。突发大小通常设置为外设FIFO大小的一半。

- 每个通道内部有四字FIFO。

- 支持8、16和32位宽的事务。

- 支持大端和小端模式。DMAC在复位时默认为小端模式。

- 分离和组合的DMA错误和DMA计数中断请求。您可以在发生DMA错误或DMA计数达到0时生成对处理器的中断。这通常用于指示传输已完成。有三个中断请求信号:

- DMACINTTC表示传输已完成。

- DMACINTERR表示发生了错误。

- DMACINTR结合了DMACINTTC和DMACINTERR中断请求信号。在中断控制器请求输入较少的系统中可以使用DMACINTR中断请求。

- 中断屏蔽。您可以屏蔽DMA错误和DMA终端计数中断请求。

- 原始中断状态。在屏蔽之前,您可以读取DMA错误和DMA计数的原始中断状态。

- 用于块和集成系统级测试的测试寄存器。

- 唯一标识DMAC的识别寄存器。操作系统可以使用这些寄存器自动配置自己。

9.3 模块图

9.4 功能描述

9.4.1 软件注意事项

在编程DMAC时,必须考虑以下软件注意事项:

- 在通道使能为高后,不得对活动通道的寄存器进行任何写操作。如果需要重新编程任何DMAC通道参数,必须在禁用DMAC通道后重新编程。

- 如果源宽度小于目标宽度,传输大小值乘以源宽度必须是目标宽度的整数倍。

- 当源外设是流控制器且源宽度小于目标宽度时,源外设在断言DMACLSREQ或DMACLBREQ之前执行的传输次数必须使得传输次数乘以源宽度是目标宽度的整数倍。如果违反此条件,数据可能会卡在FIFO中并丢失,导致不可预测的结果。可以通过禁用相关DMAC通道来中止传输。

- 不得将DMACCxCONFIG寄存器中的SRCPERIPHERAL和DESTPERIPHERAL位字段编程为大于15的值。

- DMACCxCONTROL寄存器中的SWIDTH和DWIDTH位字段不得表示超过32位宽的外设。

- 在软件通过清除DMACCxCONFIG寄存器中的通道使能位禁用通道后,必须在轮询相应的DMACENBLDCHNS寄存器位为0后才能重新使能该位。这是因为实际禁用不会立即发生在清除通道使能位时。必须考虑进行中的AHB突发的延迟。

- DMACCxLLIREG寄存器中的LLI字段不得表示大于0xFFFFFFF0的地址,否则四字LLI突发将在0x00000000处回绕,并且LLI数据结构不在连续的内存位置。

- 当DMAC中编程的传输大小大于源或目标外设中FIFO的深度时,必须仅将DMAC编程为非递增地址生成。

- 外设在接收DMACCLR信号时应取消断言任何DMACSREQ、DMACBREQ、DMACLSREQ或DMACLBREQ信号,无论DMACCLR是响应哪个请求断言的。这是因为DMACCLR不是针对单个请求信号、DMACSREQ或突发请求信号DMACSBEQ的。DMACCLR的握手通过DMAC中的所有DMA请求的逻辑OR实现。 注意:当DMACCLR为高时,外设发出新的DMACSREQ或DMACBREQ信号是非法的。

- 如果在DMACCxCONTROL寄存器中将传输大小字段编程为零,并且DMAC是流控制器,则传输大小字段在其他流控制模式下没有意义,那么通道不会启动任何传输。必须通过写入DMACCxCONFIG寄存器中的通道使能位来禁用该通道,并重新编程该通道。

- 不得对DMACCxCONTROL寄存器进行正常的读写测试,因为传输大小字段不是典型的写回读寄存器字段。在写入时,传输大小位字段类似于控制寄存器,因为它确定DMAC执行的传输次数。然而,在回读时,传输大小表现为状态寄存器,因为它返回以源宽度表示的剩余传输次数。因此,当传输大小回读时,它返回存储在称为TRFSIZEDST的单独计数器中的目标传输完成数乘以一个因子。不是对同一个物理寄存器进行写入和读出,因此不适用正常的写回读测试。

- 在目标流控制模式下,执行外设到外设的传输,如果通道FIFO中有足够的数据来服务由目标外设引发的DMACLSREQ或DMACLBREQ请求,而不需要从源外设获取数据,那么源外设会收到DMACTC。

- 在目标流控制情况下,执行外设到外设传输,且DWIDTH < SWIDTH时,目标外设请求的数据字节数必须是以字节表示的SWIDTH的整数倍。如果不确保这一点,DMAC可能会从源外设获取比所需更多的数据。这可能导致数据丢失。

- 在低优先级通道的访问结束时,在AHB总线上插入一个空闲周期,以使其他主控能够访问总线。这确保了低优先级通道不会垄断总线。然而,这意味着在最坏的情况下,总线可能被对应于低优先级的事务占用最多16个周期。这适用于所有传输配置,包括内存到内存的传输。 注意:当DMACCLR为高时,外设发出新的DMACSREQ或DMACBREQ信号是非法的。

9.4.2 程序员模型

9.4.2.1 关于程序员模型

DMAC支持以下类型的事务:

- 内存到内存

- 内存到外设

- 外设到内存

- 外设到外设

每个DMA流配置为提供单源和目标的单向DMA传输。

例如,一个双向串行端口需要一个流用于发送,一个流用于接收。源和目标区域可以是内存区域或外设,可以通过相同的AHB主控访问,或一个区域由每个主控访问。

DMAC的基地址不是固定的,可能因具体系统实现而异。然而,任何特定寄存器相对于基地址的偏移是固定的。

寄存器字段

以下适用于DMAC使用的寄存器:

- 不得访问保留或未使用的地址位置,因为这可能导致设备行为不可预测。

- 必须将寄存器的保留或未使用位写为零,并在读取时忽略这些位,除非相关文本中另有说明。

- 除非相关文本中另有说明,系统或上电复位会将所有寄存器位复位为逻辑0。

- 除非相关文本中另有说明,所有寄存器都支持读写访问。写入更新寄存器内容,读取返回寄存器内容。

- 除非相关文本中另有说明,仅可使用字读取和字写入访问此文档中定义的寄存器。

启用DMAC

通过在DMAC配置寄存器中设置DMA使能位E来启用DMAC。

禁用DMAC

要禁用DMAC:

-

读取DMACENBLDCHNS寄存器,确保已禁用所有DMA通道。如果有任何通道处于活动状态,请参见禁用DMA通道。

-

通过在DMAC配置寄存器中写入0来禁用DMAC。

启用DMA通道

通过在相关DMA通道配置寄存器中设置通道使能位来启用DMA通道。

注意:必须在启用通道之前完全初始化通道。此外,必须在启用任何通道之前设置DMAC的使能位。

禁用DMA通道

可以通过以下方式禁用DMA通道:

-

直接写入通道使能位。

注意:如果使用此方法,会丢失FIFO中任何未完成的数据。

-

将活动位和暂停位与通道使能位结合使用。

-

等到传输完成。然后通道会自动禁用。

禁用DMA通道且丢失FIFO中的数据

清除相关通道配置寄存器中的通道使能位。当前的AHB传输(如果正在进行)完成后,通道会禁用。

注意:会丢失FIFO中的数据。

禁用DMA通道且不丢失FIFO中的数据

要禁用DMA通道且不丢失FIFO中的数据:

-

在相关通道配置寄存器中设置暂停位。这会导致忽略任何后续的DMA请求。

-

轮询相关通道配置寄存器中的活动位,直到其变为0。此位指示通道中是否有待传输的数据。

-

清除相关通道配置寄存器中的通道使能位。

设置新的DMA传输

要设置新的DMA传输:

-

如果通道未分配给DMA事务:

- 读取DMACENBLDCHNS寄存器,确定非活动通道。

- 选择具有必要优先级的非活动通道。

-

编程DMAC。

- 在相关DMA通道配置寄存器中设置暂停位。当前的源请求会被服务。忽略任何后续的源DMA请求,直到清除暂停位。

编程DMA通道

要编程DMA通道:

-

选择具有必要优先级的空闲DMA通道。DMA通道0具有最高优先级,DMA通道7具有最低优先级。

-

通过写入DMAC INTTCCLEAR和DMACINTERRCLR寄存器清除要使用的通道上的任何未决中断。上一个通道操作可能已留下活动的中断。

-

将源地址写入DMACCxSRCADDR寄存器。

-

将目标地址写入DMACCxDESTADDR寄存器。

-

将下一个LLI的地址写入DMACCxLLI寄存器。如果传输由单个数据包组成,必须将0写入此寄存器。

-

将控制信息写入DMACCxCONTROL寄存器。

-

将通道配置信息写入DMACCxCONFIGURATION寄存器。如果设置了使能位,则DMA通道会自动启用。

9.4.2.4 外设DMA请求ID

| Index | Description | Index | Description |

| 0 | UART1 Tx | 16 | I2S2 Tx |

| 1 | UART1 Rx | 17 | I2S2 Rx |

| 2 | UART0 Tx | 18 | AC97 PCMOUT |

| 3 | UART0 Rx | 19 | AC97 PCMIN |

| 4 | UART2 Tx | 20 | AC97 MICIN |

| 5 | UART2 Rx | 21 | SPDIF RX |

| 6 | SSP0 Tx | 22 | SPDIF TX |

| 7 | SSP0 Rx | 23 | MPEGTSI0 |

| 8 | SSP1 Tx | 24 | MPEGTSI1 |

| 9 | SSP1 Rx | 25 | MPEGTSI2 |

| 10 | SSP2 Tx | 26 | MPEGTSI4 |

| 11 | SSP2 Rx | 27 | CRYPTO BR |

| 12 | I2S0 Tx | 28 | CRYPTO BW |

| 13 | I2S0 Rx | 29 | CRYPTO HR |

| 14 | I2S1 Tx | 30 | Reserved |

| 15 | I2S1 Rx | 31 | Reserved |

9.4.2.5 地址生成

地址生成可以是递增的或非递增的。

注意:不支持地址环绕。突发不会跨越1 KB地址边界。

9.4.2.6 散播/收集

通过使用链接列表支持散播/收集。这意味着源和目标区域不必在内存中占据连续区域。如果不需要散播/收集,必须将DMACCxLLI寄存器设置为0。有关散播/收集DMA的更多信息,请参见附录B DMA接口。

链接列表项

一个LLI由四个字组成。这些字按以下顺序组织:

- DMACCxSCRADDR

- DMACCxDESTADDR

- DMACCxLLI

- DMACCxCONTROL

注意:DMACCxCONFIGURATION通道配置寄存器不属于LLI。

为散播/收集DMA编程DMAC

为散播/收集DMA编程DMAC:

-

将完整DMA传输的LLI写入内存。每个LLI包含四个字:

- 源地址

- 目标地址

- 指向下一个LLI的指针

- 控制字

最后一个LLI的链接列表字指针设置为0。

-

选择具有所需优先级的空闲DMA通道。DMA通道0具有最高优先级,DMA通道7具有最低优先级。

-

将之前写入内存的第一个LLI写入DMAC中的相关通道。

-

将通道配置信息写入通道配置寄存器并设置通道使能位。然后,DMAC在每个LLI加载时传输第一个及后续的数据包。

-

在每个LLI结束时,根据DMACCxCONTROL寄存器中的终端计数位,可以生成中断。如果设置了此位,则在相关LLI结束时会生成中断。必须处理中断请求,并在DMACINTTCCLEAR寄存器中设置相关位以清除中断。如果是这样,必须处理此中断请求,并在DMACINTTCCLR寄存器中设置相关INTTCCLEAR位以清除中断请求。

通过链接列表操作进行散播/收集

一系列链接列表定义了源和目标数据区域。每个LLI控制一块数据的传输,然后可选地加载另一个LLI以继续DMA操作,或停止DMA流。第一个LLI被编程到DMAC中。

LLI描述的数据包通常需要一个或多个DMA突发,分别传输到源和目标。

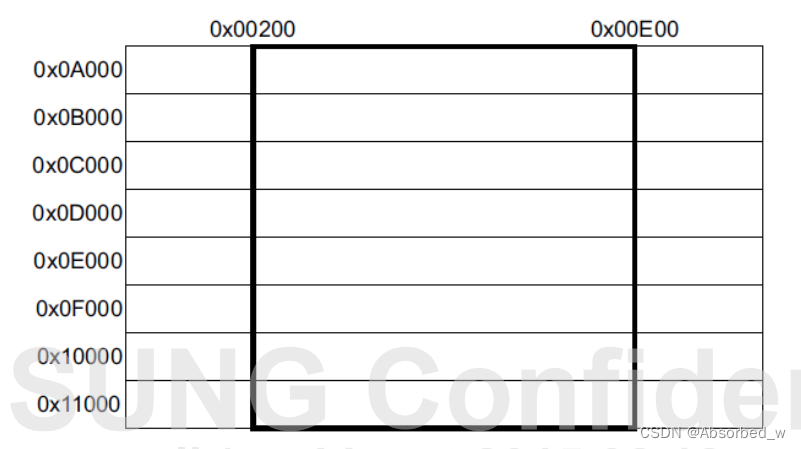

下图显示了LLI的一个示例。必须将内存的一个矩形传输到外设。数据每行的地址在图的左侧以十六进制表示。描述传输的LLI应从地址0x20000开始连续存储。

第一个LLI

第一个LLI存储在0x20000,定义了要传输的第一个数据块。这些数据存储在地址0x0A200和0x0AE00之间:

- 源起始地址:0x0A200

- 目标地址设置为目标外设地址

- 传输宽度:字(32位)

- 传输大小:3072字节(0xC00)

- 源和目标突发大小:16次传输

- 下一个LLI地址:0x20010

第二个LLI

第二个LLI存储在0x20010,定义了要传输的下一个数据块:

- 源起始地址:0x0B200

- 目标地址设置为目标外设地址

- 传输宽度:字(32位)

- 传输大小:3072字节(0xC00)

- 源和目标突发大小:16次传输

- 下一个LLI地址:0x20020

描述符链

描述符链被构建,每个描述符指向系列中的下一个。为了初始化DMA流,第一个LLI(0x20000)被编程到DMAC中。当第一个数据包被传输后,下一个LLI会自动加载。

最后一个LLI

最后一个LLI存储在0x20070,包含以下信息:

- 源起始地址:0x11200

- 目标地址设置为目标外设地址

- 传输宽度:字(32位)

- 传输大小:3072字节(0xC00)

- 源和目标突发大小:16次传输

- 下一个LLI地址:0x0

因为下一个LLI地址被设置为零,这是最后一个描述符,在传输完最后一项数据后,DMA通道将被禁用。在这一点上,该通道可能会生成一个中断,以指示ARM处理器该通道可以重新编程。

9.4.2.7 中断请求

中断请求可以在遇到AHB错误或传输结束时生成,即在当前LLI对应的所有数据传输到目标后生成终端计数。可以通过编程相关DMACCxCONTROL和DMACCxCONFIGURATION通道寄存器中的相关位来屏蔽中断。

提供了中断状态寄存器。这些寄存器在中断屏蔽之前汇总所有DMA通道的中断请求(DMACRAWINTTCSTATUS、DMACRAWINTERRORSTATUS),以及中断屏蔽之后的中断请求(DMACINTTCSTATUS、DMACINTERRORSTATUS)。

DMACINTSTATUS寄存器将DMACINTTCSTATUS和DMACINTERRORSTATUS请求合并到一个寄存器中,以便快速找到中断源。通过将相应的位设置为高,写入DMACINTTCCLEAR或DMACINTERRCLR寄存器,可以选择性地清除中断。

DMAC提供了两种中断请求连接方案。最简单的连接方案具有组合错误和传输完成中断请求。要找到中断源,必须读取DMACINTSTATUS和DMACINTTCSTATUS寄存器。

为了更快的中断响应,可以使用另一种连接方案。该方案使用单独的错误和传输完成请求中断。读取DMACINTTCSTATUS或DMACINTERRORSTATUS寄存器以找到中断源。

组合终端计数和错误中断序列流程

当使用DMACINTR中断请求时:

- 必须等待组合中断请求从DMAC变为活动状态。假设在中断控制器和处理器中启用了中断,处理器会分支到中断向量地址并进入中断服务例程。

- 必须读取中断控制器状态寄存器并确定请求的来源是否是DMAC。

- 必须读取DMACINTSTATUS寄存器以确定生成中断的通道。如果有多个请求处于活动状态,建议首先检查优先级最高的通道。

- 必须读取DMACINTTCSTATUS寄存器以确定中断是否由于传输结束、终端计数或错误而生成。高位表示传输完成。

- 必须读取DMACINTERRORSTATUS寄存器以确定中断是否由于传输结束、终端计数或错误而生成。高位表示发生了错误。

- 必须在DMACINTTCCLEAR或DMACINTERRCLR寄存器中写入1到相应的位,以清除中断请求。

终端计数中断序列流程

当使用单独的DMACINTTC和DMACINTERR中断请求时:

- 必须等待终端计数DMA中断请求变为活动状态。假设在中断控制器和处理器中启用了中断,处理器会分支到中断向量地址并进入中断服务例程。

- 必须读取中断控制器状态寄存器以确定中断请求的来源是否是DMAC断言的DMACINTTC信号。

- 必须读取DMACINTTCSTATUS寄存器以确定生成中断的通道。如果有多个请求处于活动状态,建议首先服务优先级最高的通道。

- 必须服务中断请求。

- 必须在DMACINTTCCLEAR寄存器中写入1到相应的位,以清除中断请求。

错误中断序列流程

当使用单独的DMACINTTC和DMACINTERR中断请求时:

- 必须等待因DMA通道错误而变为活动状态的中断请求。假设在中断控制器和处理器中启用了中断,处理器会分支到中断向量地址并进入中断服务例程。

- 必须读取中断控制器状态寄存器以确定请求的来源是否是DMAC断言的DMACINTERR信号。

- 必须读取DMACINTERRORSTATUS寄存器以确定生成中断的通道。如果有多个请求处于活动状态,建议首先检查优先级最高的通道。

- 必须服务中断请求。

- 必须在DMACINTERRCLR寄存器中写入1到相应的位,以清除中断请求。

中断轮询序列流程

DMAC中断请求信号在中断控制器中被屏蔽或在处理器中被禁用。当轮询DMAC时,必须:

- 读取DMACINTSTATUS寄存器。如果没有位为高,重复此步骤,否则转到步骤2。如果有多个请求处于活动状态,建议首先检查优先级最高的通道。

- 读取DMACINTTCSTATUS寄存器,以确定中断是否由于传输结束、终端计数或错误而生成。高位表示传输完成。

- 服务中断请求。

- 对于错误中断,在DMACINTERRCLR寄存器的相关位写入1以清除中断请求。对于终端计数中断,在DMACINTTCCLR寄存器的相关位写入1。

9.4.2.8 DMAC数据流

内存到内存DMA流

对于内存到内存DMA流:

- 编程并启用DMA通道。

- 当DMA通道具有最高挂起优先级且DMAC获得AHB总线主控权时,传输数据。

- 如果在传输数据时发生错误,则生成错误中断并禁用DMA流。

- 递减传输计数。

- 如果计数已达到零:

- 生成终端计数中断。可以屏蔽中断。

- 如果DMACCxLLI寄存器不为0,则重新加载以下寄存器并返回步骤2:

- DMACCxSRCADDR

- DMACCxDESTADDR

- DMACCxLLI

- DMACCxCONTROL

- 但是,如果DMACCxLLI为0,则禁用DMA流并结束流程序列。

内存到外设或外设到内存DMA流

对于外设到内存或内存到外设DMA流:

- 编程并启用DMA通道。

- 等待DMA请求。

- 当DMA请求变为活动状态,DMA流具有最高挂起优先级,并且DMAC是AHB总线主控时,DMAC开始传输数据。

- 如果在传输数据时发生错误,则生成错误中断,禁用DMA流,并结束流程序列。

- 如果DMAC控制流,则递减传输计数。

- 如果传输已完成,传输计数达到0(如果DMAC正在执行流控制)或外设设置了DMACLBREQ或DMACLSREQ信号(如果外设正在执行流控制),则:

- DMAC断言DMACTC信号。

- 生成终端计数中断。可以屏蔽中断。

- 如果DMACCxLLI寄存器不为0,则重新加载以下寄存器并返回步骤2:

- DMACCxSRCADDR

- DMACCxDESTADDR

- DMACCxLLI

- DMACCxCONTROL

- 但是,如果DMACCxLLI为0,则禁用DMA流并结束流程序列。

外设到外设DMA流

对于外设到外设DMA流:

- 编程并启用DMA通道。

- 等待源DMA请求。

- 当DMA请求变为活动状态,DMA流具有最高挂起优先级,并且DMAC是AHB总线主控时,DMAC开始传输数据。

- 如果在传输数据时发生错误,则生成错误中断,然后完成。

- 如果DMAC控制流,则递减传输计数。

- 如果传输已完成,传输计数达到0(如果DMAC正在执行流控制)或外设设置了DMACLBREQ或DMACLSREQ信号(如果外设正在执行流控制),则:

- DMAC对源外设断言DMACTC信号。

- 忽略后续源DMA请求。

- 当目标DMA请求变为活动状态且DMACFIFO中有数据时,将数据传输到目标外设。

- 如果在传输数据时发生错误,则生成错误中断,禁用DMA流,并结束流程序列。

- 如果传输已完成,传输计数达到0(如果DMAC正在执行流控制)或外设设置了DMACLBREQ或DMACLSREQ信号(如果外设正在执行流控制),则:

- DMAC对目标外设断言DMACTC信号。

- 生成终端计数中断。可以屏蔽中断。

- 如果DMACCxLLI寄存器不为0,则重新加载以下寄存器并返回步骤2:

- DMACCxSRCADDR

- DMACCxDESTADDR

- DMACCxLLI

- DMACCxCONTROL

- 但是,如果DMACCxLLI为0,则禁用DMA流并结束流程序列。

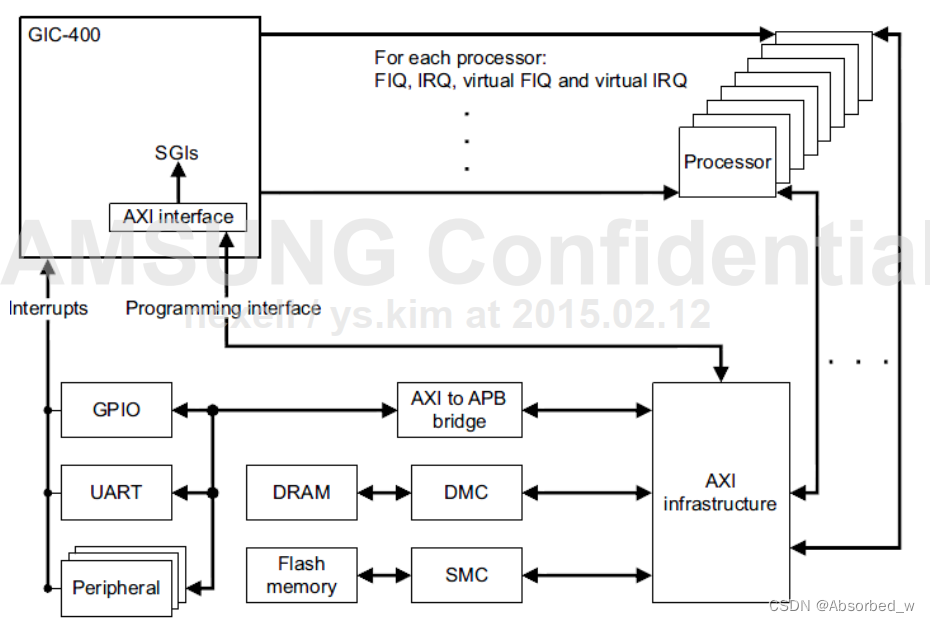

10 中断控制器

10.1 概述

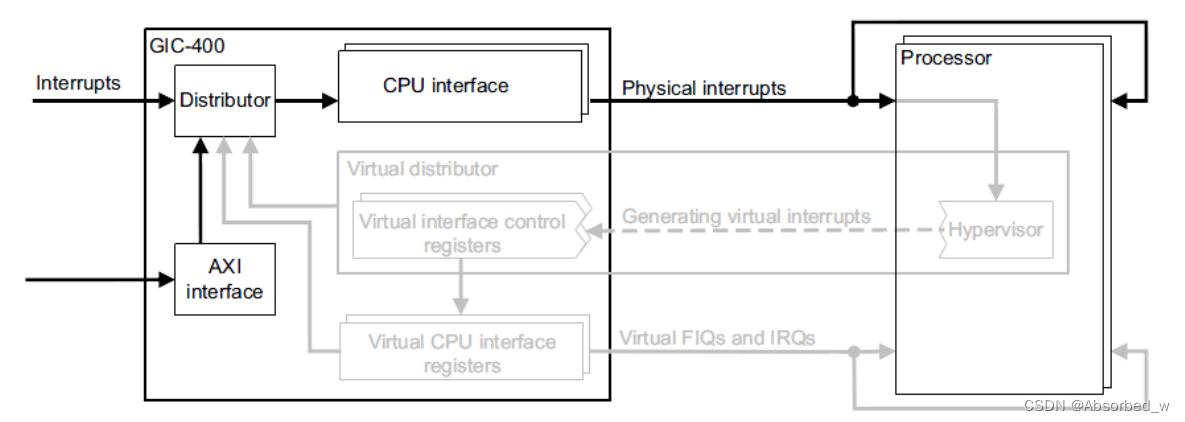

GIC 是一个高性能、面积优化的中断控制器,具有 AXI 接口。它在 S5P6818 中检测、管理和分发中断。GIC 是支持和管理系统中断的集中资源。

10.2 特性

GIC 提供用于管理中断源、中断行为和中断路由到一个或多个处理器的寄存器。

支持:

- ARM 架构的安全扩展

- ARM 架构的虚拟化扩展

- 启用、禁用和从硬件(外设)中断源生成处理器中断

- 软件生成的中断(SGI)

- 中断屏蔽和优先级排序

- 单处理器和多处理器环境

- 电源管理环境中的唤醒事件

GIC 包括支持以下功能的中断分组功能:

- 将每个中断配置为组 0 或组 1

- 使用 IRQ 或 FIQ 异常请求向目标处理器信号组 0 中断

- 使用 IRQ 异常请求向目标处理器信号组 1 中断

- 统一处理组 0 和组 1 中断优先级的方案

- 可选的组 0 中断配置锁定 GIC 支持 4 种中断类型:

- 16 个软件生成中断(SGI)

- 每个处理器有 6 个外部私有外设中断(PPI)

- 每个处理器有 1 个内部 PPI

- 128 个共享外设中断(SPI)

10.3 安全扩展支持 在包括安全扩展的实现中:

- 组 0 中断是安全中断,组 1 中断是非安全中断。

- 处理器对 GIC 寄存器的访问行为取决于访问是安全还是非安全的。除非本文档明确指明,否则访问 GIC 寄存器时:

- 非安全读取安全中断的寄存器字段状态信息返回零

- GIC 忽略任何对安全中断状态信息寄存器字段的非安全写入。非安全访问只能读取或写入与非安全中断对应的信息。 安全访问可以读取或写入与非安全和安全中断对应的信息。

- 安全系统软件单独定义每个实现的中断为安全或非安全。

- 非安全中断向目标处理器信号 IRQ 中断请求。

- 安全中断可以向目标处理器信号 IRQ 或 FIQ 中断请求。

- 安全软件可以安全地管理中断源,而不会受到非安全软件的干扰。

安全系统与为没有安全扩展的系统编写的软件向后兼容。

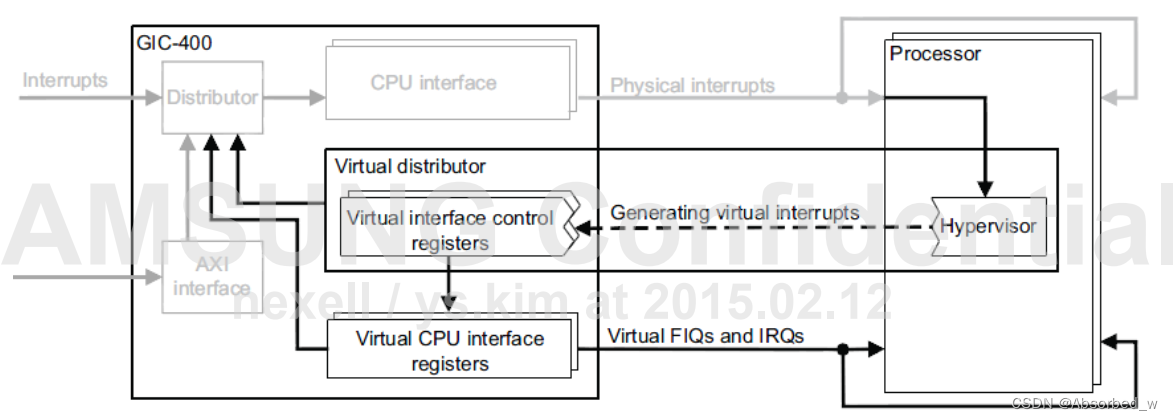

10.4 虚拟化支持

处理器虚拟化扩展为虚拟化 VMSAv7 实现的非安全状态提供硬件支持。这些扩展支持系统使用虚拟机监控器(称为管理程序)来切换客户操作系统。

无论是在单处理器还是多处理器系统中实现,处理器虚拟化扩展支持在单个处理器上运行多个虚拟机。

中断处理是虚拟化实现中的一个主要考虑因素。管理程序可以自己处理物理中断,或者生成相应的虚拟中断并向虚拟机发出信号。管理程序还可以生成不对应物理中断的虚拟中断。

这些扩展支持在支持处理器虚拟化的系统中处理虚拟中断和物理中断。例如,在一个与实现 ARM 处理器虚拟化扩展的处理器集成的系统中,GIC 虚拟化扩展提供机制以最小化管理程序路由中断到虚拟机的开销。

10.5 术语

10.5.1 中断状态

以下状态适用于系统中 GIC 与每个处理器之间的接口:

- 非活动:不活动或未挂起的中断。

- 挂起:GIC 从源中检测到在硬件中断言或由软件生成的中断,正在等待目标处理器服务。

- 活动:GIC 从源中检测到并由处理器确认的中断,正在服务但尚未完成。

- 活动和挂起:处理器正在服务中断,同时 GIC 有来自同一源的挂起中断。

10.5.2 中断类型

实现此 GIC 架构的设备可以管理以下类型的中断:

- 外设中断 这是由信号向 GIC 断言的中断。GIC 架构定义了以下类型的外设中断:

- 私有外设中断(PPI):这是特定于单个处理器的外设中断。

- 共享外设中断(SPI):这是分配器可以路由到任何指定组合处理器的外设中断。

每个外设中断可以是:

-

边沿触发:这是在检测到中断信号上升沿时断言的中断,不管信号状态如何,直到按本规范定义的条件清除。

-

电平敏感:这是当中断信号电平激活时断言的中断,当电平未激活时撤销。

-

软件生成中断(SGI) 这是通过软件写入 GIC 中的 GICD_SGIR 寄存器生成的中断。系统使用 SGI 进行处理器间通信。

SGI 具有边沿触发特性。触发中断的软件等效于中断请求信号的边沿转换。 当 SGI 发生在多处理器实现中时,中断确认寄存器 GICC_IAR 或别名中断确认寄存器 GICC_AIAR 中的 CPU ID 字段标识请求中断的处理器。

在包括 GIC 虚拟化扩展的实现中:

-

当发生 SGI 时,GIC 虚拟化扩展中的管理寄存器使请求处理器报告给客户操作系统,符合 GIC 规范的要求。

-

通过写入 GIC 虚拟化扩展中的管理寄存器,管理程序可以生成虚拟中断,使其在虚拟机中表现为 SGI。

-

虚拟中断 在实现 GIC 虚拟化扩展的 GIC 中,一个目标是处理器上运行的虚拟机的中断,通常通过连接的虚拟 CPU 接口向处理器发出信号。

-

维护中断 在实现 GIC 虚拟化扩展的 GIC 中,一种电平敏感中断,用于信号关键事件,例如某组中断的启用或禁用。

10.5.3 中断处理模型

在多处理器实现中,有两种中断处理模型:

- 1-N 模型:仅一个处理器处理此中断。系统必须实现一种机制来确定哪个处理器处理编程为目标多于一个处理器的中断。

- N-N 模型:所有处理器独立接收中断。当一个处理器确认中断时,挂起状态仅对该处理器清除。中断仍然对其他处理器挂起。

10.5.4 虚假中断

可能出现 GIC 向处理器信号的中断不再需要的情况。如果发生这种情况,当处理器确认中断时,GIC 返回一个特殊的中断 ID,将中断标识为虚假中断。

虚假中断的示例原因包括:

- 在处理器确认中断之前:

- 软件更改中断的优先级

- 软件禁用中断

- 软件更改中断的目标处理器

- 对于 1-N 中断,另一个目标处理器已先前确认该中断。

10.5.5 处理器安全状态和 GIC 访问的安全与非安全

实现 ARM 安全扩展的处理器有一个安全状态,安全或非安全:

- 非安全状态的处理器只能对 GIC 进行非安全访问。

- 安全状态的处理器可以对 GIC 进行安全和非安全访问。

- 在非安全状态下运行的软件称为非安全软件。

- 在安全状态下运行的软件称为安全软件。

实现安全扩展的 GIC 的多处理器系统可能包括一个或多个不实现安全扩展的处理器。此类处理器实现为:

- 仅对 GIC 进行安全访问,这意味着在处理器上运行的任何软件都是安全软件,只能进行安全访问。

- 仅对 GIC 进行非安全访问,这意味着在处理器上运行的任何软件都是非安全软件。

10.5.6 寄存器bank

-

中断bank在多处理器实现中,对于 PPI 和 SGI,GIC 可以有多个具有相同中断 ID 的中断。这种中断称为bank中断,通过其中断 ID 和其关联的 CPU 接口的组合唯一标识。

-

寄存器银行 寄存器银行指的是在同一地址实现寄存器的多个副本。

- 在多处理器实现中,为每个处理器提供独立的寄存器副本。

- 在实现安全扩展的 GIC 中,为某些寄存器提供独立的安全和非安全副本。

10.6 功能概述

10.6.1 功能接口

GIC 的主要模块有:

- AMBA 从接口

- 分配器

- CPU 接口

- 虚拟接口控制

- 虚拟 CPU 接口

- 时钟和复位

10.6.1.1 AMBA 从接口

AMBA 从接口提供对 GIC 寄存器的访问,使您能够编程系统配置参数并获取状态信息。

- AXI4 从接口

AXI4 从接口使用 32 位数据总线,由以下 AXI 通道组成:

- 写地址 (AW)

- 写数据 (W)

- 写响应 (B)

- 读地址 (AR)

- 读数据 (R)

AWUSER 和 ARUSER 信号是 GIC 特有的。它们向 GIC 指示哪个处理器正在执行请求。识别请求者对于确定 AXI 访问应定向到哪个 CPU 接口或虚拟 CPU 接口是必要的。此外,这对于某些分配器寄存器访问(例如 GICD_SGIR)也是必要的。AWUSER 和 ARUSER 信号的格式是从 0 到 CPU 数量减 1 的二进制数,包括这两个数字。生成 AWUSER 和 ARUSER 信号的唯一严格要求是所选择的编号方案必须表示处理器和合法编码范围之间的一致映射。处理器可以通过读取中断处理器目标寄存器 0(GICD_ITARGETSR0)来发现 GIC 使用的 ID。

AXI4 不支持写入交错。因此,AXI3 主设备必须设置为不交错写入。

10.6.1.2 分配器

分配器接收中断并将最高优先级的挂起中断呈现给每个 CPU 接口。

此外,GIC 实现了中断组寄存器 GICD_IGROUPRn,这些寄存器控制每个中断是配置为组 0 还是组 1。中断组影响中断是否可以转发到 CPU 接口,并且还会影响 CPU 接口中的后续路由决策,可能包括它是否作为 FIQ 或 IRQ 异常请求向处理器发出信号。

分配器为每个处理器提供 6 个外部 PPI 输入和内部虚拟维护 PPI,以及 0 到 223 个以 32 为倍数的 SPI。每个处理器的 PPI 是独立的,分配器只将它们转发到相应的 CPU 接口。您可以编程分配器以控制它将每个 SPI 路由到哪个 CPU 接口。

10.6.1.3 CPU 接口

每个 CPU 接口向相应的处理器发出中断信号,并从该处理器接收确认和 EOI 访问。这些 AXI 访问传递中断 ID 及有关中断的其他信息,并触发分配器状态的更新。

只有当中断具有足够的优先级时,CPU 接口才会向处理器发出挂起的中断。中断是否具有足够的优先级由 CPU 接口的配置和某些活动中断的优先级决定。

10.6.1.4 虚拟接口

GIC 实现了可选的 GIC 虚拟化扩展。GIC 的一组功能组件和处理器中的一些软件组成了一个虚拟分配器,其角色类似于物理分配器。 管理程序和虚拟接口控制寄存器一起形成虚拟分配器:

-

管理程序为物理中断创建虚拟中断并分配优先级。

-

每组虚拟 CPU 接口控制寄存器对虚拟中断进行优先级排序,并将最高优先级的挂起中断转发到其相应的虚拟 CPU 接口。管理程序还通过使用地址转换表来捕获虚拟机对虚拟分配器的访问来支持虚拟化。管理程序确定这些访问的效果,并可能相应地更新虚拟接口控制寄存器。

下图显示了虚拟分配器如何部分在 GIC 中实现,部分在处理器中实现,以及它如何与 GIC 中的分配器和虚拟 CPU 接口交互。GIC 实现了虚拟接口控制寄存器,即 GICH 寄存器,而处理器实现了管理程序。

- 虚拟接口控制块

GIC 实现了虚拟接口控制块,包括所有管理寄存器和四个列表寄存器。列表寄存器 GICH_LR0 - GICH_LR3 是虚拟接口控制寄存器的一个子集,定义了虚拟 CPU 接口的活动和挂起虚拟中断。管理寄存器,例如虚拟机控制寄存器 GICH_VMCR 和活动优先级寄存器 GICH_APR,使管理程序能够管理相应虚拟 CPU 接口的其他方面,并允许在虚拟机之间切换时保存和恢复状态。

- 虚拟 CPU 接口

虚拟 CPU 接口寄存器类似于 CPU 接口寄存器。然而,虚拟 CPU 接口接收来自由管理程序管理的虚拟接口控制寄存器的信息,而不是来自分配器。

在接收到物理中断或其他情况下,如果管理程序需要向当前虚拟机发出虚拟中断信号,它通常会更新虚拟接口控制寄存器。这些寄存器,特别是列表寄存器 GICH_LRn,保存了发送到当前虚拟机的虚拟中断列表。虚拟中断处理的信号、确认和 EOI 步骤通常可以由虚拟 CPU 接口在硬件中处理。某些情况下可能需要管理程序干预,例如列表寄存器中存储的虚拟中断超过限制。虚拟接口控制寄存器控制何时生成内部 PPI,称为虚拟维护中断。这个虚拟维护中断,PPI ID 25,旨在通知管理程序它必须处理的事件。

处理器的地址转换表通常配置为将虚拟机对 CPU 接口的访问定向到虚拟 CPU 接口。这确保了 CPU 接口的虚拟化对虚拟机是透明的。

- 管理程序

管理程序不是 GIC 的一部分,但对其操作至关重要。它是在每个运行虚拟机的处理器上执行的软件:

- 负责将物理中断转换为虚拟中断,并使用虚拟接口控制寄存器管理所有虚拟中断。

- 可以配置虚拟维护中断,以在需要管理虚拟中断时发出信号。通常,它会设置二级非安全地址转换表,以便虚拟机访问虚拟 CPU 接口而不是物理接口。

- 负责虚拟化虚拟机对分配器的访问,通常通过捕获访问并在软件中处理它们。

10.6.2 分配器

分配器集中所有中断源,确定每个中断的优先级,并为每个 CPU 接口分配优先级最高的中断,以进行优先级屏蔽和抢占处理。

分配器提供以下编程接口:

- 全局启用中断转发到 CPU 接口。

- 启用或禁用每个中断。

- 设置每个中断的优先级。

- 设置每个中断的目标处理器列表。

- 将每个外设中断设置为电平敏感或边沿触发。

- 将每个中断设置为组 0 或组 1。

- 将 SGI 转发到一个或多个目标处理器。

此外,分配器提供:

- 每个中断状态的可见性。

- 软件设置或清除外设中断挂起状态的机制。

10.6.2.1 中断 ID

来自源的中断通过 ID 号进行标识。每个 CPU 接口可以看到多达 1020 个中断。SPIs 和 PPIs 的银行增加了分配器支持的中断总数。

GIC 按如下分配中断 ID 号 ID0-ID1019:

- 中断编号 ID32-ID1019 用于 SPIs。

- 中断编号 ID0-ID31 用于对 CPU 接口私有的中断。这些中断在分配器中是bank化的。

- bank化中断是分配器可以具有相同 ID 的多个中断。bank化中断由其 ID 号和关联的 CPU 接口编号唯一标识。bank化中断 ID 中:

- ID0-ID15 用于 SGIs

- ID16-ID31 用于 PPIs

- 在多处理器系统中:

- PPI 转发到特定的 CPU 接口,并且对该接口是私有的。分配器在为 CPU 接口优先排序中断时不考虑与其他接口相关的 PPIs。

- 每个连接的处理器通过写入分配器中的 GICD_SGIR 发出 SGI。每次写入可以生成具有相同 ID 的 SGIs,目标是多个处理器。在分配器中,SGI 由中断号(ID0-ID15)、目标处理器 ID(CPUID0-CPUID7)和发出 SGI 的处理器源 ID(CPUID0-CPUID7)的组合唯一标识。当 CPU 接口向目标处理器传递中断 ID 时,它还提供处理器源 ID,使目标处理器能够唯一识别 SGI。

- SGI bank化意味着 GIC 可以同时处理多个 SGI,而不会发生资源冲突。

- 分配器忽略任何来自未连接到任何 CPU 接口的处理器的对 GICD_SGIR 的写入。分配器如何确定向 GICD_SGIR 写入的处理器的源 ID。

- 在单处理器系统中,没有共享和私有中断的区别,因为所有中断对处理器都是可见的。在这种情况下,处理器源 ID 值为 0。

- 中断编号 ID1020 至 ID1023 保留用于特殊用途。

系统软件设置每个中断的优先级。此优先级与中断 ID 号无关。在实现 ARM 安全扩展的任何系统中,为了支持处理器之间消息传递的一致模型,ARM 强烈建议所有处理器保留:

- ID0 到 ID7 用于非安全中断

- ID8 到 ID15 用于安全中断

10.6.3 CPU 接口

每个 CPU 接口块为连接到 GIC 的处理器提供接口。每个 CPU 接口提供以下编程接口:

- 启用向处理器发出中断请求信号

- 确认中断。

- 指示中断处理的完成。

- 设置处理器的中断优先级屏蔽。

- 定义处理器的抢占策略。

- 确定处理器的最高优先级挂起中断。

启用后,CPU 接口为其连接的处理器获取最高优先级的挂起中断,并确定中断是否具有足够的优先级以向处理器发出中断请求。为了确定是否向处理器发出中断请求,CPU 接口考虑中断优先级屏蔽和处理器的抢占设置。在任何时候,连接的处理器都可以从其 CPU 接口寄存器 GICC_HPPIR 中读取其最高优先级活动中断的优先级。

处理器通过读取 CPU 接口中断确认寄存器来确认中断。读取返回以下之一:

- 如果中断具有足够的优先级以向处理器发出信号,则返回最高优先级挂起中断的 ID 号。这是对中断确认的正常响应。

- 特殊情况下,返回一个指示虚假中断的 ID 号。

当处理器在 CPU 接口确认中断时,分配器将中断状态从挂起更改为活动或活动和挂起。此时,CPU 接口可以向处理器发出另一个中断信号,以抢占处理器上的活动中断。如果没有优先级足够高的挂起中断可以向处理器发出信号,接口将撤销对处理器的中断请求信号。

当处理器上的中断处理程序完成中断处理后,它会写入 CPU 接口以指示中断完成。

中断完成有两个阶段:

- 优先级下降,意味着已处理中断的优先级不再阻止向处理器发出另一个中断信号

- 中断去激活,意味着分配器移除中断的活动状态。

GICC_CTLR.EOI 模式位决定了:

- 两个阶段是否同时发生,当处理器写入 CPU 接口的中断结束寄存器时

- 两个阶段是否分开进行,这样:

- 当处理器写入 CPU 接口的中断结束寄存器时,优先级下降

- 中断去激活发生在稍后,当处理器写入 CPU 接口的去激活中断寄存器时。

10.7 中断处理和优先级排序

10.7.1 关于中断处理和优先级排序

中断处理描述了:

- GIC 如何识别中断。

- 软件如何编程 GIC 以配置和控制中断。

- GIC 为每个 CPU 接口上的每个中断维护的状态机。

- 处理器的异常模型如何与 GIC 交互。

优先级排序描述了:

- 中断优先级的配置和控制。

- 挂起中断的执行顺序。

- 确定中断何时对目标处理器可见,包括:

- 中断优先级屏蔽

- 优先级分组

- 活动中断的抢占

10.7.1.1 在多处理器系统中处理不同的中断类型

GIC 支持外设中断和软件生成的中断

在多处理器实现中,GIC 使用 N-N 模型处理软件生成的中断(SGI)。 GIC 使用 1-N 模型处理外设(硬件)中断。

10.7.1.2 识别支持的中断

GIC 为不同类型的中断定义了不同的 ID 值。然而,GIC 并不要求为任何中断类型实现连续的中断 ID 块。

为了正确处理中断,软件必须知道 GIC 支持哪些中断 ID。软件可以使用 GICD_ISENABLERn 来发现此信息。如果处理器实现了安全扩展,安全软件决定哪些中断对非安全软件可见。非安全软件必须知道它可以看到哪些中断,并可能使用此发现过程来获取此信息。

GICD_ISENABLER0 提供 SGI 和 PPI 的启用位,分别对应寄存器位 [15:0] 和 [31:16]。 其余的 GICD_ISENABLERn,从 GICD_ISENABLER1 开始,提供 SPI 的启用位,起始中断 ID 为 32。

软件发现支持的中断的方法:

-

读取 GICD_TYPER。GICD_TYPER.IT Lines Number 字段标识实现的 GICD_ISENABLERn 的数量,从而确定可能支持的最大 SPI 数量。

-

写入 GICD_CTLR 以禁用从分配器到 CPU 接口的中断转发。

-

对每个实现的 GICD_ISENABLERn,从 GICD_ISENABLER0 开始:

- 写入 0xFFFFFFFF 到 GICD_ISENABLERn。

- 读取 GICD_ISENABLERn 的值。读取为 1 的位对应支持的中断 ID。

软件使用 GICD_ICENABLERn 来发现永久启用的中断。对于每个实现的 GICD_ICENABLERn,从 GICD_ICENABLER0 开始,软件:

-

写入 0xFFFFFFFF 到 GICD_ICENABLERn。这样禁用所有可以禁用的中断。

-

读取 GICD_ICENABLERn 的值。读取为 1 的位对应永久启用的中断。

-

写入 1 到任何 GICD_ISENABLERn 位,对应必须重新启用的中断。

GIC 实现了相同数量的 GICD_ISENABLERn 和 GICD_ICENABLERn。

当软件完成其发现过程后,通常会写入 GICD_CTLR 以重新启用从分配器到 CPU 接口的中断转发。

如果 GIC 实现了安全扩展,软件可以使用安全访问来发现所有支持的中断 ID。

使用非安全访问的软件只能发现和控制配置为非安全的中断。如果安全软件在非安全软件发现其支持的中断后更改任何中断的安全配置,则必须将这些更改的影响传达给非安全软件。

在提供中断分组的 GIC 中,软件可以:

- 写入 GICD_IGROUPRn 寄存器,将中断配置为组 0 或组 1

- 使用 GICD_CTLR.EnableGrp0 和 GICD_CTLR.EnableGrp1 位独立控制组 0 和组 1 中断的转发。

10.7.2 中断的常规处理

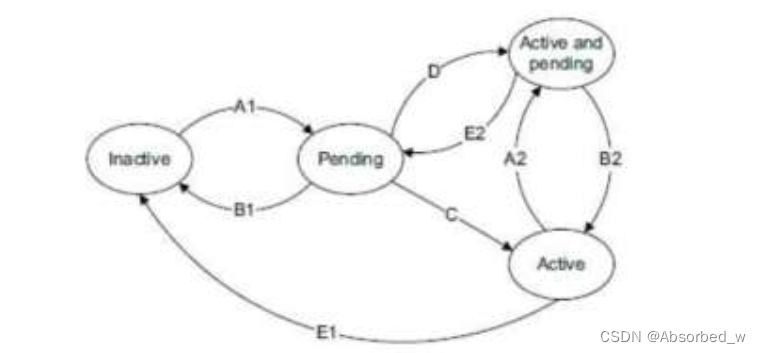

分配器为每个 CPU 接口上的每个支持的中断维护一个状态机。中断的可能状态是:

- 非活动

- 挂起

- 活动

- 活动和挂起

当 GIC 识别中断请求时,它将其状态标记为挂起。重新生成挂起的中断不会影响中断的状态。

GIC 中断处理顺序如下:

-

GIC 确定哪些中断是启用的。

-

对于每个挂起的中断,GIC 确定目标处理器或处理器组。

-

对于每个 CPU 接口,分配器将目标接口的最高优先级挂起中断转发给该接口。

-

每个 CPU 接口确定是否向其处理器发出中断请求信号,如果需要,则执行此操作。

-

处理器确认中断,GIC 返回中断 ID 并更新中断状态。

-

处理器处理完中断后,向 GIC 发出中断结束信号(EOI)。

详细说明如下:

-

GIC 确定每个中断是否启用。未启用的中断对 GIC 没有影响。

-

对于每个启用且挂起的中断,分配器确定目标处理器或处理器组。

-

对于每个处理器,分配器根据其持有的每个中断的优先级信息,确定最高优先级挂起中断,并将中断转发到目标 CPU 接口。

-

如果分配器将中断请求转发到 CPU 接口,CPU 接口确定中断是否具有足够的优先级以向处理器发出信号。如果中断具有足够的优先级,GIC 向处理器发出中断请求信号。

-

当处理器接受中断异常时,它读取其 CPU 接口的 GICC_IAR 以确认中断。读取返回一个中断 ID,对于 SGI,还返回源处理器 ID,处理器使用这些信息选择正确的中断处理程序。当识别到此读取时,GIC 将中断状态更改如下:

- 如果中断变为活动状态或中断再次生成,从挂起状态变为活动和挂起状态

- 否则,从挂起状态变为活动状态

- 当处理器完成中断处理后,它必须向 GIC 发出中断完成信号。

- 始终需要有效写入中断结束寄存器(EOIR)

- 可能还需要随后写入去激活中断寄存器(GICC_DIR)。

对于每个 CPU 接口,GIC 架构要求有效的 EOIR 写入顺序与从 GICC_IAR 或 GICC_AIAR 读取的顺序相反,以便每个有效的 EOIR 写入对应于最近确认的中断。

如果在 EOIR 写入后,没有足够优先级的挂起中断,CPU 接口将撤销对处理器的中断异常请求信号。

CPU 接口从不向连接的处理器发出任何活动和挂起的中断。它仅向处理器发出挂起且优先级足够高的中断:

- 对于 PPI 和 SGI,特定中断 ID 的活动状态在 CPU 接口之间是银行化的。这意味着如果特定中断 ID 在一个 CPU 接口上处于活动或活动和挂起状态,则该中断在其他接口上不发出信号。

- 对于 SPI,中断的活动状态对所有 CPU 接口是共同的。这意味着如果中断在一个 CPU 接口上处于活动或活动和挂起状态,则不会在任何 CPU 接口上发出信号。

注意:

- 当处理器确认中断时,电平敏感的外设中断将持续存在,因为向 GIC 发出的中断信号保持断言状态,直到运行在处理器上的中断服务例程(ISR)访问断言信号的外设。

- 在多处理器实现中,GIC 处理:

- 使用 GIC N-N 模型处理 PPI 和 SGI,其中一个处理器确认中断对其他 CPU 接口的中断状态没有影响

- 使用 GIC 1-N 模型处理 SPI,其中一个处理器确认中断会清除其他目标处理器上的中断挂起状态。

- 在 GICC_CTLR.ACKCTL 位设置为 0 的软件模型中,使用不同的寄存器来管理组 0 和组 1 中断,如下所示:

- 组 0 中断使用 GICC_IAR、GICC_EOIR 和 GICC_HPPIR

- 组 1 中断使用 GICC_AIAR、GICC_AEOIR 和 GICC_AHPPIR ARM 不建议使用 GICC_CTLR.ACKCTL,强烈推荐使用 GICC_CTLR.ACKCTL 设置为 0 的软件模型。

10.7.2.1 优先级下降和中断去激活

当处理器完成中断处理时,它必须向 GIC 发出中断完成信号。中断完成需要对 GIC 状态进行以下更改:

- 优先级下降:

优先级下降是对有效写入 EOIR(GICC_EOIR 或 GICC_AEOIR)的响应,运行优先级下降。有效写入是指未预测、不被忽略且未写入大于 1019 的中断 ID 值的写入。

优先级下降时,运行优先级从 EOIR 写入引用的中断的优先级降低到:

-

尚未写入 EOIR 的最高优先级活动中断的优先级

-

如果没有尚未写入 EOIR 的活动中断,则为空闲优先级。

-

中断去激活:

中断去激活是中断状态的更改,从:

- 活动和挂起状态变为挂起状态

- 活动状态变为空闲状态。

当 GICC_CTLR.EOI 模式设置为 0 时,有效的 EOIR 写入也会去激活它引用的中断。

将 GICC_CTLR.EOI 模式设置为 1 将优先级下降和中断去激活操作分开,处理软件必须:

- 执行有效的 EOIR 写入,以在 GIC CPU 接口上导致优先级下降。

- 随后写入 GICC_DIR,以去激活中断。

GIC 架构规范要求有效的 EOIR 写入是有序的,因此:

- 有效的 GICC_EOIR 写入对应于最近确认的中断

- 有效的 GICC_AEOIR 写入对应于最近确认的组 1 中断。

- GICC_EOIR 写入是否影响组 0 或组 1 中断取决于以下两者:

- GICC_CTLR.ACKCTL 位的值

- 如果 GIC 实现了 GIC 安全扩展,则写入是安全的还是非安全的。 GICC_DIR 写入没有排序要求。

然而,如果软件在以下情况下写入 GICC_DIR,其效果是不可预测的:

- GICC_CTLR.EOI 模式设置为 0

- GICC_CTLR.EOI 模式设置为 1 并且没有相应的 GICC_EOIR 或 GICC_AEOIR 写入。

在虚拟化物理中断时,ARM 建议,对于每个运行虚拟机的处理器对应的 CPU 接口:

- GICC_CTLR.EOI 模式位设置为 1

如果 GIC 实现了 GIC 安全扩展,则 GICC_CTLR.EOI 模式 NS 位设置为 1

10.7.2.2 GIC 中的中断控制

以下部分描述了 GIC 中的中断控制:

-

中断启用

-

设置和清除中断的挂起状态

-

查找中断的活动或挂起状态

-

生成 SGI

-

中断启用

对于外设中断,处理器:

- 通过写入相应的 GICD_ISENABLERn 位启用中断。

- 通过写入相应的 GICD_ICENABLERn 位禁用中断。

SGI 是永久启用的,或者可以通过写入 GICD_ISENABLERn 启用和禁用。

对 GICD_ISENABLERn 和 GICD_ICENABLERn 的写入控制分配器是否将特定中断转发到 CPU 接口。通过写入相应的 GICD_ICENABLERn 禁用中断不会阻止该中断更改状态,例如变为挂起状态。

- 设置和清除中断的挂起状态

对于外设中断,处理器可以:

- 通过写入相应的 GICD_ISPENDRn 位设置挂起状态

- 通过写入相应的 GICD_ICPENDRn 位清除挂起状态。

对于电平敏感中断:

- 如果处理器写入相应的 GICD_ICPENDRn 位时中断的硬件信号被断言,则对寄存器的写入对中断的挂起状态没有影响。

- 如果处理器写入 1 到 GICD_ISPENDRn 位,则无论该中断的硬件信号状态如何,相应的中断变为挂起状态,并且无论信号的断言或撤销如何,保持挂起状态。

对于 SGI,GIC 忽略对相应 GICD_ISPENDRn 和 GICD_ICPENDRn 位的写入。处理器无法通过写入这些寄存器更改软件生成中断的状态。通常,通过写入 GICD_SGIR 来使 SGI 挂起。SGI 的挂起状态也可以使用 ICD_SPENDSGIRn 和 GICD_CPENDSGIRn 位直接修改。

- 查找中断的活动或挂起状态

处理器可以查找:

- 通过读取相应的 GICD_ISPENDRn 或 GICD_ICPENDRn 位来查找中断的挂起状态

- 通过读取相应的 GICD_ISACTIVERn 或 GICD_ICACTIVERn 位来查找中断的活动状态

如果中断处于挂起或活动状态,则相应的寄存器位为 1。如果中断同时处于挂起和活动状态,则相应的位在两个寄存器中都为 1。

在保存或恢复 GIC 状态时,处理器必须考虑所有中断的挂起和活动状态。

对于 SGI,如果至少有一个生成处理器向读取 GICD_ISPENDRn 或 GICD_ICPENDRn 的处理器发送了挂起的中断,则相应的 GICD_ISPENDRn 和 GICD_ICPENDRn 位为只读。如果读取 GICD_ISPENDRn 或 GICD_ICPENDRn 的处理器有挂起的中断,则相应的 GICD_ISPENDRn 和 GICD_ICPENDRn 位为只读。在 GICv2 中,可以通过读取相应的 GICD_SPENDSGIRn 或 GICD_CPENDSGIRn 位来确定发出 SGI 的处理器。

- 生成 SGI

处理器通过写入 GICD_SGIR 生成 SGI。SGI 可以针对多个处理器,GICD_SGIR 写入指定目标处理器列表。GICD_SGIR 包括以下优化:

- 仅中断写入 GICD_SGIR 的处理器

- 中断写入 GICD_SGIR 的处理器以外的所有处理器。

来自不同处理器的 SGI 使用相同的中断 ID。因此,任何目标处理器都可以接收具有相同中断 ID 的不同处理器的 SGI。

然而,如果以下任何一项不同,任何两个 SGI 的挂起状态都是独立的:

- 中断 ID

- 源处理器

- 目标处理器。

在任何时候,CPU 接口上只能有一个具有特定中断 ID 的中断处于活动状态。这意味着 CPU 接口不能同时具有两个具有相同中断 ID 的活动 SGI,即使不同的处理器已向该处理器发送具有相同中断 ID 的 SGI。

在目标处理器的 CPU 接口上,读取 GICC_IAR 对于 SGI 返回中断 ID 和生成中断的处理器的 CPU ID,即中断的源处理器。中断 ID 和源 CPU ID 的组合使目标处理器能够唯一地识别中断。

在多处理器实现中,每个 SGI 中断 ID 的中断优先级由每个目标处理器独立定义,请参阅中断优先级寄存器 GICD_IPRIORITYRn。对于每个 CPU 接口,所有在该接口上挂起的具有特定中断 ID 的 SGI 具有相同的优先级,必须按顺序处理。CPU 接口按顺序处理这些 SGI 的顺序是实现特定的。

10.7.2.3 1-N 模型的影响

在多处理器实现中,GIC 使用 1-N 模型处理目标是多个处理器的外设中断,即 SPI。这意味着当 GIC 从目标处理器之一识别中断确认时,它会清除其他目标处理器上的中断挂起状态。GIC 实现必须确保任何使用 1-N 模型处理中断的中断只能由一个 CPU 接口确认,所有其他接口返回虚假中断 ID。

当多个目标处理器尝试确认中断时,可能会发生以下情况:

- 处理器读取 GICC_IAR 并获得要服务的中断 ID。

- 如果处理器在非常相似的时间读取其 GICC_IAR 寄存器,多个目标处理器可能获得相同的中断 ID。系统可能需要目标处理器上的软件确保只有一个处理器运行其中断服务例程。实现这一目标的典型机制是在共享内存中实现中断服务例程(ISR)上的锁。

- 处理器读取 GICC_IAR 并获得中断 ID 1023,指示虚假中断。处理器可以在其中断服务例程中返回,而不写入其 GICC_EOIR。虚假中断 ID 表明原始中断不再挂起,通常是因为另一个目标处理器正在处理它。

注意:GIC 实现可能确保只有一个处理器可以使 1-N 中断活动,从而消除 ISR 上的锁的需求。这不是架构要求,通用 GIC 代码不能依赖此行为。对于任何处理器,如果中断是活动和挂起的,则 GIC 不会向任何处理器发出中断异常请求,直到清除活动状态。

10.7.2.4 中断处理状态机

GIC 为每个 CPU 接口上的每个支持的中断维护一个状态机。下图显示了此状态机的一个实例以及可能的状态转换。

当分配器启用中断转发和 CPU 接口启用中断信号时,引起每个状态转换的条件如下:

- 转换 A1 或 A2,添加挂起状态

对于 SGI,如果以下任一情况发生:

- 软件写入 GICD_SGIR,指定处理器作为目标。

- 目标处理器上的软件写入与所需源处理器和中断 ID 对应的 GICD_SPENDSGIRn 位。

对于 SPI 或 PPI,如果以下任一情况发生:

-

外设断言中断请求信号。

-

软件写入 GICD_ISPENDRn。

-

转换 B1 或 B2,移除挂起状态

对于 SGI,如果目标处理器上的软件写入 GICD_CPENDSGIRn 的相关位。对于 SPI 或 PPI,如果以下任一情况发生:

-

电平敏感中断仅因输入信号的断言而挂起,并且该信号被撤销。

-

中断仅因边沿触发中断信号的断言或写入 GICD_ISPENDRn 而挂起,且软件写入相应的 GICD_ICPENDRn。

-

转换 C,挂起到活动

如果中断已启用且优先级足够高以向处理器发出信号,则在软件从 GICC_IAR 读取时发生。

- 转换 D,挂起到活动和挂起

对于 SGI,此转换在以下任一情况下发生:

- 如果将 SGI 状态设置为挂起的写入操作与读取 GICC_IAR 的操作几乎同时发生。

- 当两个或两个以上具有相同中断 ID 的挂起 SGI 来自相同源处理器并针对相同处理器时。如果其中一个 SGI 发生转换 C,则其他 SGI 发生转换 D。

对于 SPI 或 PPI,如果以下所有条件成立,此转换发生:

-

中断已启用。

-

软件从 GICC_IAR 读取。此读取将活动状态添加到中断中。

-

此外,以下条件之一适用:

- 对于电平敏感中断,中断信号保持断言。通常情况下是这样,因为外设在处理器服务中断之前不会撤销中断。

- 对于边沿触发中断,此转换是否发生取决于读取 GICC_IAR 的时间相对于中断重新断言的检测时间。否则,读取 GICC_IAR 导致转换 C,可能随后是转换 A2。

-

转换 E1 或 E2,移除活动状态

当软件通过写入 GICC_EOIR 或 GICC_DIR 去激活中断时发生。在实现虚拟化扩展的 GIC 中,如果虚拟 CPU 接口信号指示相应的物理中断已去激活,也会发生此转换。

10.7.2.5 特殊中断编号

GIC 架构保留中断 ID 号 1020-1023 用于特殊用途。在未实现安全扩展的 GIC 中,唯一使用的是 ID 1023。如果没有足够优先级的挂起中断可以向处理器发出信号,则在中断确认响应中返回此值,描述为虚假中断的响应。

见原文

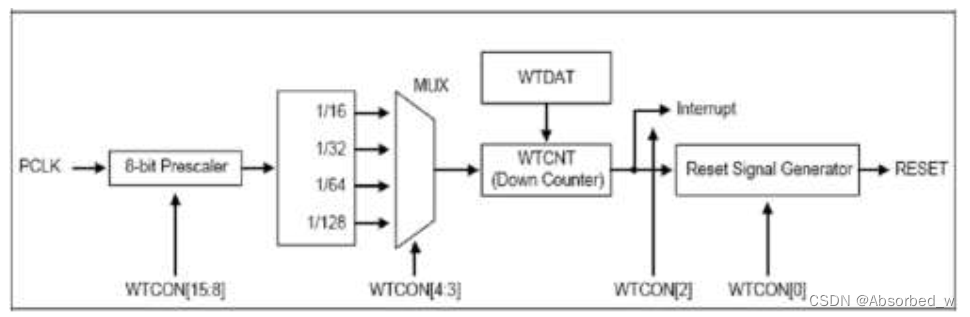

11 看门狗定时器

11.1 概述

看门狗定时器用于在控制器操作受到噪声和系统错误等故障干扰时恢复控制器操作。它可以用作普通的 16 位间隔定时器以请求中断服务。看门狗定时器生成复位信号。

看门狗定时器与 PWM 定时器的使用区别在于看门狗定时器生成复位信号。

11.2 特性

- 带有中断请求的普通间隔定时器模式

- 当定时器计数值达到 0(超时)时,内部复位信号被激活。

- 电平触发中断机制

11.3 功能描述

11.3.1 看门狗定时器操作

下图显示了看门狗定时器的功能模块图。看门狗定时器仅使用 PCLK 作为其源时钟。PCLK 频率被预分频以生成相应的看门狗定时器时钟,结果频率再次被分频。

预分频器值和频率分频因子在看门狗定时器控制(WDTCON)寄存器中指定。有效的预分频器值范围为 0 到 28-1。频率分频因子可以选择为 16、32、64 或 128。

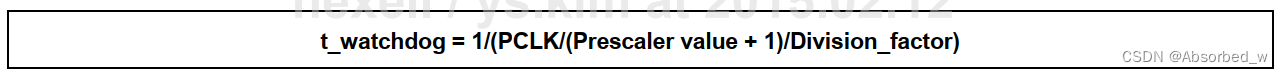

使用以下方程计算看门狗定时器时钟频率和每个定时器时钟周期的持续时间:

11.3.2 WTDAT 和 WTCNT

一旦启用看门狗定时器,监控定时器数据(WTDAT)寄存器的值不能自动重新加载到定时器计数器(WTCNT)中。因此,在看门狗定时器启动之前,必须向看门狗定时器计数(WTCNT)寄存器写入初始值。

11.3.3 调试环境的考虑

当 MDIRAC-III 处于调试模式嵌入式 ICE 时,看门狗定时器必须停止工作。看门狗定时器可以从 CPU 内核信号(DBGACK 信号)中确定它当前是否处于调试模式。一旦 DBGACK 信号被断言,看门狗定时器超时时,其复位输出不被激活。

11.3.4 特殊功能寄存器

11.3.4.1 内存映射

| Register | Type | Description | Reset Value |

| WTCON | RW | Watchdog timer control register | 0x8021 |

| WTDAT | RW | Watchdog timer data register | 0x8000 |

| WTCNT | RW | Watchdog timer count register | 0x8000 |

| WTCLRINT | W | Watchdog timer interrupt register | – |

11.3.4.2 看门狗定时器控制 (WTCON) 寄存器

WTCON 寄存器允许用户启用/禁用看门狗定时器,从 4 个不同的源中选择时钟信号,启用/禁用中断,以及启用/禁用看门狗定时器输出。

看门狗定时器用于在电源打开后恢复故障。如果不需要控制器重新启动,应禁用看门狗定时器。

如果用户想使用看门狗定时器提供的普通定时器,应启用中断并禁用看门狗定时器。

11.3.4.3 看门狗定时器数据 (WTDAT) 寄存器

WTDAT 寄存器用于指定超时持续时间。在初始看门狗定时器操作中,WTDAT 的内容不能自动加载到定时器计数器中。然而,使用 0x8000(初始值)将驱动首次超时。在这种情况下,WTDAT 的值将自动重新加载到 WTCNT 中。

11.3.4.4 看门狗定时器计数 (WTCNT) 寄存器

WTCNT 寄存器在正常操作期间包含看门狗定时器的当前计数值。注意,当看门狗定时器最初启用时,WTDAT 寄存器的内容不能自动加载到计数寄存器中,因此在启用之前必须将 WTCNT 寄存器设置为初始值。

11.3.4.5 看门狗定时器中断 (WTCLRINT) 寄存器

WTCLRINT 寄存器用于清除中断。中断服务例程负责在中断服务完成后清除相关中断。向此寄存器写入任何值都会清除中断。禁止读取此寄存器。

寄存器描述见原文

12 实时时钟 (RTC)

12.1 概述

实时时钟 (RTC) 模块可以在系统电源关闭时由备用电池供电。RTC 模块由 32 位自由计数寄存器组成,使用外部 32.768 kHz 晶体工作,并且可以执行闹钟功能。

12.2 特性

- 32 位计数器

- 闹钟功能:闹钟中断或从掉电模式唤醒

- 独立电源引脚 (VDD_RTC)

- 支持掉电模式的 1 Hz 时间中断

- 生成电源管理复位信号

12.3 模块图

在上图中显示了 RTC 模块图。RTC 模块接收 32.768 kHz 的外部时钟,并将其分频成 1 Hz。RTC 计数器根据外部时钟工作。

注意:如上图所示,中间虚线左右两部分分别使用 RTC 电源和正常电源。RTC 电源模块使用汞电池,但实际使用汞电池的模块是 RTC 电源模块中的 RTC 计数器。电池寿命约为五年。

在上图中,点 [A] 的输出应用于电源管理器或中断控制器。输出在正常模式下应用于中断控制器,在电源模式下应用于电源管理器。

注意:即使不使用 RTC,也应提供 RTC 电源和 RTC 时钟。

12.4 功能描述

12.4.1 备用电池操作

如上图所示,由于 RTC 模块使用独立的电源(纽扣电池),即使外部电源关闭,RTC 模块仍能工作。

即使系统电源关闭,RTC 逻辑也可以通过 VDD_RTC 引脚从备用电池供电。当系统电源关闭时,应屏蔽 CPU 和 RTC 逻辑的接口,备用电池仅驱动振荡电路和内部 32 位 RTC 计数器以最小化功耗。换句话说,当 S5P6818 转入掉电模式时,RTC 模块可以用作唤醒源。

要使用 RTC 模块作为唤醒源,需要在系统进入掉电模式之前将 RTCCTRL.ACCESSENB 位设置为“0”。将其设置为“0”是为了在系统进入掉电模式时仍能使用 RTC 作为唤醒源。

即使不使用 RTC 模块,也必须将 RTC 时钟连接到 S5P6818,因为 RTC 时钟用作电源管理操作的时钟。

12.4.2 RTC 操作

RTC 在掉电模式或正常操作模式下在指定时间生成闹钟信号。在正常操作模式下,闹钟中断被激活。在掉电模式下,电源管理唤醒信号和 RTCALARM 被激活。闹钟时间设置寄存器 (RTCALARM) 决定闹钟时间设置的条件,RTCINTENB.ALARMINTENB 位决定闹钟启用/禁用状态。

生成闹钟中断的步骤如下: 首先,将计数值写入 RTCCNTWRITE 寄存器。(为此,应提前检查 RTCCTRL.RTCCNTWAIT 的忙状态。写入值在两个 32.768 kHz 时钟周期后应用到寄存器。)之后,将希望生成中断的点的值写入 RTCALARM 寄存器。RTC 计数器以 1 Hz 的间隔增加计数值。如果 RTCINTENB.ALARMINTENB 位设置为“1”时,两个寄存器(RTCCNTWRITE 和 RTCALARM 寄存器)的值相等,则会发生中断。

以类似的方式,在 1Hz 上升沿检测到 RTC 中断。在这种情况下,通过将 RTCINTENB.RTCINTENB 位设置为“1”来生成中断。

此外,RTCINTENB 寄存器包含挂起清除功能,挂起清除通过写入“0”执行。

12.4.3 访问 RTC 时间计数设置/读取寄存器

要访问 RTC 时间计数读取寄存器 (RTCCNTREAD) 和 RTC 时间计数设置寄存器 (RTCCNTWRITE),在访问这些寄存器之前,将 RTCCTRL.RTCCNTWRITEENB 位设置为“1”。当 CPU 完成访问这些寄存器时,应将 RTCCTRL.RTCCNTWRITEENB 位设置为“0”,以保护 RTC 计数器的内容免受异常状态下未知问题的影响。RTCCNTWRITEENB 位决定 RCCNTWRITE 寄存器值对 RTC 计数器的反映。

12.4.4 中断挂起寄存器

对于 S5P6818 的 RTCINTPND 寄存器,仅提供“读取”功能,但可以读取当前的挂起状态。

由于 RTCINTPND 寄存器只有“读取”功能,挂起清除功能由 RTCINTENB 寄存器控制。通过禁用相关中断来清除中断挂起状态。因此,如果将 RTCINTENB 寄存器的相应位设置为“1”,则启用相关中断。如果将相应位设置为“0”,则禁用中断并清除挂起位。

12.4.5 电源管理复位时间控制

RTC 控制从 CorePOR 释放 nPWRMANRST(电源管理复位)的时间。有关设置 nPWRMANRST 释放时间,请参阅 RTCCORERSTIMESEL 寄存器。

13 ALIVE

13.1 概述

在去除 S5P6818 核心电源的状态下,一些 PAD 需要持续供电并保持驱动 PAD 为某一特定值。

例如,控制 STN LCD 的位在去除核心电源的状态下应保持驱动 PAD 为低电平。32 位值可以保存在暂存寄存器中,即使在核心电源关闭的情况下也能保持该值。

用户可以通过按下开关来开启/关闭系统电源,ALIVE 在这些瞬时电源控制中执行必要的功能。

13.2 特性

- ALIVE GPIO PADs 都是输入/输出 PAD。

- 即使在核心电源关闭时,ALIVE 模块的值仍然保持。

- ALIVE 模块不会解锁。要更改控制寄存器的值,需要直接对 SR-触发器的设定/复位引脚进行编程。

- 芯片睡眠模式唤醒源 (AliveGPIO, VDDToggle, RTCIRQ)

- 电源 IC 启用。

- 支持 PAD 保持功能

- 扫描链未插入到 ALIVE GPIO。

13.3 电源隔离

13.3.1 核心电源关闭

在核心电源(CoreVDD)关闭的情况下,由于 ALIVE VDD 保持供电,ALIVE 寄存器保持其值。连接到 NPOWERGATING 的下拉寄存器在核心电源关闭或不稳定的间隔期间执行保持 ALIVE 寄存器控制位的功能。

13.3.2 电源门控

在核心电源关闭的情况下,应保持设定/复位值为低,以确保 ALIVE 寄存器的值安全。因此,由于 NPOWERGATING 寄存器连接到下拉寄存器,它设计为在核心电源关闭的情况下保持低值。

13.4 ALIVE 寄存器

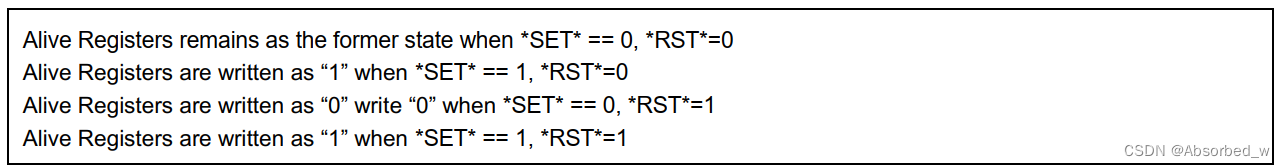

除 NPOWERGATING/AliveDetectPending 寄存器外,ALIVE 模块的所有寄存器在核心电源关闭时保持寄存器中写入的值,并在 ALIVE 电源关闭时复位。ALIVE 寄存器没有自己的时钟,在 NPOWERGATING 寄存器为 "1"(NPOWERGATING = 1)时可以读写。特别是在写模式下,可以通过 SET/RST(复位)寄存器写入 ALIVE 寄存器。以下是根据寄存器 SET/RST 的寄存器功能示例。

13.4.1 ALIVE GPIO 检测寄存器

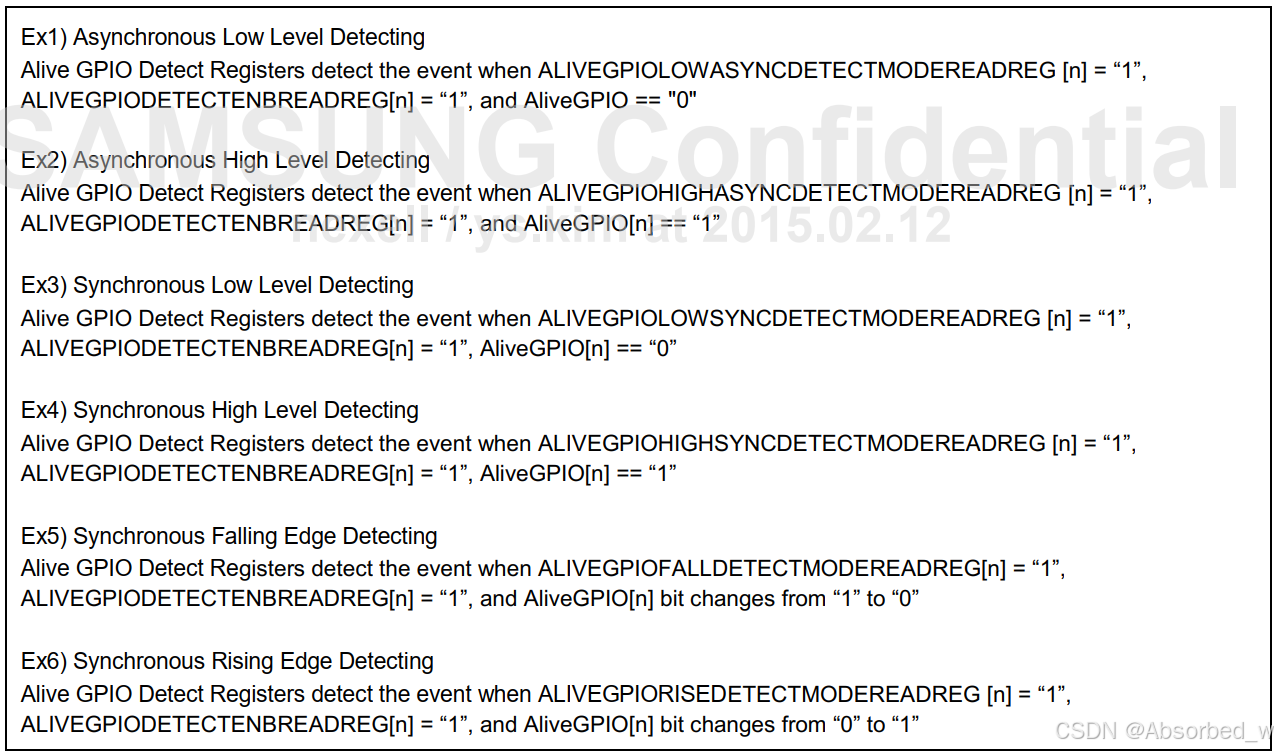

对于 ALIVE GPIO 输入,在异步/同步检测模式下,ALIVE GPIO 检测寄存器可用作核心电源开启、ALIVE 中断、睡眠模式唤醒源。当检测到这些事件时,ALIVEGPIODETECTPENDREG[n] 寄存器被设置为 "1"。以下是根据检测模式的操作示例。

13.4.2 暂存寄存器

程序员可以在暂存寄存器中保存任何 32 位值。在 CoreVDD 电源关闭的情况下,暂存寄存器的值仍然保持。

13.4.3 ALIVE GPIO 控制寄存器

无论 GPIO 块如何,ALIVE GPIO 都通过 ALIVE 块进行控制。

控制寄存器具有 ALIVE GPIO 输入/输出模式启用、上拉和 ALIVE GPIOPADOut 功能。

13.5 瞬时电源控制

13.5.1 CoreVDD 电源开启

通过 VDDPWRTOGGLE 开关、ALIVE GPIO 检测、RTC 中断,可以将核心电源从关闭状态切换到开启状态。在电源开启的情况下,系统启动后可以通过设置 VDDPWRON_DDR/VDDPWRON 位来处理 VDDPWRTOGGLE 开关、ALIVE GPIO 检测和 RTC 中断。(当电池故障发生时,不允许电源开启。)

13.5.2 CoreVDD 电源关闭

通过清除 VDDPWRON_DDR/VDDPWRON 位,可以将核心电源从关闭状态切换到开启状态。

核心块和 ALIVE 块通过 PowerGating 寄存器连接,这使得即使在清除 VDDPWRON_DDR/VDDPWRON 位后核心电源关闭时,ALIVE 寄存器仍然能够安全地保持其自身的值。

以下是芯片电源序列示例:

-

不要保持初始 Pad 状态。(NPADHOLDx = 1)

-

在关闭电源之前保持 Pad 状态。(NPADHOLDx 寄存器 = 0)

-

关闭 VDDPWRON

-

电源关闭后,非 ALIVE POR 被设为低电平

-

按下切换开关开始供电

-

当内部 POR 打开时,Pad 释放保持状态(这为防止电源开启后 Pad 保持释放提供了稳定性)

-

系统启动后,VDDPWRON 和 PadHold 寄存器应同时释放。

-

释放 VDDPWRON。

除电源开启复位外,NPADHOLDENBx 寄存器应设置为“0”。

13.6 睡眠模式

S5P6818 支持两种睡眠模式(SleepMode1,SleepMode2)。在睡眠模式下核心电源关闭,芯片通过唤醒源(如 ALIVE GPIO 检测、RTC 中断和 nVDDPWRTOGGLE 开关按下)从睡眠模式中唤醒。(如果发生电池故障,则无法唤醒)

- 清除 ALIVE GPIO 检测挂起寄存器

- 在用户关闭电源之前保持 Pad 状态。(SleepMode1: NPADHOLDx[2:1] = 2'b00, SleepMode2: NPADHOLDx[2:0] == 3'b000)

- 清除 VDDPWRON 寄存器

- 清除 NPOWERGATING 寄存器

- 设置 S5P6818 停止模式(参见时钟和电源管理部分)

13.7 电源管理单元 (PMU)

13.7.1 概述

PMU 是 ALIVE 内部的一个模块。它控制芯片内子模块的内部电源开关。PMU 可以控制这些模块的电源开关:

- GPU (图形处理单元)

- MFC (多功能编解码器)

14 ID 寄存器

14.1 概述

S5P6818 的 ECID 模块在 e-fuse ROM 上存储 128 位的 DIEID 信息。每个芯片都有自己的 DIEID 以识别它。

14.2 特性

- 支持 128 位 DIEID

- 支持 128 位安全启动 ID

- 支持 128 位安全 JTAG ID

- 支持 128 位后门 JTAG ID

- 可编程安全启动 ID、安全 JTAG ID、后门 JTAG ID

详细操作见原文

15 内存控制器

15.1 概述

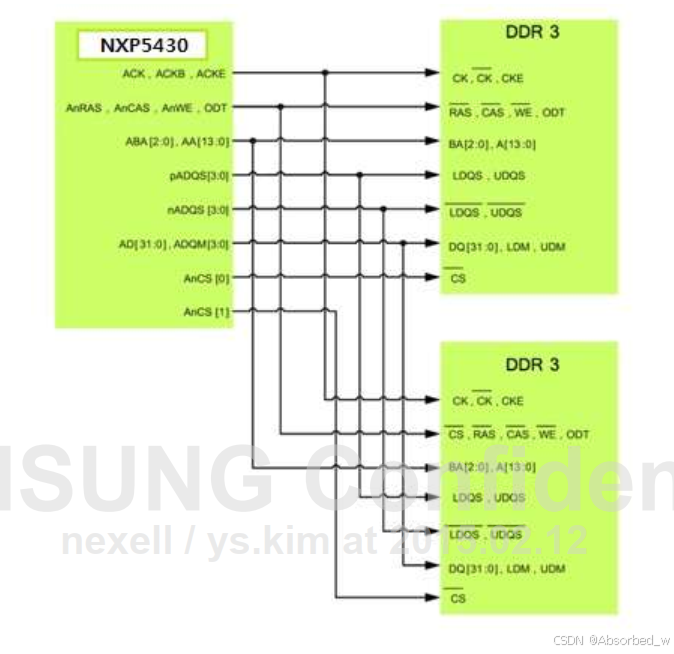

S5P6818 内存控制器基于统一内存架构 (UMA)。该控制器由两个控制单元组成:MCU-A 和 MCU-S。每个单元都有专用的控制引脚。

15.1.1 统一内存架构 (UMA)

• 两个独立的内存控制器:

- MCU-A: DDR3/LVDDR3 (低电压 DDR3)/LPDDR3/LPDDR2

- MCU-S: 静态内存

- MCU-A 特性:

- MCU-A 由 DREX 和 DDRPHY 组织

- 支持 DDR3/LVDDR3 (低电压 DDR3)/LPDDR3/LPDDR2 内存

- 支持 8/16/32 位 2 GB SDRAM

- 单bank内存 (32 位数据总线宽度)

- 支持省电模式

- 支持自刷新模式

- MCU-S 特性:

- 静态内存

- 两个静态内存芯片选择

- NAND 闪存接口

- 使用锁存地址支持 23 位地址

- SLC NAND, MLC NAND,带有 ECC (支持 BCH 算法)

- 静态内存映射影像

15.3 功能描述

S5P6818 的内存控制器区域分为 MCU-A 和 MCU-S bank。MCU-A bank 连接到 DDR3/LVDDR3 (低电压 DDR3)/LPDDR3/LPDDR2,是 S5P6818 的主内存,数据总线宽度为 32 位。

MCU-S bank 是静态bank,可以连接到静态内存/设备、NAND。

15.3.1 MCU-A Bank 特性

• 兼容 JEDEC 标准 LPDDR2-S4/LPDDR3/LVDDR3 (低电压 DDR3)/DDR3 SDRAM • 支持总线时钟和内存时钟之间的 1:2 同步操作 • 集成 TrustZone 地址空间控制单元 • 支持多达两个内存级 (芯片选择) 和每个内存芯片 4/8 个bank • 支持每个芯片选择 512 Mb、1 Gb、2 Gb、4 Gb、8 Gb 和 16 Gb 的密度 • 支持 QoS 方案以确保实时应用的低延迟 • 无序调度策略以提高性能 • 支持提前写入响应 • 支持级/bank交错 • 支持未完成的独占访问 • 支持bank选择预充电策略 • 包含嵌入式性能监视器 • DREX 时钟:MBCLKn(40e0xMHezl) • DDRPHY 时钟:MCLK(800 MHz,待定),MDCLK(800 MHz,待定) • MBCLK:MCLK = 1:MBCLKx2 • MDCLK:MDCLK 0° 相位主 DLL 时钟(400 到 800 MHz)。该时钟应与正常模式下的 clk2x 频率相同,并由与 MCLK 使用相同的 PLL 生成。但主 DLL 无法在 400 MHz 以下锁定。如果 MCLK 低于 400 MHz,可以使用 clk2x 的双频率来锁定主 DLL 以进行低频操作

15.3.2 MCU-S Bank 特性

• 锁存寻址

外部连接的引脚数量为 ADDR [18:0]。然而,MCU-S Bank 的总地址为 26 位。ADDR[8:2] 和 ADDR[25:19] 分配到相同的引脚,系统具有两次输出地址的结构。如果系统使用 ADDR[19] 或以上,通过系统配置引脚 (CfgSTLATADD) 可以设置更高地址 (ADDR[25:19])。在这种情况下,首先应通过使用外部锁存 IC 锁存由 ADDR[25:19] 配置的地址。 • 16 位数据总线宽度除 NAND 闪存 (8 位) 外的静态内存寄存器具有总线宽度选择寄存器 • 静态内存控制器正常的静态内存 (SRAM 和 ROM) 或静态设备连接。存在多达两个静态芯片选择信号。 • NAND 闪存控制器支持小块和大块 NAND 闪存。最多可连接两个 NAND 闪存。 支持 SLC 和 MLC NAND 闪存。 使用二进制 BCH 编码,支持多达 4/8/16/24/40/60 位错误校正 (1024 或 512 字节)。

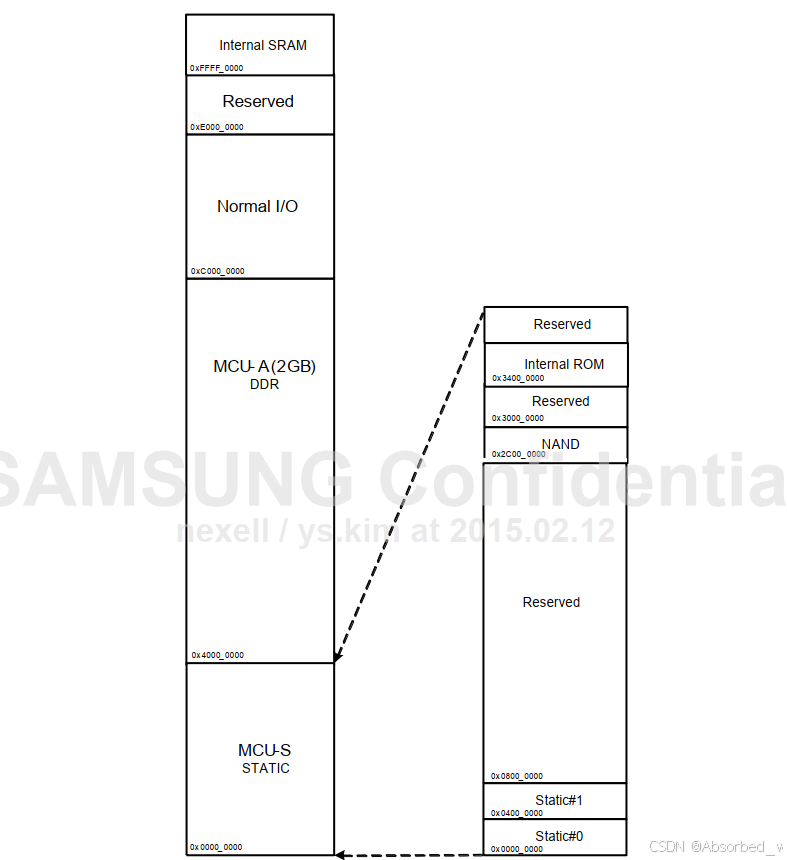

15.3.3 内存映射

内存映射大致分为一个 SDRAM Bank (MCU-A) 和一个静态 bank (MCU-S)。静态 bank 由 NAND 闪存控制器和静态内存控制器组成。MCU-A bank 包括一个线性阵列区域和显示阵列区域。

15.3.4 MCU-A 地址映射

DREX 将来自 AXI 从端口的 AXI 事务地址修改为内存地址,包括芯片选择、bank地址、行地址、列地址和内存数据宽度。 “宽度”表示所用 DRAM 的数据宽度,固定为 32 位(4 字节),因此,在字节寻址的地址值上,相应的宽度固定为 2。

相关的 SFR 在 MEMCONFIG0/1 寄存器中的 BANK_LSB、CHIP_INTER_EN、BIT_SEL_EN 和 CHIP_MAP。在芯片交错的情况下,两个芯片的配置应相同。 要将内存设备的芯片选择映射到地址映射的特定区域,需要设置 MEMCONFIG0 寄存器的 CHIP_BASE 和 CHIP_MASK 位字段(参见寄存器描述)。如果存在内存设备的 chip1,则还必须设置 MEMCONFIG1 寄存器。然后,AXI Master 请求的 AXI 地址被分为 AXI 基地址和 AXI 偏移地址。AXI 基地址激活相应的内存芯片选择,AXI 偏移地址根据 MEMCONFIG0/1 和 MEMCONTROL 寄存器设置的 bank、行、列号和数据宽度映射到内存地址。

有两种方式来映射 AXI 偏移地址,如下所示:

- 简单交错映射

- 列分割交错映射

- 随机交错映射

- 芯片交错映射

15.3.4.1 列分割交错映射

CHIP_INTER_EN = 0x0, BIT_SEL_EN = 0x0 和 CHIP_MAP = 0x2 表示列分割交错映射。

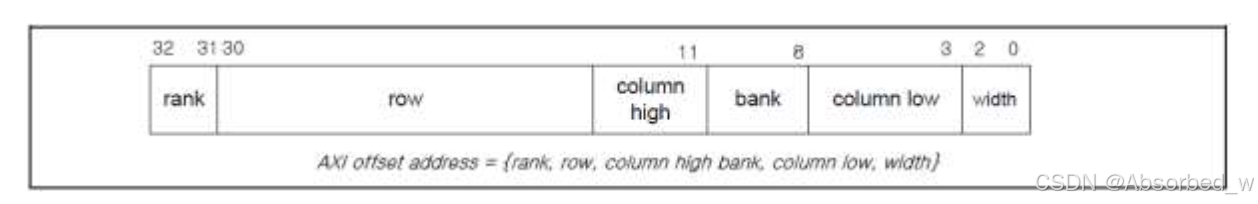

如图 所示,列分割交错映射方法按行、列高、bank、列低和宽度的顺序映射 AXI 地址。

相关的 SFR 是“BANK_LSB”,它选择列低大小(参见寄存器描述)。如果 BANK_LSB 与实际内存页大小相同,则列不会被分割。

15.3.4.2 随机交错映射

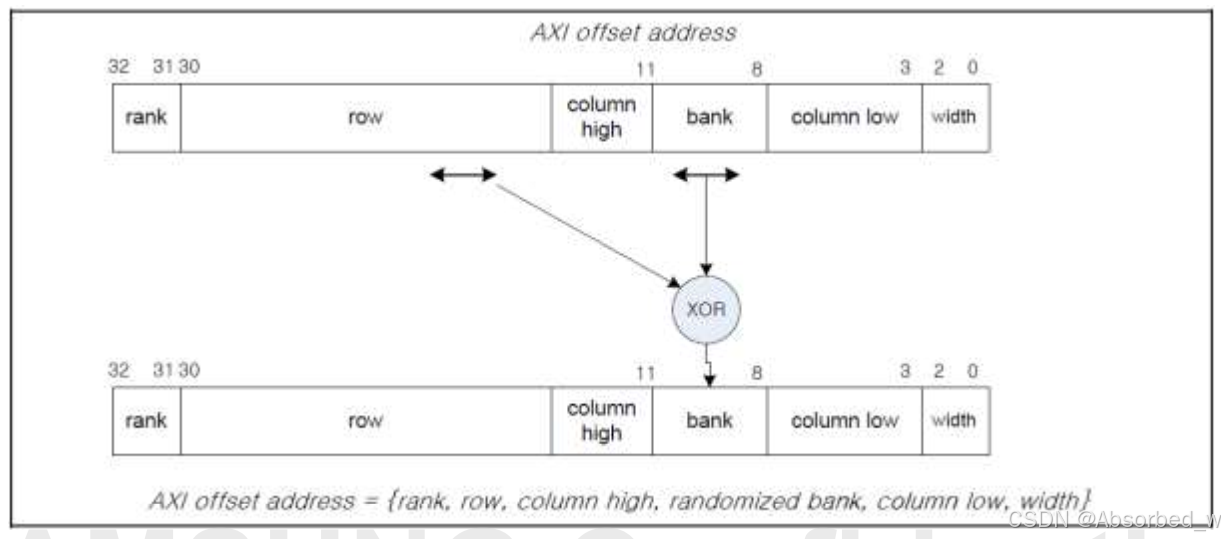

除了列分割交错地址映射,DREX 还支持随机交错映射。如下面的图所示,通过将选自 AXI 地址的附加位与 bank 地址进行异或操作来实现 bank 地址的随机化。通过更积极地将内存访问分布到多个 bank 中,这进一步提高了性能。

CHIP_INTER_EN = 0x0 和 BIT_SEL_EN = 0x1 表示随机交错映射。

15.3.4.3 级交错映射

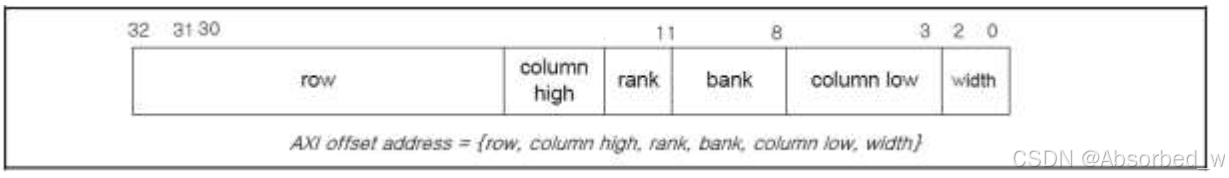

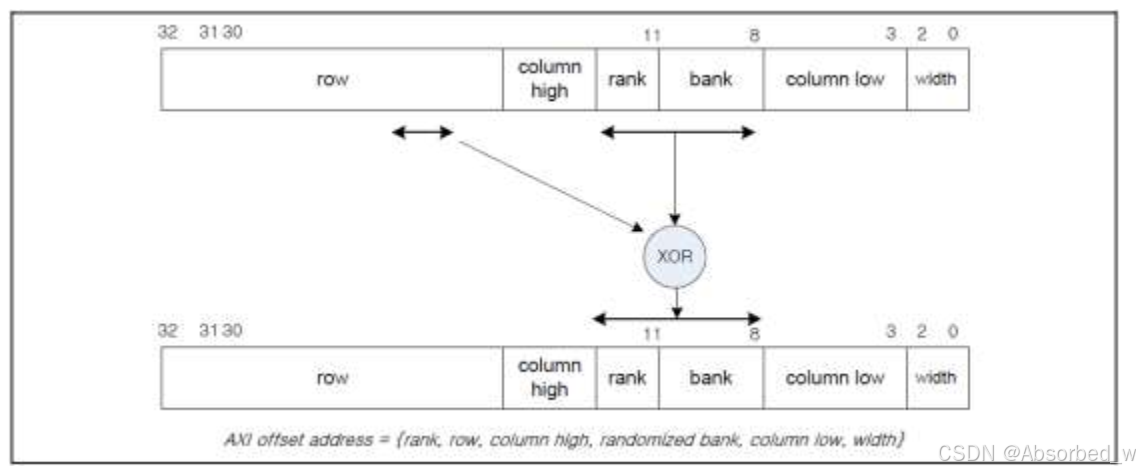

RANK_INTER_EN = 0x1 表示级交错映射。如果启用了 RANK_INTER_EN,那么上图将分别更改为下图。

Rank Interleaved Address Mapping (CHIP_MAP = 0X2, BIT_SEL_EN = 0X0)

Rank Interleaved Address Mapping (CHIP_MAP = 0x2, BIT_SEL_EN = 0x1)

15.3.5 低功耗操作

控制器以以下五种方式执行低功耗内存操作。每个功能彼此独立并可同时执行。

当内存处于 SREF 状态时,如果收到 AXI 请求,控制器将自动发出 SRX 命令。

15.3.5.1 AXI 低功耗通道

控制器有一个 AXI 低功耗通道接口,用于与系统控制器等低功耗管理单元通信,使内存设备进入自刷新模式。

15.3.5.2 动态掉电

SDRAM 设备具有激活/预充电掉电模式。通过将 CKE 解除为低电平触发该模式。当任何一个 bank 打开时,它进入激活掉电模式。否则,它进入预充电掉电模式。

当请求缓冲器在一定数量的周期内保持为空时(PWRDNCONFIG.DPWRDN_CYC 寄存器),DREX-1 自动将内存设备的状态更改为激活/预充电掉电模式。内存设备根据 SFR 设置进入激活/预充电掉电模式或强制预充电掉电模式。两种掉电模式的描述如下:

-

激活/预充电掉电模式:在不考虑是否有行打开的情况下进入掉电。

-

强制预充电掉电模式:关闭所有 bank 后进入掉电。

当 DREX-1 在内存设备处于掉电模式时收到新的 AXI 事务时,它会自动唤醒内存设备并执行正常操作。

15.3.5.3 动态自刷新

与动态掉电功能类似,如果请求缓冲器在一定数量的周期内保持为空(PWRDNCONFIG.DSREF_CYC 寄存器),DREX-1 将内存设备的状态更改为自刷新模式。由于退出掉电模式需要很多周期,因此建议动态自刷新入口的空闲周期阈值比动态掉电的阈值更长。

15.3.5.4 时钟停止

为了减少内存设备和控制器的 I/O 功耗,如果 LPDDR / LPDDR2-S4 处于空闲模式或自刷新模式,并且 DDR3 处于自刷新模式,可以停止时钟。如果启用此功能,控制器将自动执行时钟停止功能。在 DDR3 中,时钟停止功能必须通过软件考虑 tCKSRX / tCKSRE / tCKESR 时间打开和关闭。

15.3.5.5 直接命令

使用直接命令功能,通过 APB3 端口直接向内存设备发送内存命令。这样,可以强制内存设备进入激活/预充电掉电、自刷新或深度掉电模式。

15.3.6 预充电策略

对于预充电策略,DREX 有两个选项 - 端口选择预充电和每端口超时预充电。

15.3.6.1 端口选择预充电

由于应用程序对页面策略的偏好不同,工程师难以决定使用开放页面策略还是关闭页面(自动预充电)策略。与其将页面策略应用于所有端口,不如端口选择预充电策略允许用户为每个端口选择预充电策略(参见 PRECHCONFIG.PORT_POLICY)。这样,可以为某些应用程序分配开放页面策略,为其他应用程序分配关闭页面(自动预充电)策略。

- 开放页面策略:在读取或写入后,访问的行保持打开状态。

- 关闭页面(自动预充电)策略:当 DREX 发出最后一个读取或写入 CAS 命令时,它会增加一个自动预充电标志。

15.3.6.2 超时预充电

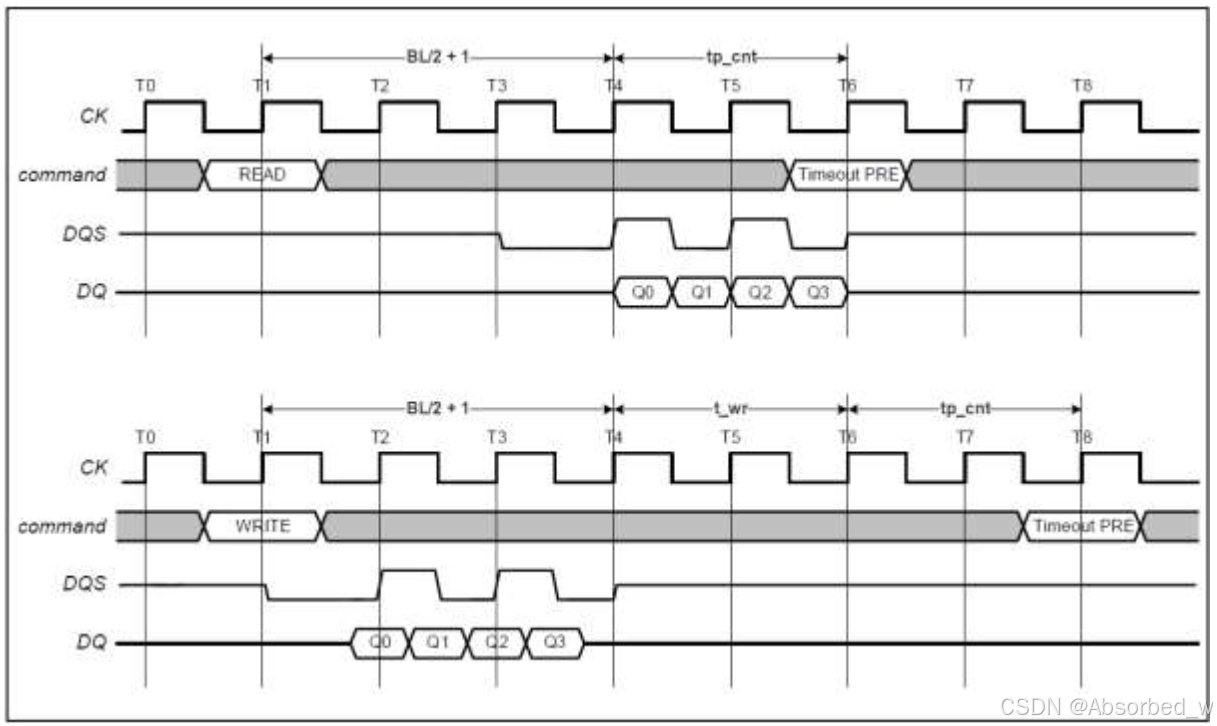

如果某个端口使用开放页面策略,数据访问后该行保持打开。如果发生这种情况,并且保持打开状态的 bank 在特定数量的周期内未调度(PRECHCONFIG.TP_CNT 位字段),控制器将自动发出预充电命令以关闭该 bank。

15.3.7 服务质量

DREX 提供服务质量 (QoS) 功能,以确保实时主设备的低延迟。具体来说,DREX 使用基于超时的 QoS 执行方案。

- 当 DREX 接收到 AXI 事务时,会为相应的内存请求分配一个预定义的 QoS 超时值。

- 当计时器到期时,请求会提升到最高优先级,以便在仲裁阶段立即选择。

15.3.7.1 BRB 仲裁

端口中 AXI 请求 FIFO 头部的 AXI 请求被仲裁到 Bank 请求缓冲区 (BRB)。每个端口的优先级由 FIFO 中 AXI 请求的最高 AxQoS 值决定。当 AXI 请求 FIFO 计时器 (CONCONTROL.TIMEOUT_LEVEL0) 到期时,FIFO 的端口具有最高优先级,以防止低优先级端口的饥饿。

15.3.7.2 基于 AxQoS 的 QoS

当 DREX 接收到 AXI 请求时,它根据 AxQoS 值(0 到 15)分配预定义的 BRB 超时值 (QOSCONTROL_N.CFG_QOS, n= 0 到 15)。当 BRB 计时器到期时,请求在请求调度器中具有最高优先级。当 BRB 已满或请求的数据缓冲区已满时,BRB 计时器按预定义值 (BRBQOSCONFIG.BRB_QOS_TIMER_DEC) 递减,而不是 1。

15.3.7.3 BRB 空间预留

当为 AXI AR/AW 端口启用 BRB 空间预留 (BRBRSVCONTROL.BRB_RSV_EN_{W, R}{0,1,2,3}) 时,当目标 BRB 的占用超过 BRB 阈值 (BRBRSVCONFIG.BRB_RSV_TH_{W, R}{0,1,2,3}) 时,AXI 端口停止发出 BRB 仲裁请求。

15.3.7.4 紧急优先级提升

除了传统的 QoS 方案外,DREX-1 支持基于紧急信号的优先级提升。此功能使用两个附加输入信号实现:

- 每个 AXI 端口有附加的 ARMARKER[4:0] 和 AWMARKER[4:0] 输入信号。这些信号用于标识给定请求的 QoS 类,例如,发送请求的主设备,或在特定应用场景中两个特定主设备之间发生的通信。

- EMERGENCY_R[30:0] 和 EMERGENCY_W[30:0] 输入信号,用于指定需要更高优先级的流量类。

默认情况下,主设备将 EMERGENCY_R 和 EMERGENCY_W 的值驱动为 31'b0。当某个请求类需要更高优先级时,主设备驱动相应的 EMERGENCY_R(读取)或 EMERGENCY_W(写入)位,以提升该类所有流量的优先级。具体而言,当 EMERGENCY_R[n] 驱动为 1 时,所有 ARMARKER 值为 n + 1 的读取请求优先级提高,当 EMERGENCY_W[n] 驱动为 1 时,所有 AWMARKER 值为 n + 1 的写入请求优先级提高。

当相应的 EMERGENCY_R/EMERGENCY_W 信号返回到 0 时,优先级返回到其原始优先级。注意,无论 EMERGENCY_R/EMERGENCY_W 信号如何,超时计数器应继续递减。

有可编程寄存器(每 AxMARKER 值),用于确定在优先级提升情况下移动到的优先级级别。用户可以在“超时”优先级和“紧急页面未命中”优先级之间进行选择。

15.3.8 Trust Zone 地址空间控制 (TZASC)

TZASC 对内存的 AXI 访问执行安全检查。这支持可配置数量的区域。每个区域的大小、基地址、启用和安全参数都是可编程的。使用 SECURE_BOOT_LOCK 输入信号,可以锁定程序员视图以防止错误写入。它提供在使用 AXI 响应通道和中断报告故障的可编程性。

15.3.8.1 区域

一个区域是一个连续的地址空间。TZASC 为每个区域提供一个可编程的安全权限字段。安全权限值用于使 TZASC 接受或拒绝对该区域的事务访问。事务使用 arprots[2:0] 或 awprots[2:0] 信号来确定该事务的安全设置。区域特征如下:

- 最小区域粒度:64 KB

- 区域数量:8 个不重叠区域(区域 1 到 8)+ 1 个默认区域(区域 0)

- 区域优先级:priority_of_region_1 到 8 > priority_of_region_0

- 区域的地址空间

- 基地址:对齐到 64 KB

- 区域大小:64 KB × N

- 区域最大大小:4 GB

- 区域 0 覆盖整个地址空间

- 不支持子区域

区域的安全属性功能如下:

- 4 位权限

- 每个位表示是否允许(安全读取、安全写入、非安全读取、非安全写入)

- 例如)具有安全属性 b'1100 的区域允许安全访问(读取和写入),但禁止非安全访问

- 1 位区域锁定

- SECURE_BOOT_LOCK 断言后,区域配置(SFR)被锁定

- 1 位区域启用

- 区域 1 到 8 由 SFR 启用

- 区域 0 始终启用

15.3.8.2 拒绝的 AXI 事务

如果 AXI 事务没有足够的安全权限,则对于:

- 读取:TZASC 通过将读数据总线 RDATA 的所有位设置为零来响应主设备。

- 写入:TZASC 阻止数据写入内存。

TZASC 动作寄存器控制当区域权限失败时,TZASC 是否向主设备发出信号,以及它提供的响应类型。

15.3.8.3 防止对寄存器的写入和使用 SECURE_BOOT_LOCK

TZASC 期望 SECURE_BOOT_LOCK 信号至少被断言一个时钟周期。在 TZASC 采样到 SECURE_BOOT_LOCK 为高电平后的一个时钟周期内,除非通过断言 ARESETn 重置 DREX,否则以下寄存器不能被写入。

断言 SECURE_BOOT_LOCK 信号使以下寄存器变为只读:

- TZASC 锁定选择寄存器

通过适当编程 TZASC 锁定选择寄存器并断言 SECURE_BOOT_LOCK 信号,使以下寄存器变为只读:

- TZASC 锁定范围寄存器