1)选中你的顶层文件右键点'New Source'

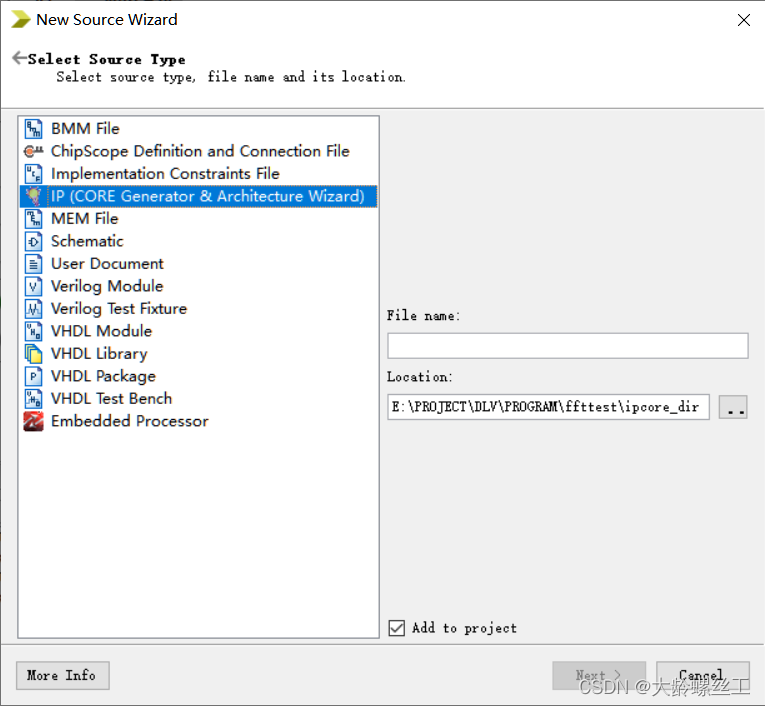

2)选IP CORE

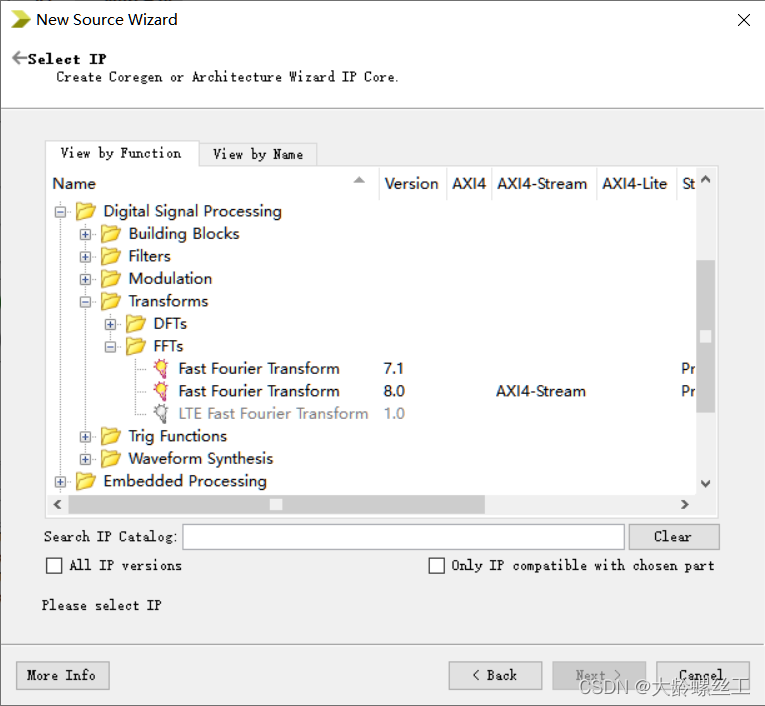

3) 然后输入你自己起的'file name',然后下一个界面就是找对应的IP核,如下图:

选Fast Fourier Transform 7.1然后NEXT,然后Finish。

4)然后IP核配置的第一页是选择通道和一次转换的数据长度,我选的是单通道1024,目标时钟我选100M,FFT的类型我选的PipeLine,Streaming I/O.这种方式叫流水线,就是可以一边输入时域信号一边输出频域信号,速度快一些。

5)然后下一页是你输入的数据宽度,我输入的数据宽度是16位,相位因子不管,然后缩放选项我选择的不缩放,输出数据顺序我选的是Natural Order,也就是自然顺序输出。Input Data Timing 我选的是No offset,就是IP核开始处理数据的时候对输入数据不产生延迟,不明白的话到时候仿真看一下就行,这

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?