2.3 TMS320VC33的CPU结构

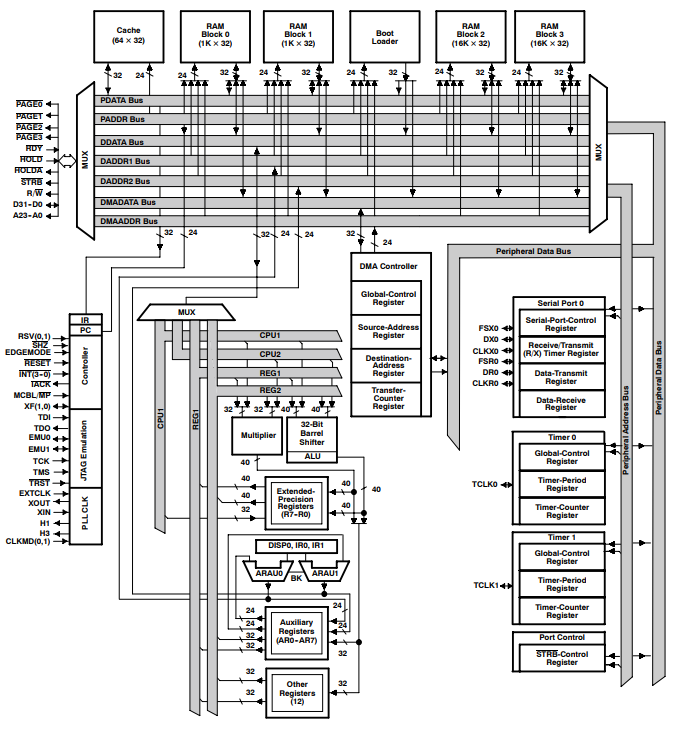

TMS320VC33是以寄存器为基础的CPU结构。CPU由以下几部分组成:

1. 乘法器(multiplier):对整数及浮点数进行乘法运算。TMS320VC33可在一个指令周期 内完成一次乘法和一次算术、逻辑运算。执行浮点乘法时,结果可以用40位浮点数表示,执行整数乘法时,结果用32位整数表示。

2. 算术和逻辑运算单元(Arithmetic Logic Unit,ALU):ALU对32位整数、32位逻辑及40位浮点数实现单周期操作,包括单周期的整数和浮点转换,此外还包括加法、减法、逻辑与、逻辑或等。它可以执行多种操作,并且通常也包括移位、比较和其他常见的算术逻辑运算。疑问解析:有算术逻辑运算单元后为什么还需要乘法器

3. 32位桶式移位器:桶式移位器在单周期内左移或右移的位数可高达32位。

4. CPU总线和寄存器总线:CPU总线(CPU1 bus,CPU2 bus)和寄存器总线(REG1 bus,REG2 bus)在一个指令周期内可从存储器读取两个操作数,同时从寄存器组读取2个操作数,从而可在单周期内对4个整数或浮点操作数进行并行的乘和加减。

5. 辅助寄存器运算单元(ARAUs):两个辅助寄存器运算单元(ARAU0和ARAU1)可在单周期内产生两个地址。ARAUs与乘法器及ALU并行操作。它们支持由立即数、索引寄存器IRO和IR1给出的带有偏移量的寻址方式,还支持专门用于相关运算、卷积、有限冲激响应(FIR)、无限冲激响应(IIR)、快速傅氏变换(FFT)等专门用于数字信号处理的循环寻址和位翻转寻址。

6. CPU寄存器组(包括28个寄存器):所有这些寄存器都可以被乘法器和ALU操作,既可用作通用寄存器,又可以实现一些特殊的功能。例如其中的8个扩展精度寄存器特别适合于进行扩展精度浮点数的运算,8个辅助寄存器支持各种间接寻址方式,并可用做通用的32位整数及逻辑寄存器,其余的寄存器提供诸如寻址、堆栈管理、中断及块重复等功能

2.3.1 注释

1、指令周期2、疑问解析:有算术逻辑运算单元后为什么还需要乘法器指令周期是计算机执行一条指令所需的时间周期。它通常包括取指令、译码、执行、访存和写回这几个阶段。在每个时钟周期内,计算机会完成这些阶段中的一个或多个。指令周期的长短取决于计算机的体系结构和性能。

虽然算术逻辑运算单元(ALU)可以执行各种基本的算术和逻辑操作,但乘法器仍然是必需的,原因如下:

- 性能和效率:乘法器通常是专门设计的硬件单元,能够以更高的速度执行乘法运算,相比在通用ALU中实现乘法操作,乘法器能够更快速地完成乘法运算,提高整体计算性能和效率。

- 复杂性和精度:乘法运算通常比较复杂,尤其是在处理大整数、浮点数或者高精度的数值时。专门设计的乘法器能够更好地处理这些情况,提供所需的精度和准确性。

- 资源分配:ALU的设计通常考虑了各种常见的算术和逻辑操作,包括加法、减法、逻辑与、逻辑或等。将乘法器作为单独的硬件单元,可以使得ALU更加简单和紧凑,并且专门优化乘法运算的乘法器可以使用更少的硬件资源来实现。

因此,虽然ALU能够执行多种操作,但乘法器作为一个专门设计的硬件单元,仍然是计算机体系结构中必不可少的组件之一,用于高效、准确地执行乘法运算。

2.4 总线结构及管理

计算机的总线结构可分为两种:

1. 冯.诺依曼结构:

2. 哈佛结构:程序和数据具有独立的存储空间,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址、独立访问,并有着各自独立的程序总线和数据总线,显然这使计算机的结构变得复杂,但优点是可以同时对数据和程序进行寻址,数据吞吐率提高了1倍,非常适合于进行实时的数字信号处理。

TI公司的DSP采用了改进的哈佛结构,即TMS320VC33既采用了独立的程序总线和数据总线,又在程序总线和数据总线中采用了交叉连接,允许数据存放在程序存储器中,并被算术运算指令直接使用,增强了芯片的灵活性,提高了运行速度

TMS320VC33有四种总线:程序总线、数据总线、DMA总线、外部总线,其中前三种总线统称为内部总线。

总线分类:

1. 内部总线:与CPU寄存器和程序计数器(PC)相关联的总线。其特点:程序总线与数据总线是分开的,地址总线与数据总线是分开的。具体划分{程序总线:程序的地址总线PADDR、程序的数据总线PDATA;数据总线:数据的地址总线DADDR1和DADDR2、数据的数据总线DDATA;DMA总线:DMA的地址总线DMAADD、DMA的数据总线DMADATA}。

程序计数器(PC)与24位的程序地址总线(PADDR)相连。索引寄存器(IR)与32位的程序数据总线(PDATA)相连。这些总线在每一机器周期内可读取一个指令字。

24位的数据地址总线(DADDR1和DADDR2)和32位数据的数据总线(DDATA),在每一机器周期中支持两次数据存储器的读写操作。DDATA总线通过CPU1和CPU2总线将数据传输到CPU。CPU1和CPU2在每一机器周期内可将两个操作数传送到乘法器、算术逻辑单元(ALU)及寄存器组。寄存器REG1和REG2在每一个机器周期内可将两个数据传送到乘法器。DMA设有专门的总线,由24位地址总线(DMAADD)和32位数据总线(DMADATA)构成,这些总线使DMA能与数据总线及程序总线并行地对存储器进行操作。

上述总线可使程序的读取、数据的存取和DMA操作并行地进行。这些总线可以对所有TMS320VC33支持的存储空间(片内存储器,片外存储器)和CPU寄存器进行寻址和数据存取。另外,需要说明的是,虽然上述内部总线结构是针对TMS320VC33介绍的,但也适应于其它TMS320C3x系列其它型号的DSP。

2. 外部总线:外部引脚通过==多路选择开关(MXU)==连接到内部总线上,简化了芯片的外部结构,同时也提高了DSP的性能。这种通过多路切换开关输出的总线称为外部总线。外部总线有两种,一是主总线,二是外围总线。虽然TMS320VC33并无扩展总线,但仍然将通过多路切换后通过外部引脚所体现的总线称为主总线。

主总线包括32位数据线、24位地址线、读写信号R/W、外部存取选通信号STRB(由地址线决定的)、页选通信号PAGE0~PAGE3(由芯片内的地址线A22和A23经过译码产生的)、就绪信号RDY(总线状态的控制信号)、保持信号HOLD(根据数据总线的输入输出状态而取不同的电平)、保持回答信号HOLDA(总线状态的控制信号)。

除主总线外,外部总线还包括外围总线(Peripheral Bus),这种总线也是通过多路切换开关输出的总线,主要用于对定时器、串行口控制寄存器和DMA寄存器的控制,这些寄存器是与CPU无关的寄存器,因而不属于CPU寄存器,也没有专门的寄存器名称,其地址在DSP的内部RAM中.

总线管理:

总线管理主要涉及外部总线的管理,达到访问外部存储器和外围器件的目的。通过主总线控制寄存器和使用外部输入信号,用户可控制总线的等待状态,从而允许CPU访问低速存储器和外围设备。

主总线接口控制寄存器的地址为:808064h,该寄存器为32位的寄存器。该寄存器结构及各位的功能如下图

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?