0 确定问题的讨论层级与范围

本文讨论的层次是

- 数字逻辑与Verilog HDL语言

讨论的范围是:

- 数据存储而不是讨论逻辑

1 线网类型

1.1 wire类型

这个暂时没什么好说的,一般常用的就是wire类型,需要注意的是:

- 默认是标量,相当于一个二进制位

- 不能随意存储数据,只能流通数据

- 可以使用向量和数组修饰进行拓展

2 寄存器类型

2.1 reg类型

2.1.1 关于无符号数的问题

先接受一个事实,声明为reg类型的寄存器为无符号数,integer和real类型为有符号数,请先接受这个事实,不要怀疑它,接下来我将通过实验为你验证它的确如此!

reg a = -4‘d9;

reg b = -4'sd9;

输出均为 7 也就是负数的补码对应的十进制数字

2.1.2 关于越界的问题——数据存储的通用法则

这与逻辑运算不同,不是非0即为1,遵循的规则是:

越界丢失

事实上,这条规则对于所有的需要使用数值的数据类型都适用,对于reg和net一类类型都一样的

简而言之,不能吃太饱,要是撑破了,多出来的部分就会归零。

例如:

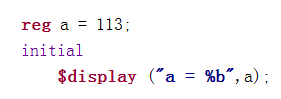

reg a = 112;

$display ("a = %b\n",a);

输出为:

a = 0;

因为a是一位,112的二进制为111 0000,故前几位丢失,只保留最后一位0

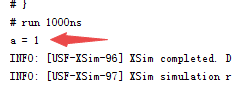

因此,如果a = 113那么将会被储存为1

得到输出结果:

扩展:多角度分析数值越界问题

2.1.3 关于补码的问题

计算机只要知道这是个补码,肯定会正确翻译出来一个负数,但是,得用正确的数据类型才行,否则依然不能正确翻译出来,比如对于负数,不能使用reg类型, 只能用integer或者real这种支持有符号数的数据类型!

2.2 integer类型

用来表示整数,可以有正负号

最小32位,轻易不用管它,不用指定位宽,按照默认就好,说了最小32位就是32位,指定31位也会变成32位,这种规则不要挑战,没有用的。

2.3 real类型

用来表示实数,即可以表述带小数点的数,可以有正负号

2.4 time类型

最小64位,与具体实现有关,用来表示时间,通常与$time配合使用

time sim_time = $time; // 存储当前仿真时间

2.5 小结

| 类型 | 使用 | 位宽 | 备注 | 字符串格式 |

|---|---|---|---|---|

| reg | 一般通用 | 默认为1 | 无符号数 | %b %B |

| integer | 整数 | 最小32位 | 有符号数 | %d %D |

| real | 实数 | 最小32位 | 有符号数 | %f %F |

| time | 仿真时间 | 最小64位 | 表示仿真时间 | %t %T |

注意:

- 以上4个类型中,只有reg类型能加向量修饰,以便于进行位宽的拓展integer和real类型与主机字的位数一致,与具体实现有关

- time位数与具体实现有关

- 字符串的显示看具体需求,无强制要求,上述只是列举了针对性对应的字符串

补充概念:计算机的字的位数

计算机位,字,字节,字长详解

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?