前段时间学习了一下带隙基准的基本概念,并搭建了一下书中带隙基准电路,计算器件参数,并进行了仿真,思考,具体参见如下。

单一的元件要么是正温度系数,要么是负温度系数,所以,单独使用一种电子元件是无法产生恒定输出的,我们需要做一些改变。

如果一个正温度系数的值与一个负温度系数的值相加,同时给它们一个特定的权重,那么我们就得到了一个零温度系数的值。

搭建电路结构如下:

双极晶体管的温度系数较好,呈现负温度系数。同时,若给两个双极性晶体管施加不同的电流,它们的电压差值就与绝对温度成正比,呈现正温度系数。利用这两者,就可以产生零温度系数的输出。

其中负温度系数电压VBE不变,其权重是1,需要用前面的正温度系数电压来抵消,从而实现零温度系数,可以看出lnn越大,那么R2/R1就可以取小,相反lnn越小,R2/R1就要取的大一些,总之要满足:M··R2=17.2。(这里不清楚为什么是17.2的话,可以看一下书本)

以上原理写得很粗略,会的不用看,不会的可能看不懂,具体原理介绍参考何乐年老师书中,解释的很详细

接下来开始搭建电路:

注意运放不要接反了,要让有电阻的一方是负反馈,用瞬时极性法判断,(例如+端,给一个增加的△V,那么输出变大,p管栅压变大,电流变小,从而Y点电压减小,使得+端电压又小了,所以是负反馈。)我第一次仿真的时候,运放就接反了,扫R1参数的时候,出来是错误的。

计算参数:

1、我们可以先确定三极管的并联个数,也就是n的取值,三极管并联个数影响的是电压差值△VBE,从而和电阻一起影响电流一般n取6、7、8,为了版图设计方便,取n=7,使得Q1、Q2、Q3比值为:1:7:1,可以得到一个3X3的三极管阵列。为啥n不取得更大呢,当n取8时,ln8=2.07,当n取7时,ln7=1.945,n=6时,ln6=1.79,差得不多,但是当n=20时候,ln20=2.99,差得明显,但是其面积会增加的很大,所以一般取n=6、7、8。我们取Q1:Q2:Q3=1:7:1。

2、接着我们根据功耗确定每条电路的电流,选每条支路的电流都是10μA,电流大小影响电阻R的取值,在功耗有余量的情况下,可以让电流大点,这样R取的就小点,从而在工艺角变化的时候,电阻不会偏差太多(工艺角对电阻的影响很大,不同工艺角下阻值会差很多)

3、设计运放:带隙里面的运放最重要的指标是增益,当然带宽大也好,(带宽要在确定带隙基准的管子尺寸后,先用理想运放仿一下,看看运放输出端的负载有多大,以此设计运放),这里我们用一个增益为10000(80dB)的理想运放

4、确定PMOS的尺寸:

①:可以给PMOS取一个过驱动电压(100~200mV),且由功耗知道电流,又知道工艺中的Kp(即μnCox),可以计算出W/L

②:也可以用gm/id的方法,负载电流管,减小噪声干扰,给gm/id取小一点,(看各个工艺,一般取6~8)同时给一个沟道长度L=2μm(抑制沟道长度调制效应),由对应的id/W可以得出W,这里不算了,大概给出合适的尺寸,W=6μm,L=2μm

5、确定R1的阻值:

R1决定了其支路的电流,因为前面定了支路电流为10μA,电压➗电阻=电流,我们通过扫描电阻R1阻值,看支路电流为10μA的情况下,阻值是多大,扫描的时候,看的是R1这一支路电流,所以可以将R2先设置为1K。我们跑DC,让VDD从0~3.3V变化,在Tools里选扫描参数,将R1从1K扫描到100K:

得到输出电流和电阻R1阻值的关系,这里我们确定R1的范围在4.6K附近,重新缩小范围继续扫描,从4K扫描到6K,扫描100个点

可以看到R1取值为5.03KK的时候,电流接近10μA,再逐次逼近,最终确定R1=5.049K

6、确定R2的阻值:

电阻R2主要确定电路的温度系数,(正温度系数的权重)这个时候输出电压是不随着电源电压变化而变化的了,就不再用扫描VDD了,why?

将扫描设置成DC扫描,DC里扫描温度,参数扫描里扫描R2的阻值,观察Vout的变化情况,看温度系数的权重是否正确,只有当vout不变的时候,权重才正确。从而可以得到不随温度变化的输出电压Vout

将VDD设置为3.3V,温度从-20~80℃扫描,R2从1K~100K扫描,得到随着温度的变化,不同阻值的R2情况下,输出电压的波动情况:

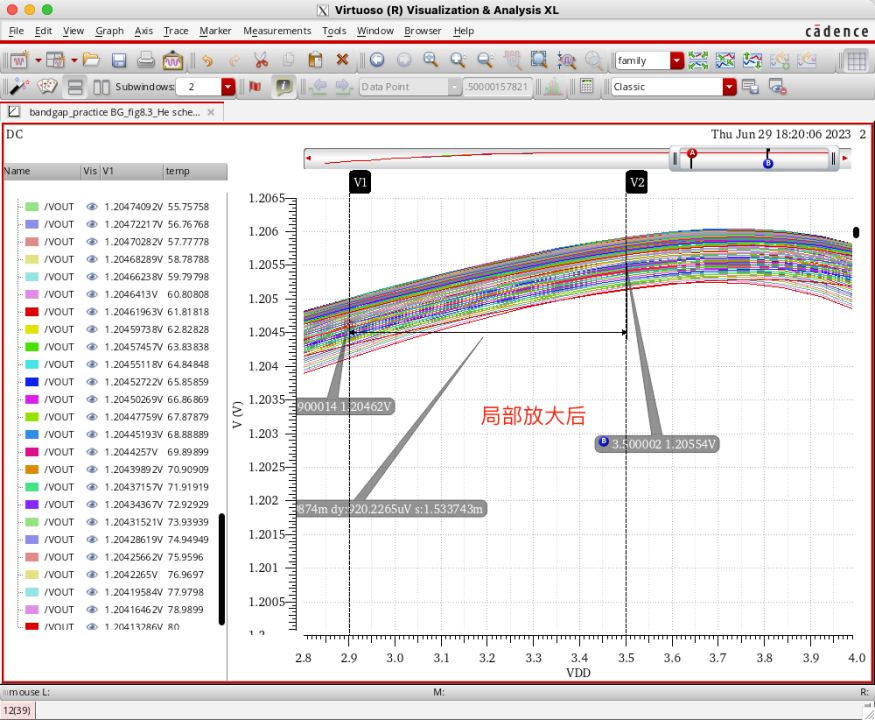

将阻值设置完成,仿真随温度变化和随电源电压变化,输出电压的波动程度:

可以看到,随着温度变化,输出电压的波动不超过1.9 mV

同样可以看到,在不同温度下,随着VDD的变化(当然VDD要使管子正常工作),在大概1.6V之后,其输出电压稳定,在-20~80℃的波动下,其输出电压只差了2.86mV。

接下来仿真其电源抑制比、温漂系数(注意不是温度系数)

温漂系数:衡量带隙基准电压源输出电压随温度变化的一个性能参数,注意是在一个温度点上获得零温度系数

单位为:ppm/℃ ,(1ppm=10^(-6)次方)。表示当温度变化1℃时,输出电压变化的百万分比。 其计算公式为:

我到这里没太明白是怎么测试?是在电源电压不变,即VDD=3.3V情况下,扫描温度从-20~80℃,然后找出Vout最大和最小,算平均值,然后带入上式计算吗?

如果是的话,那么VDD=3.3V,扫描温度-20~80℃,得到下图,

然后找最大值1.20027V,最小值1.19825V,差值为2.01801mV,平均值1.2V。

根据公式计算:温度系数为:16.82ppm/℃。是这样吗?总感觉不太对。

看了何乐年老师书上那部分仿真内容后,明确了ppm的概念,说的就是在某一电源电压下,例如3.3V,(因为VDD如何变对VOUT无影响,或者说影响很小,而温度漂移概念说的是,当温度改变后,对应输出电压的变化程度,自然而然就要求VDD不变(或者说VDD对VOUT的变化可忽略)

看老师的书后,也学会了利用Calculator计算温漂系数,找到最小温漂系数对应的电阻阻值R2。具体参考何乐年老师书中217页。在此不赘述公式的输入过程,直接上图:

(公式会列吧,不会可以看下何乐年老师的书)

所以我们修改R2的阻值=48.82K,完事继续仿真此状态下,VDD=3.3V,R1=5.049K,R2=48.82K,扫描温度从-20~80℃的输出电压变化。

可以看出最大和最小只差0.78mV

再扫描一下VDD从0~3.3(或许可以扫描从2~4V(稳定工作)),看看输出电压变化情况。

可以看到,当电源波动10%时,输出差不多变了1mV,我想这是正常的,是没办法,或者说不是我们该考虑的点,而是做电源管理的人该考虑的,他需要给我们提供一个好的电源模块。到这里,对于上述提到的ppm概念不清楚的问题迎刃而解

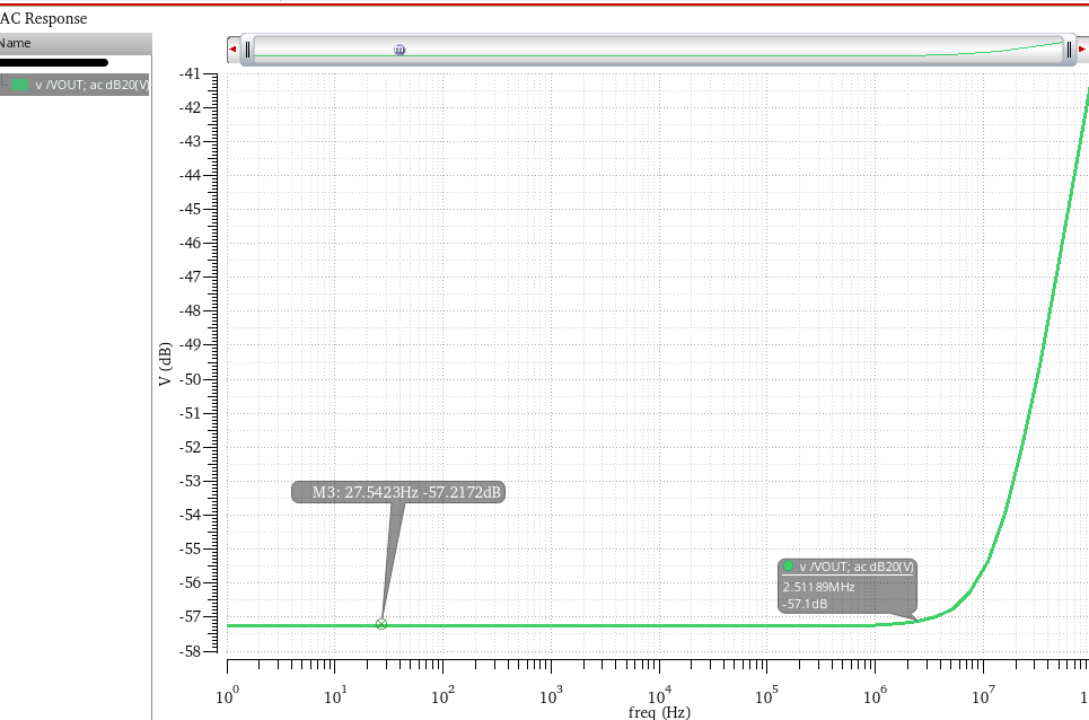

继续看psrr仿真

电源抑制比PSRR:

在VDD上添加一个1V的交流信号,然后进行ac仿真,频率扫描从1~100MHz就够了,仿真完后,mainform中选ac-voltage-dB20,然后点选输出节点,可以得到电源抑制比:

可以看到PSRR为:57dB,不高,带隙的PSRR在100dB以上才算高PSRR,但看应用背景,并不一定所有带隙都需要高PSRR。

启动电路和简并点分析暂时还没看书,之后看了有时间的话再补上。

文章介绍了带隙基准的基本概念,通过电路搭建和元件参数计算,实现了零温度系数的输出。作者强调了运放的负反馈作用,以及电阻和三极管的选择对电路性能的影响。通过仿真验证了在不同温度和电源电压下的稳定性,探讨了电源抑制比(PSRR)和温漂系数的计算方法。

文章介绍了带隙基准的基本概念,通过电路搭建和元件参数计算,实现了零温度系数的输出。作者强调了运放的负反馈作用,以及电阻和三极管的选择对电路性能的影响。通过仿真验证了在不同温度和电源电压下的稳定性,探讨了电源抑制比(PSRR)和温漂系数的计算方法。

1189

1189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?