一.74LS138芯片基本功能介绍

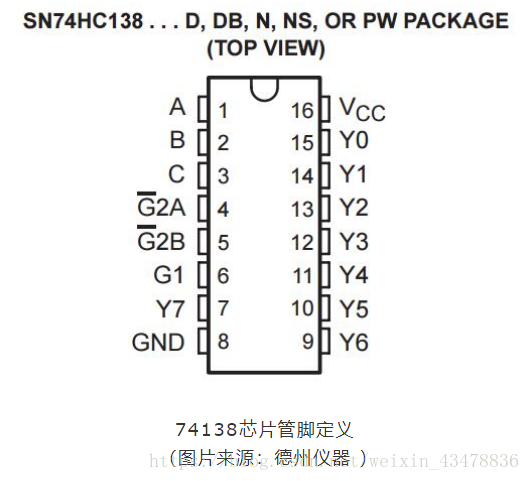

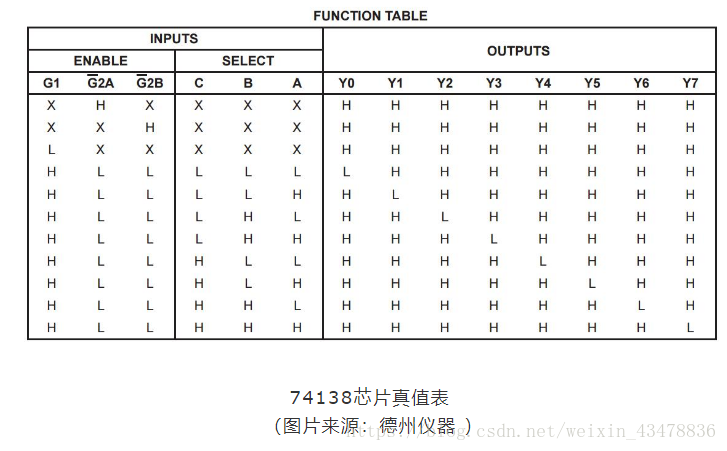

在数字集成电路的早期时代, 对于一些常用的小型逻辑, 比如3-8 译码器 会被集成进一颗芯片, 例如74138芯片就是一颗实现3-8译码器的常用组合逻辑芯片。 下图分别是74138芯片的管脚定义、真值表以及内部逻辑结构

二.利用74LS138实现4-16译码器

设计要求:

· 用2片3-8 译码器拼接成4-16 译码器

· 仿真验证电路的正确性

· 注意观察输出信号的毛刺(竞争冒险)

设计思路:

如下图所示,我们让最高位输入IN_D接到片1的G2BN,接到片2的G1,这样若IN_D=0,则上方的芯片被选中,下方芯片被禁用,若IN_D=1,则相反。

电路逻辑设计如下:

用QuartusⅡ进行功能性仿真后得:

用QuartusⅡ进行时序性仿真后得:

仿真结果符合预期,且出现了“毛刺”,即电路的冒险与竞争现象,这是由于逻辑门存在延迟以及信号的传输路径不同造成的,当输入信号电平发生瞬时变化时,电路就可能产生与稳态时不一致的错误输出。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?