1、Makefile中调用shell脚本

- Makefile中可以通过使用$(shell 指令)的方式调用shell脚本

- a指令:输出当前文件夹下的所有文件

- b指令:输出当前路径

- c指令:如果当前目录下不存在abc文件那么创建一个abc的文件

a=$(shell ls ./)

b=$(shell pwd)

filename=abc

# 如果不存在abc文件则创建一个abc文件

c:=$(shell if [ ! -f $(filename) ];then touch $(filename);fi;)

show:

@echo $(a)

@echo $(b)

@echo $(c)

clean:

${RM} abc

# make show 输出

Makefile

/home/xxx/xxxx/05-shell

2、Makefile中嵌套调用的多项目同时编译

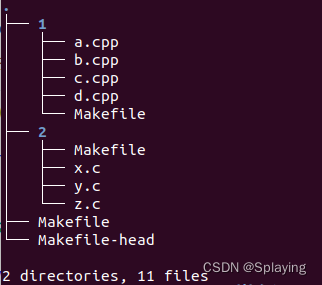

准备一个如下所示的文件夹:

- 文件夹1:4个.cpp文件,1个Makefile

- 文件夹2:3个.c文件,1个Makefile

- Makefile-head文件:1和2下的Makefile通过include 包含这个头文件(包含的本质是将代码拷贝过来),只不过Makefile-head是1和2都能用到的共同部分

- 主要目标是通过最外面的Makefile调用1和2下的Makefile

2.1 .1/Makefile、.2/Makefile、Makefile-head

- ./1/Makefile

tar=d

include ../Makefile-head

- ./2/Makefile

tar=z

include ../Makefile-head

- ./Makefile-head

src=$(wildcard ./*.cpp ./*.c)

obj =$(patsubst ./%.cpp,./%.o,$(src))

obj:=$(patsubst ./%.c,./%.o,$(obj))

$(tar):$(obj)

${CXX} $^ -o $@

clean:

${RM} $(tar) *.o

.PHONY: clean $(tar)

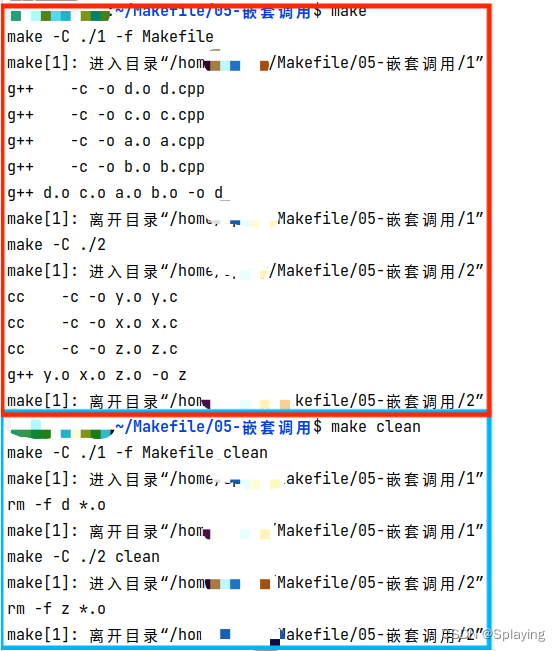

2.2、./Makefile

- make和$(MAKE)是同一个东西,不过是一个使用的系统常量

- 每个目标下的两条指令是相同的含义,只不过执行的路径不一样

a:

make -C ./1 -f Makefile

$(MAKE) -C ./2

clean:

make -C ./1 -f Makefile clean

$(MAKE) -C ./2 clean

2.3、改进

- 首先声明DIR指定需要执行的文件夹

- .PHONY是为了防止伪目标

- ALL: 表示需要生成的所有目标,依赖$(DIR)

- 然后$(DIR)需要通过嵌套调用的指令执行

- clean的过程是一个调用shell指令循环的过程

DIR=./1 ./2

.PHONY: 1 2

ALL: $(DIR)

$(DIR):

make -C $@ -f Makefile

clean:

@echo $(shell for dir in $(DIR); do make -C $$dir clean;done)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?