目标:由上节可知,要想得到FCLK = 400MHz,HCLK = 100MHz,PCLK = 50MHz的时钟需要配置两个寄存器,分别为MPLLCON和CLKDIVN

第一步:先对LOCKTIME初始化

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0,=0x4C000000

ldr r1,=0xFFFFFFFF

str r1,[r0]

第二步:对MPLL进行配置,配置为400MHz

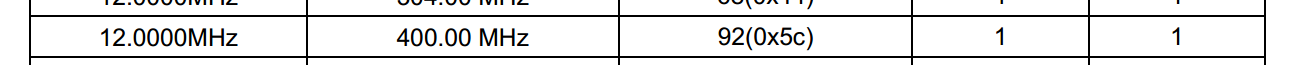

由以上公式可以推断:

MPLL = (2*(92+8)*12)/((1+2)*2^1) =400

m = 92+8 p=1+2 s=1

再配置也需注意

所以MPLL配置过程为

/*设置CPU工作于异步模式*/

mrc p15,0,r0,c1,c0,0

/*R1_nF:OR:R1_iA = #0xc0000000*/

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

/*设置MPLLCON(0x4C000004) = (0x5c << 12) | (1 << 4) | (1 << 0) */

ldr r0,=0x4C000004

ldr r1,=(0x5c << 12) | (1 << 4) | (1 << 0)

str r1,[r0]

第三步:配置CLKDIVN得到PCLK和HCLK的时钟分别为50MHz和100MHz

代码;

/* 设置MPLL 使FCLK : HCLK : PCLK = 400M : 100M ; 50M*/

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0,=0x4C000000

ldr r1,=0xFFFFFFFF

str r1,[r0]

/*设置CLKDIVN0(0x4C000014) = 0x5*/

ldr r0,=0x4C000014

ldr r1,=0x5

str r1,[r0]

注意:一旦设置了PLL,就会锁定lock time直到PLL输出稳定,然后CPU工作于新的频率

253

253

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?