JZ2440内部大致结构:

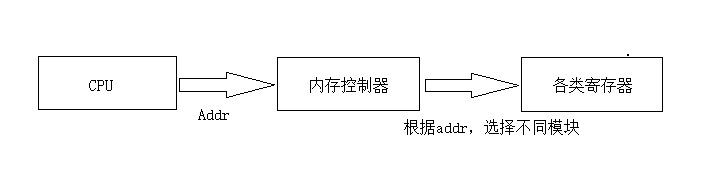

CPU把值写到外部寄存器,使外部寄存器发出不同的波形,控制相应设备,由此我们将提出,芯片内部如何选择不同寄存器的,所以芯片内部引入了内存控制器。

CPU发送地址信息给了内存控制器,内存控制器根据addr,选择不同的模块

内存类设备

内存类接口(NOR FLASH,DM9000,SDRAM)是不同的,CPU直接发送地址,数据给内存类设备,而JZ2440的外部有许多的内存类设备,而如何做到互不干扰的哪?每一个内存类设备都有一片选控制端CS(chip select),用来控制开启那个内存类设备,而片选控制端CS的信号发出,是由内存控制器管理,CPU发出地址信息给了内存控制器,内存控制器根据地址发出片选信号。

假如CPU发出的地址处于0x30000000~0x38000000,此时nGCS6发出低电平,也就选择了SDRAM

每一个片选信号

GPIO寄存器,UART寄存器,I2C寄存器,NAND控制寄存器,内存类设备(NOR FLASH;DM9000;SDRAM)等属于CPU的统一编址,而NAND FLASH由NAND寄存器控制,不参与统一编址,NAND寄存器控制向NAND FLASH发出CS信号。

每一个片选信号可选择的地址范围为2^27至少需要27根地址线

CPU将32位的地址发送到内存控制器,内存控制器:①根据地址发出片选信号;②取出27位用于控制外设

3850

3850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?