今天给大家分享一个在使用orcad 导网表出现的一个超级难搞的问题,这么多年来我碰到了2次,第一次大概是一年前,当时为了搞定这个问题,花了我整整2周多的时间,才把网表导出来,前段时间我正好又碰到了,有了上次的经验,这次半天时间就搞定了。当我刚碰到这个问题的时候,第一时间就是到网上去寻找有没有人碰到同样的问题,在网上搜了一圈也没有找到同类的问题,所以今天就在这里做一个简单的分享。

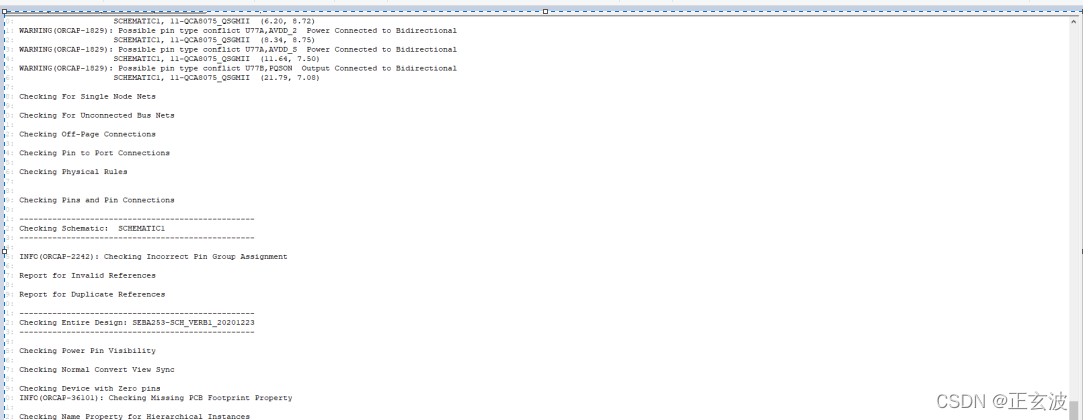

一般按正常流程,我们导网表,只要做完DRC,没有报错,我们就可以正常导出网表,但是这个问题奇怪的地方就在DRC没有报错,网表也是导不出来。我们先看下DRC的报告如下:

从这个报告里面,我们可以看到很多警告,这些警告主要是一些PIN脚的属性定义问题,可能与实际电路不匹配,这种问题一般都是参考设计的封装引入的,经过大量实践证明,这种警告没有什么影响。我们可以直接忽略跳过。

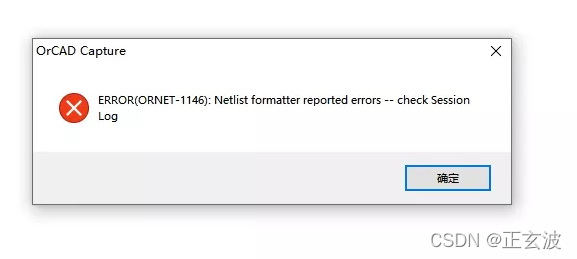

按照目前我们这个DRC结果,理论上是可以导出网表的,但是导网表时直接弹出报错框,报错信息如下:

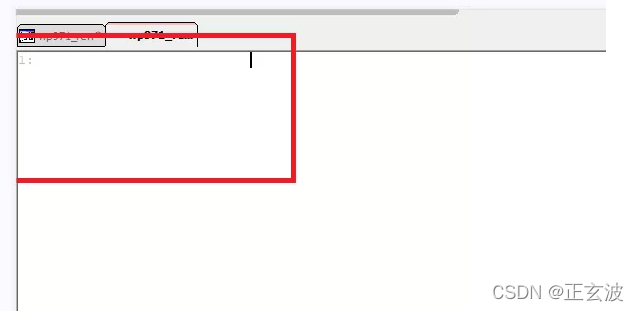

大致意思就是网络清单格式错误,让我们查看log.于是打开网表的那个文档,我们就看到这样的内容,如下截图:

当我第一次看到这个log,瞬间就傻眼了,就打印一个“1:”,没有其它任何提示,一般报错都会提示你那个地方有错误,然后我们对照查找,一般都能搞定。这正是这个问题难搞的地方,完全没有思路。

反正解决这个问题我也是各种试,后面也算机缘巧合,正好试出来了。这里我就直接给出问题原因,给出一个解决问题的思路。

问题原因:原理图中某一个器件有问题(具体有什么问题,我目前也还是不清楚),需要删除这个器件,重新新建一下。一般都可以消除这个问题。

总结:1. 我们经常做项目,一般会有很多成熟的电路模块,当再做一个新项目时,我们就会拷贝各种成熟的电路模块,这个问题,就是这样引出的,奇怪的地方就是在其它项目里,也是不报错的。

2.碰到这个问题,我们就需要根据自己实际情况,做减法,一步步减掉添加的部分,不停的重复DRC,导网表,直到最终定位某一页图纸,某一个部分原理图,某一个器件为止。

3.我们平时做一份原理图的时候,尽量做规范,方便以后直接拷贝调用,这样也能尽可能的减少不必要的麻烦,提高我们的工作效率。针对我碰到的这个问题,就是一个体力活,费时费力。

更多文章,欢迎关注硬件那些事儿微信公总号!

本文分享了一个在OrCAD中导出网表时遇到的棘手问题及解决方法。即使DRC检查未报错,网表仍无法导出。通过排除法最终定位到问题所在的具体器件。

本文分享了一个在OrCAD中导出网表时遇到的棘手问题及解决方法。即使DRC检查未报错,网表仍无法导出。通过排除法最终定位到问题所在的具体器件。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?