FIR 滤波器

FIR滤波器表达式为

Verilog编程实现

具体参考菜鸟教程的Veilog并行FIR滤波器设计。链接如下。

7.2Verilog并行FIR滤波器设计

本文着重介绍使用Vivado中的FIR IP核设计滤波器并补充一下其他知识。

IP核实现

使用IP核设计实现一下上述滤波器。

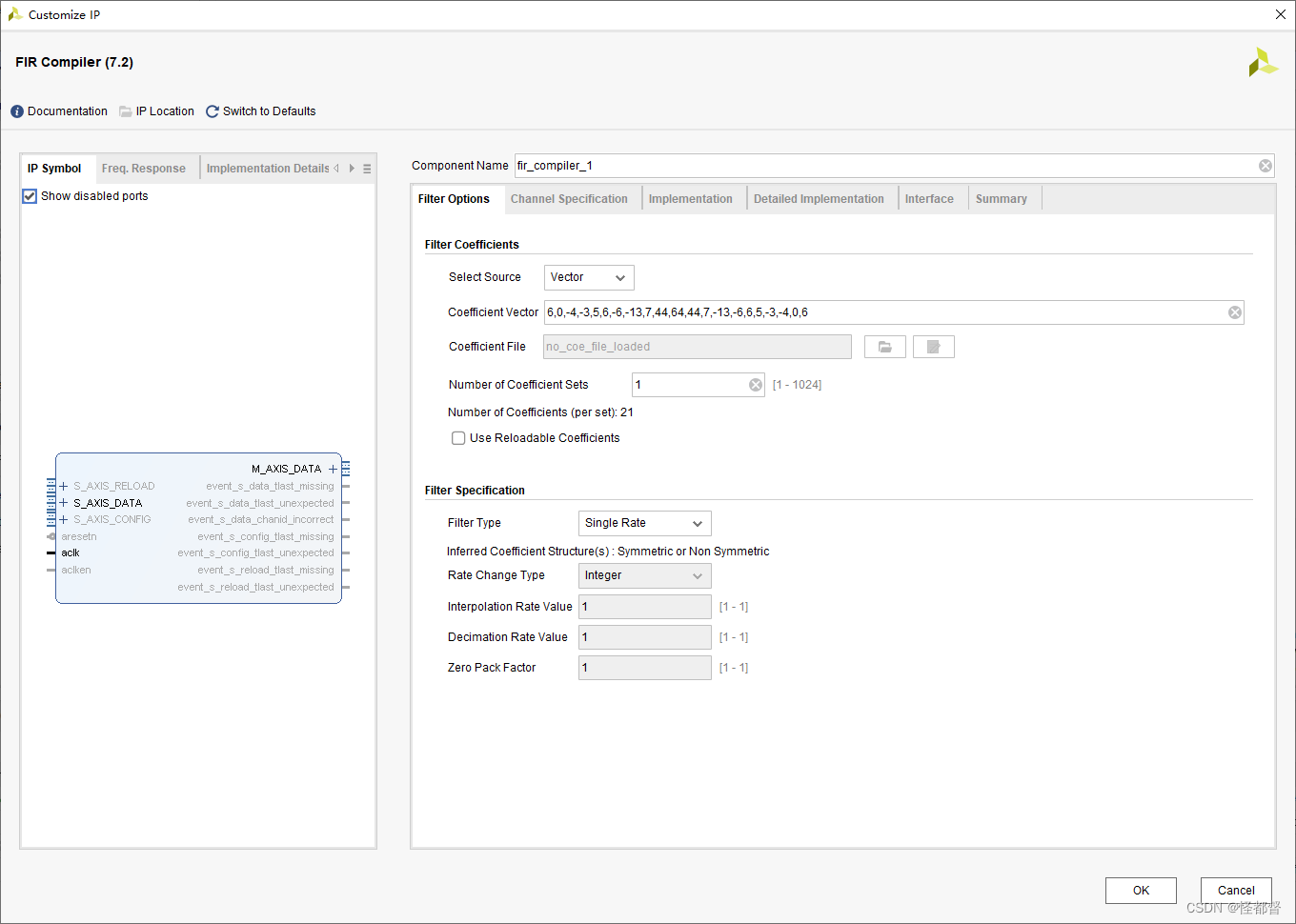

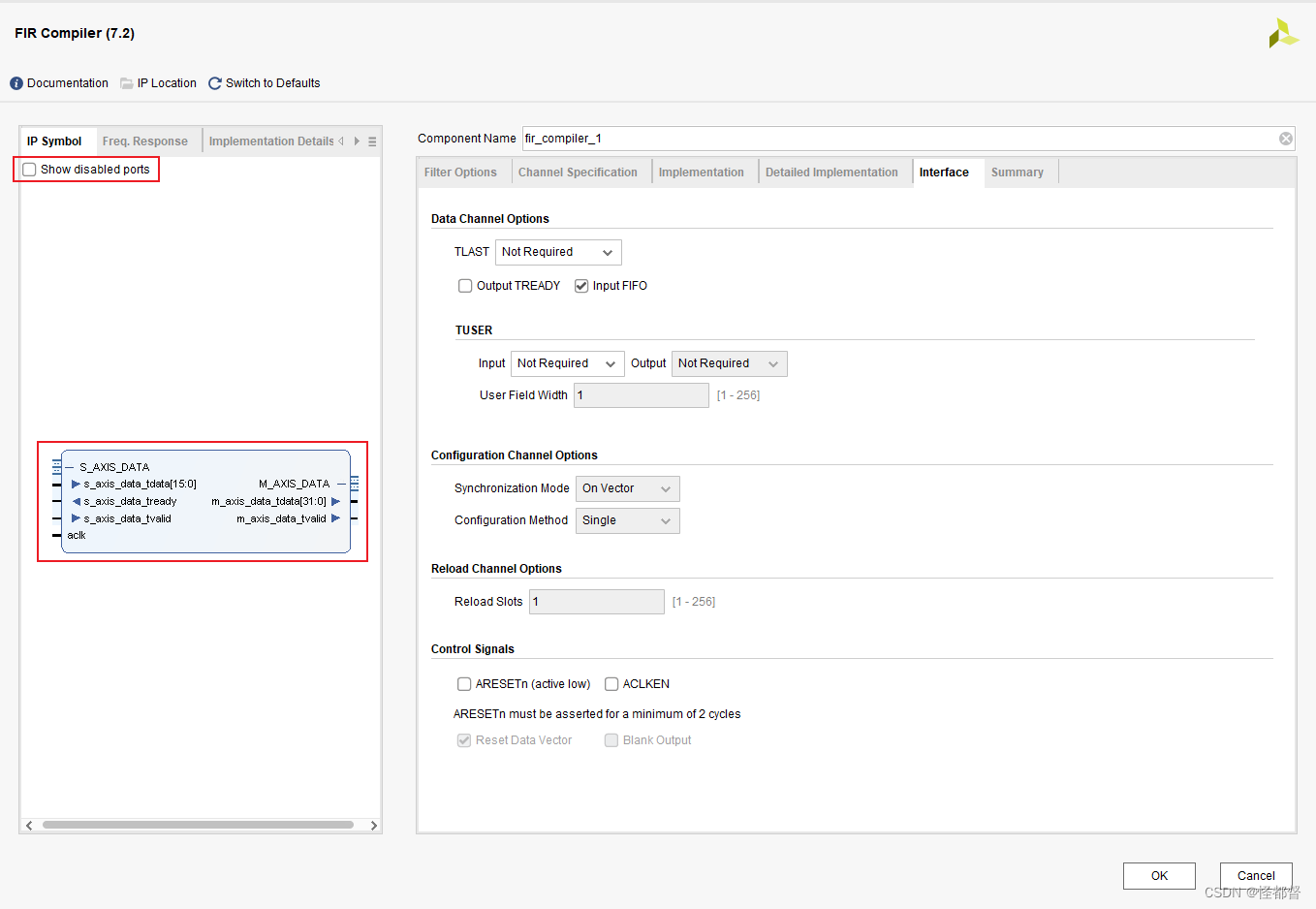

打开FIR Compiler,进入如下界面。

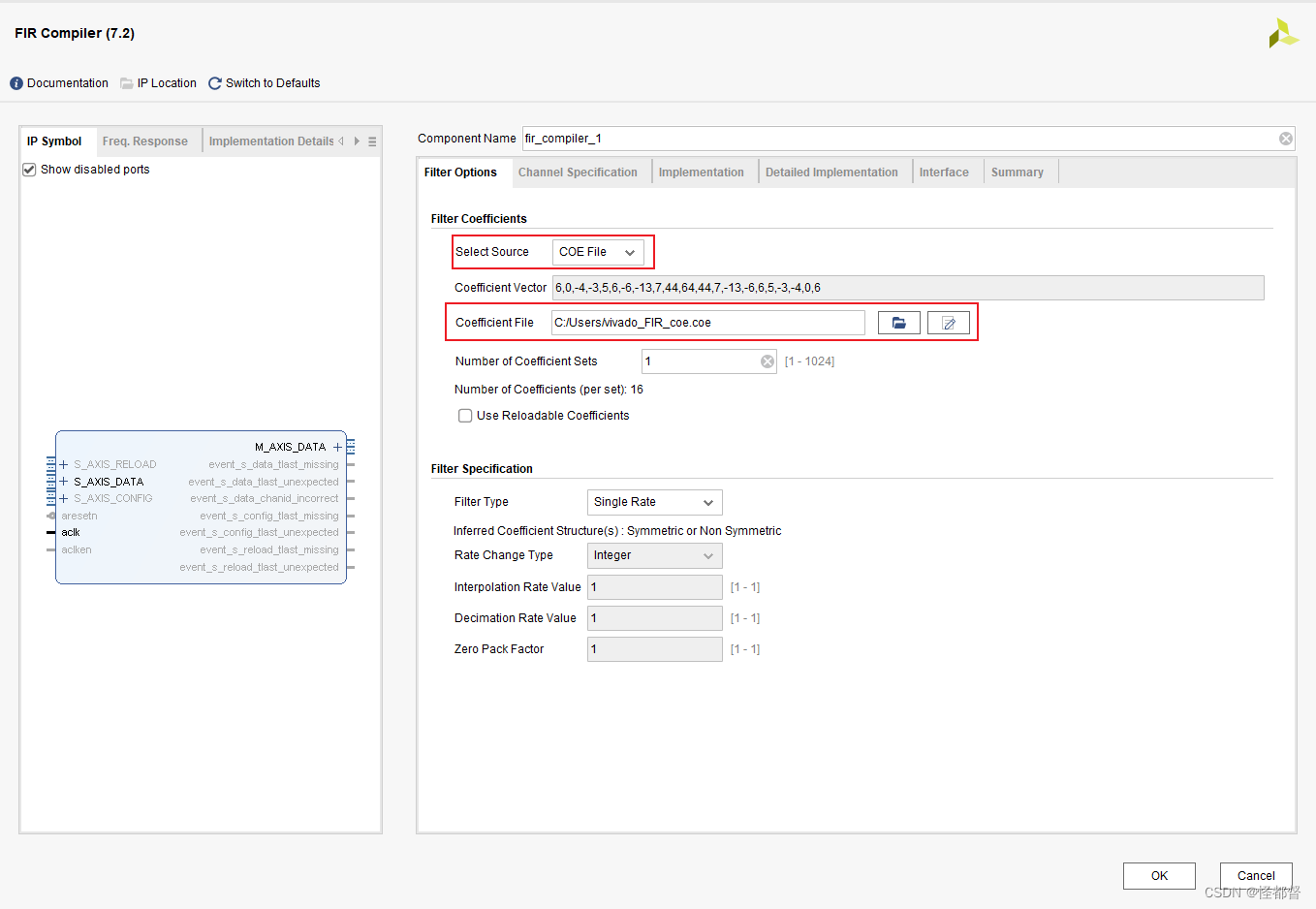

在Select Source选项中选择COE File,并选择COE文件。(也可以选择Vector后,直接将数据复制到Coefficient Vector框中)

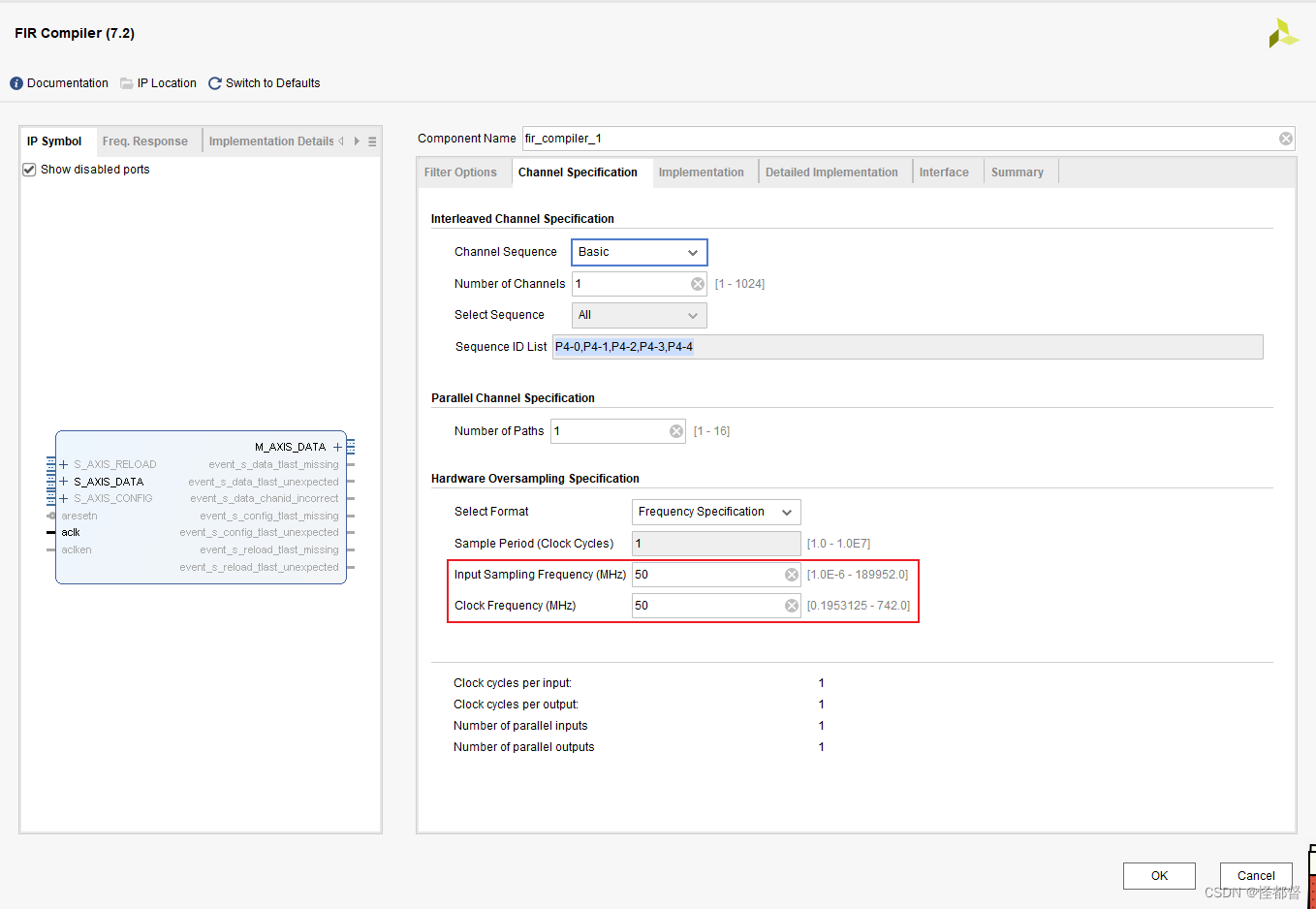

设置输入采样频率和时钟频率。

设置系数类型、量化方式、位宽,以及输入数据类型、位宽、小数位。其中Coefficient Quantization,可选Integer Coefficients、Quantize Only、Maximize Dynamic Range。当指定Radix=2(二进制)或16(十六进制)时,只有该选项可用,因为这些系数被认为已经被量化。当使用整数指定系数时,所有量化选项都可用。当使用非整数十进制(包含小数信息)指定系数时,仅量化和最大动态范围选项可用。

- Integer Coefficients整数系数,整数系数量化选项分析系数并确定表示系数所需的最小位数。

- Quantize Only仅量化,主要用于在使用非整数实数指定滤波器系数时使用,此选项将系数量化为指定的系数位宽。使用简单的向零舍入算法将系数值四舍五入到最接近的量程。系数字分为整数位和小数位。通过分析滤波器系数以找到最大整数值来确定整数宽度。剩余的位被分配来表示系数值的小数部分。

- Maximize Dynamic Range最大化动态范围,该选项来选择缩放系数以利用系数位宽提供的完整动态范围。如果选择,这将导致滤波器系数按公用因子按比例放大,以使最大系数(通常是中心抽头)等于使用所选位宽的最大可表示值,然后进行量化。总比例因子计算为缩放系数和量化系数之和与原始(理想)系数之和的比率。

设置接口,可取消勾选左上角Show disabled ports,即可在左侧看到该模块接口示意图,可以根据左侧选项添加其他控制接口,详情见AXI4-Stream接口协议。这里先生成一个最简单的模块用于仿真测试。

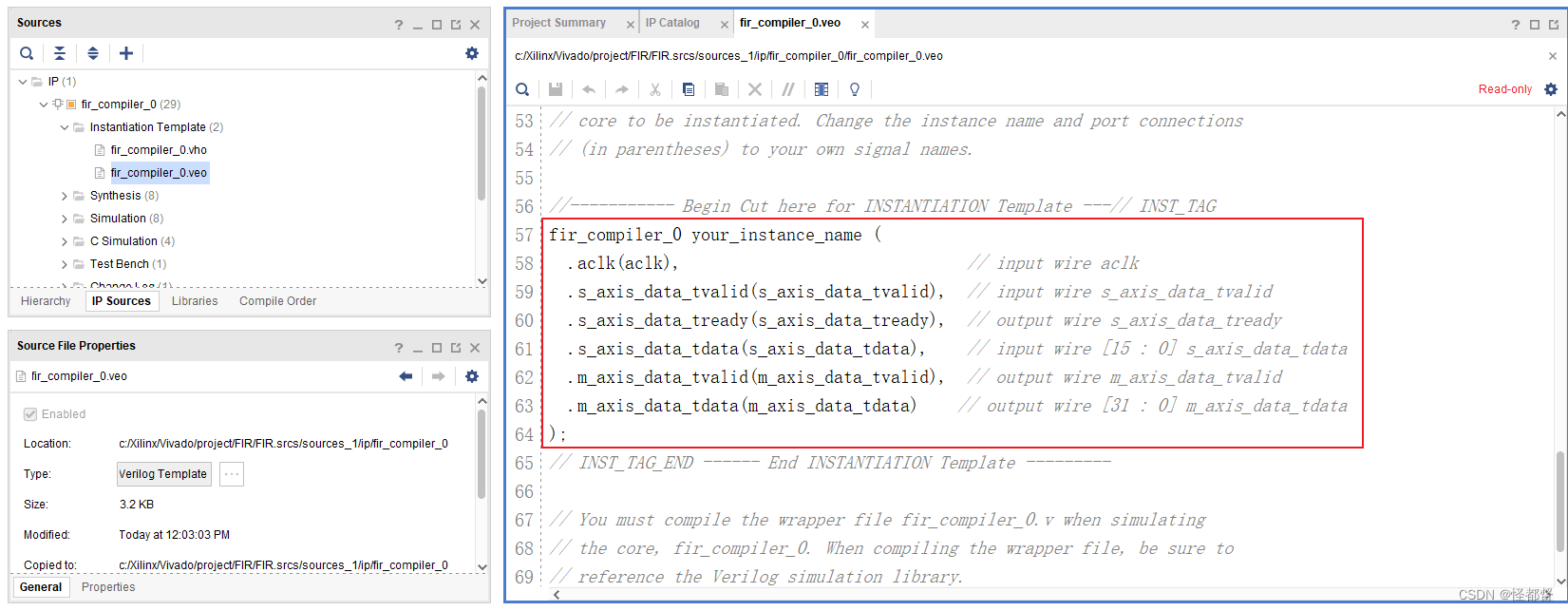

在Sources窗口中IP Sources中找到fir_compiler.evo文件,可看到该模块例化模板。

新建仿真文件,其内容如下。为了便于对比,其中输入数据文件直接使用了菜鸟教程中7.2Veilog并行FIR滤波器设计的文件。

`timescale 1ns / 1ps

module FIR_sim;

//input

reg clk;

reg s_tvalid;

reg [15:0] s_tdata;

//output

wire m_tvalid;

wire [31:0] m_tdata;

initial begin

clk = 1'b0;

forever begin

# 10;

clk = ~clk;

end

end

reg [11:0] data_in[0:200-1];

integer i;

initial begin

$readmemh("C:/Xilinx/Vivado/project/FIR/fir_para/cosx0p25m7p5m12bit.txt",data_in);

i = 0;

s_tvalid = 1'b1;

s_tdata = 0;

# 5;

forever begin

@(negedge clk) begin

s_tdata = data_in[i];

if (i == 200-1) begin

i = 0;

end

else begin

i = i + 1;

end

end

end

end

fir_compiler_0 your_instance_name (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata(s_tdata), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_tdata) // output wire [31 : 0] m_axis_data_tdata

);

endmodule

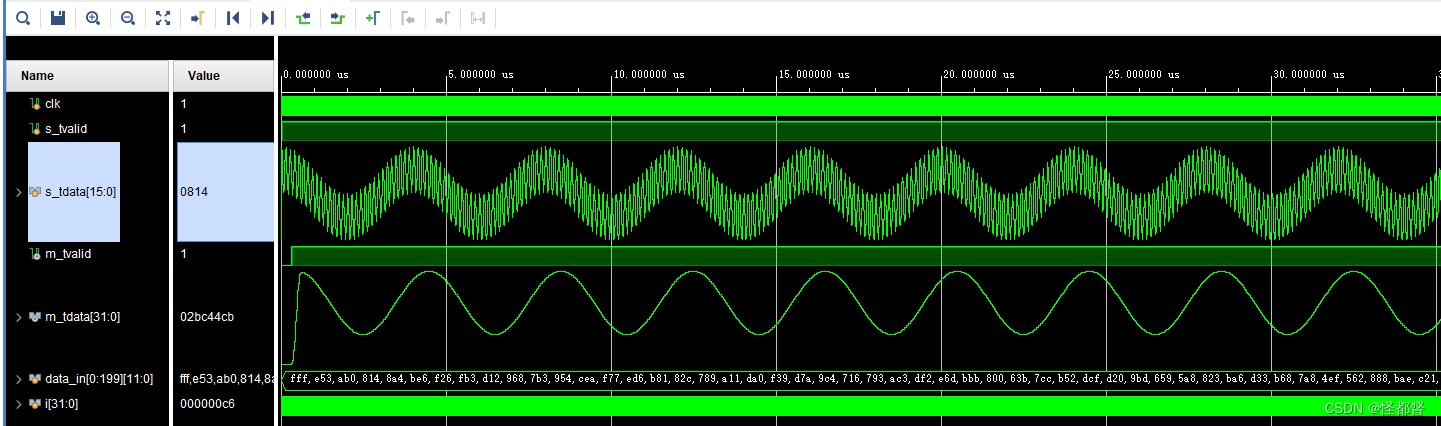

保存文件后,点击Run Simulation,其仿真结果如下。

右键变量名字,点击Waveform Style->Analog,可将数据显示为模拟波形。

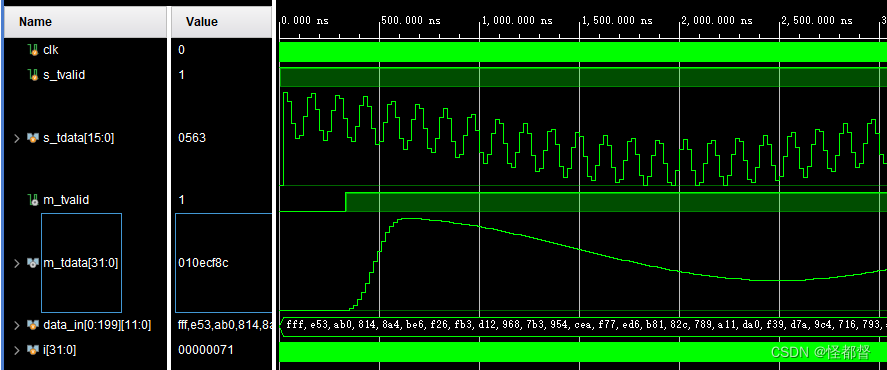

点击Waveform->Analog Settings,更改Interpolation style为Hold。可将波形显示为阶梯状。效果如下。

至此,可以看到使用IP核设计的FIR低通滤波器成功实现了功能。

Matalb设计滤波器

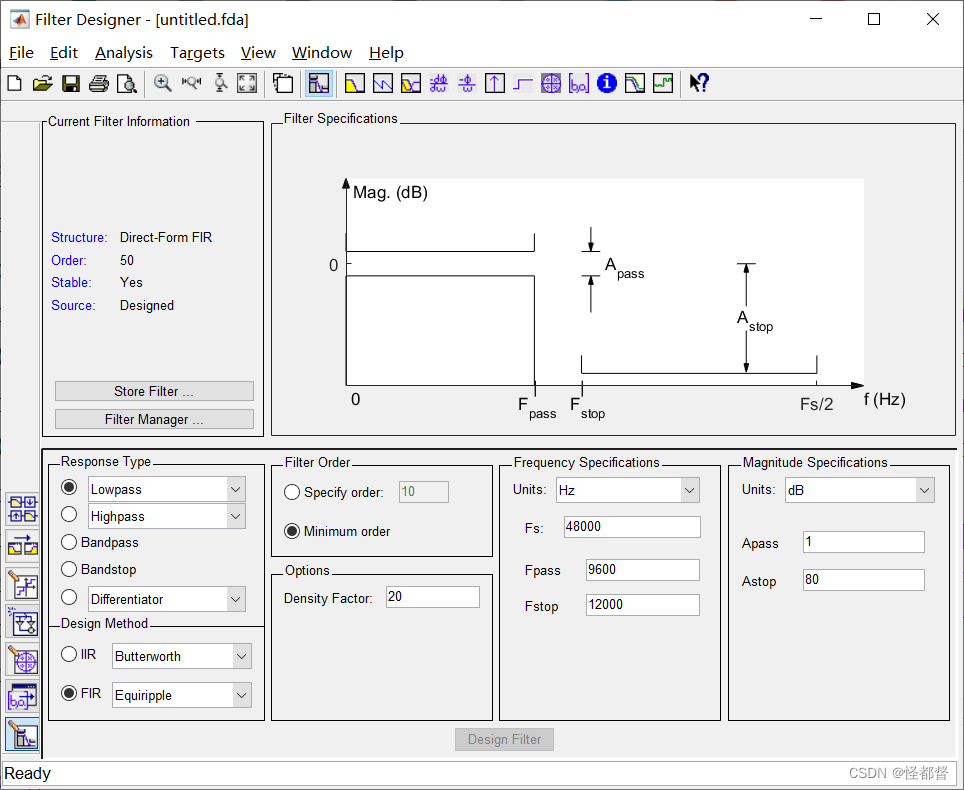

在Matlab的工具箱找到Filter Designer,并打开后界面如下。

根据滤波器设计需求,设置相应的参数。更改参数后,点击Design Filter生成滤波器。

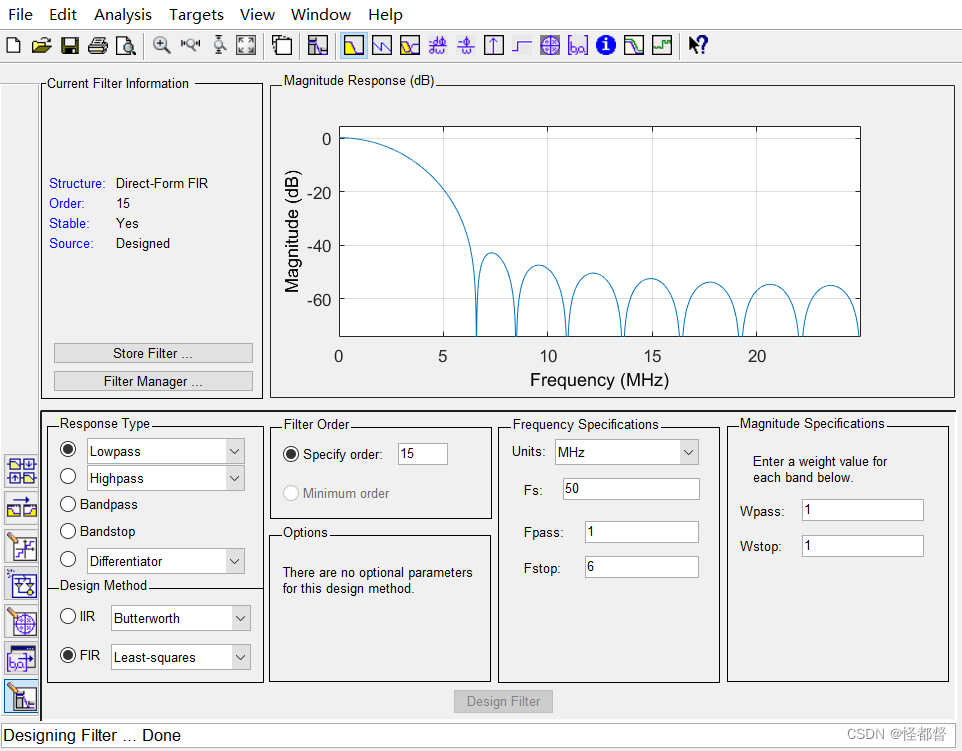

如设计15阶FIR滤波器,实现方法选择Least-squares,设置采样频率为50MHz,通带起始频率为1MHz,阻带起始频率为6MHz。

导出用于Xilinx FIR IP核所需滤波器系数,有两种方法。

方法一,在上图页面中点击File->Export,进入如下界面。

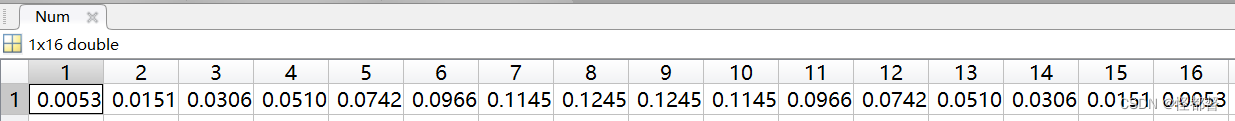

默认导出到工作区,默认变量名为Num。点击Export后查看该变量为

接下来可以使用如下Matlab代码对系数矩阵进行量化并写入coe文件。

%Matlab

q_width = 12;%量化位宽

fid = fopen('FIR_coe.coe','w');

coe_data = round(Num/max(abs(Num))*(2^(q_width-1)));

fprintf(fid,'Radix = 16;\r\n');%十六进制

fprintf(fid,'Coefficient_Width = %d;\r\n',q_width);

fprintf(fid,'CoefData = \r\n');

fprintf(fid,'%x,\r\n',coe_data);

fclose(fid);

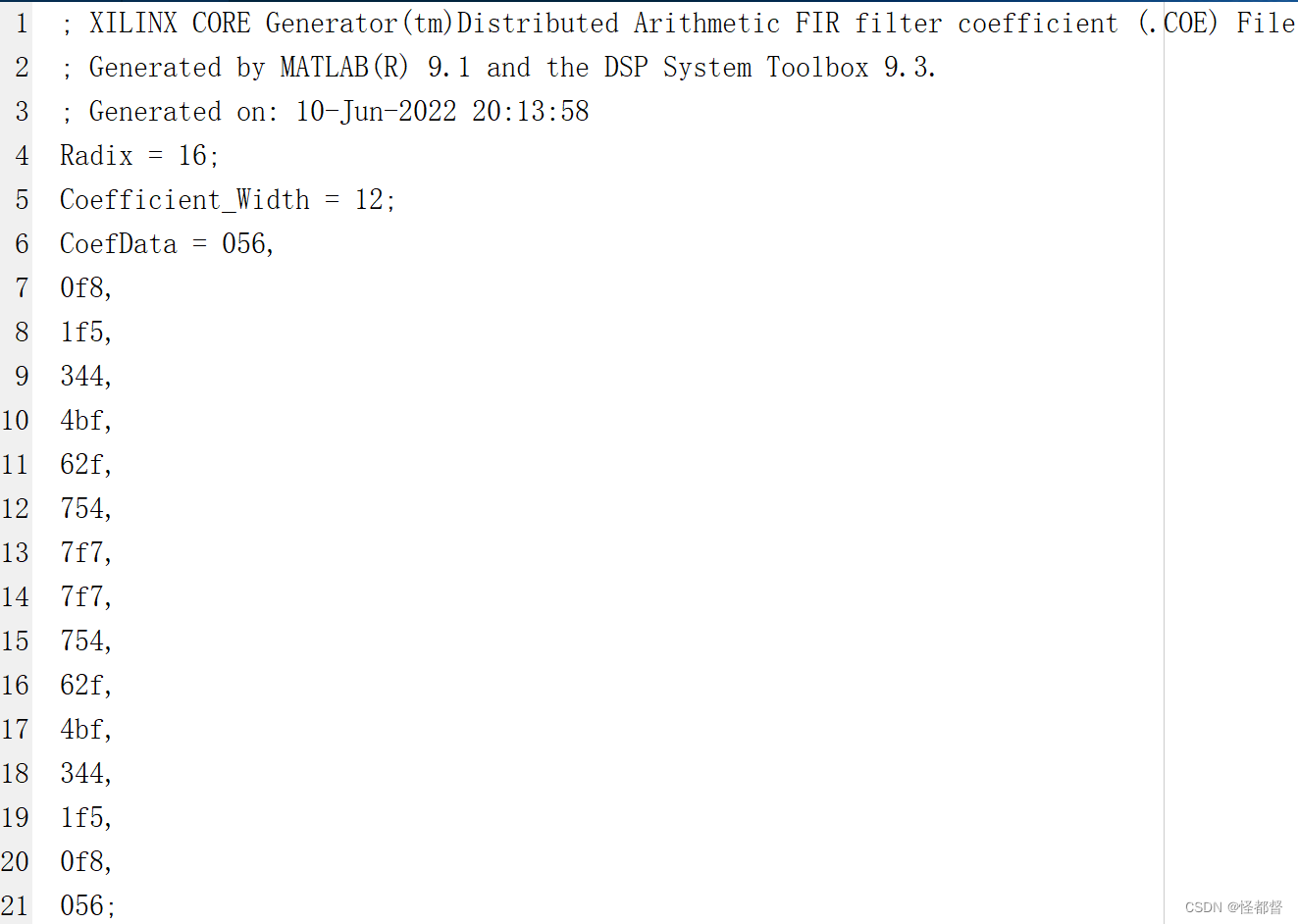

运行上述代码即可得到如下文件内容。

将19行处数据末尾逗号替换成分号 ,即可得到可使用的coe文件,同方法二生成的一样。

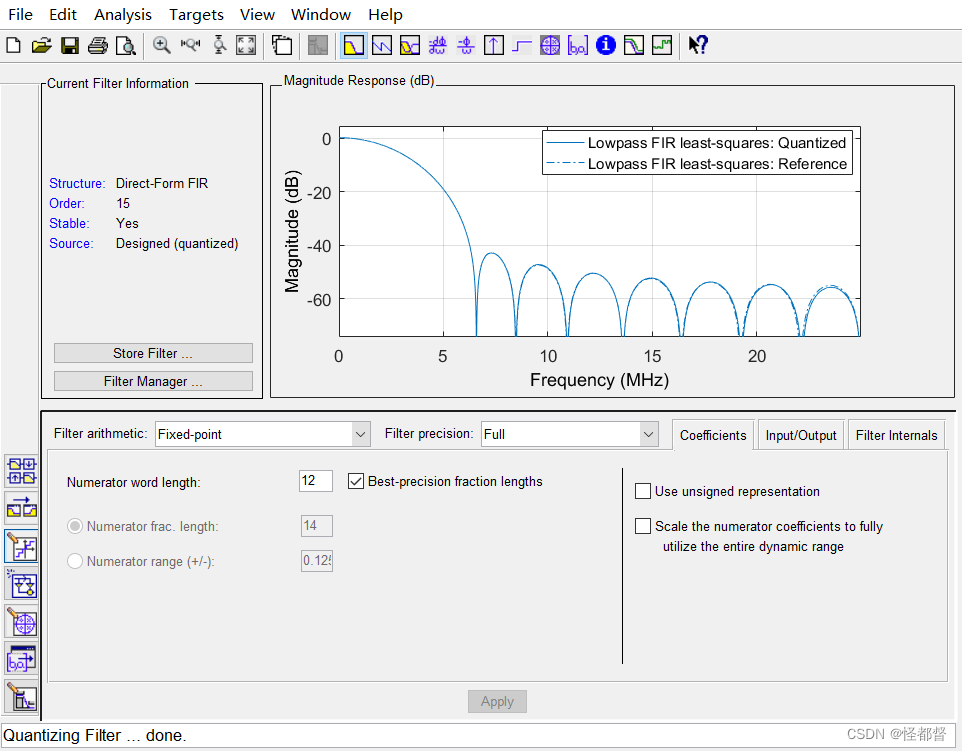

方法二,点击在Filter Designer主页面点击Set quantization parameters按钮(其位置如下图箭头所指)进入如下界面。

选择Fixed-point,并设置字长为12位后,点击Apply。

接着点击Targets->Xilinx Coefficient,设置好coe文件名并保存。该文件打开后内容如下。

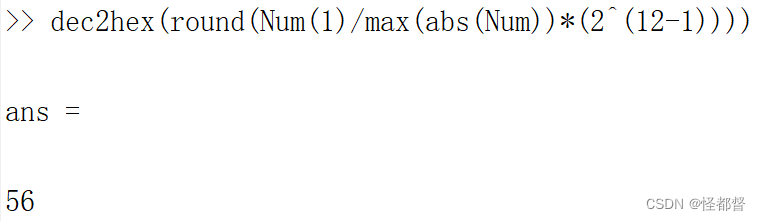

以第一个CoefData数据0x056为例,对应上面生成的Num(1) = 0.0053。通过以下Matlab程序代码可验证其量化方式。中间有一些数据使用该方法量化和生成的coe文件数据有一些小误差。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?