一、课程设计的内容

通过学习掌握使用可编程逻辑器件和QuartusII 软件的基本使用,利用QuartusII

软件各种器件进行多路智力竞赛抢答器设计;利用DE2板对所设计的电路进行验证;总结电路设计结果。

通过设计掌握基本工程设计方法,提高动手能力。

二、课程设计的要求与数据

八位数字抢答器设计要求:

1). 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2). 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3).

抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

4).

抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如,30秒)。当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

5).

参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6).

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

三、课程设计应完成的工作

利用QuartusII 软件各种器件画出八位数字抢答器的原理图。

对原理图进行编译修改错误;设计引脚,再重新编译;进行仿真,根据仿真结果观察设计是否符合设计要求。

然后加载到DE2板上,验证电路是否正确。

对设计进行优化、完善。

附加要求:

写出设计的VHDL源程序,利用QuartusII 软件生成原理图。

进行编译修改错误;设计引脚,再重新编译;进行仿真,根据仿真结果观察设计是否符合设计要求。

然后加载到DE2板上,验证电路是否正确。

五、应收集的资料及主要参考文献

**《现代电子技术实践课程指导》**谢云 等 主编,机械工业出版社

**《SOPC技术与应用》**江国强,机械工业出版社,2006年10月

**《EDA技术与应用》**江国强,电子工业出版社,2007年1月

《FPGA与SOPC设计教程: DE2实践》

张志刚编著. - 西安: 西安电子科技大学出版社, 2007.334页+光盘1片

摘 要

学习利用使用可编程逻辑器件和QUARTUS

II软件,用原理图方法设计一个八位抢答器,利用DE2板对所设计的电路进行验证。抢答器基本功能:一是能分辨出选手操作按键的先后,并锁存优先抢答者的编号,供译码显示电路用;二是要使其他选手的按键操作无效;三是具有计时功能,时间到则抢答无效。根据要求抢答器分为两个部分:一是抢答显示电路;二是倒计时显示电路。抢答电路部分可以用用VHDL编写源程序实现抢答锁存功能,而倒计时显示电路可用74HC192和74HC48器件实现预置数倒计时。通过课程设计掌握工程的基本设计方法,提高动手能力;加强对自己专业的了解和认识。深化专业知识,为以从事相关工作打下基础。

1 设计任务目的及要求

1.1设计任务

1)利用各种器件设计一个多路智力竞赛抢答器。

2)利用DE2板对所设计的电路进行验证。

3)总结电路设计结果

1.2设计要求

1). 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2). 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3).

抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

4).

抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如,30秒)。当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

5).

参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6).

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

2 原理与模块介绍

2.1 设计模块

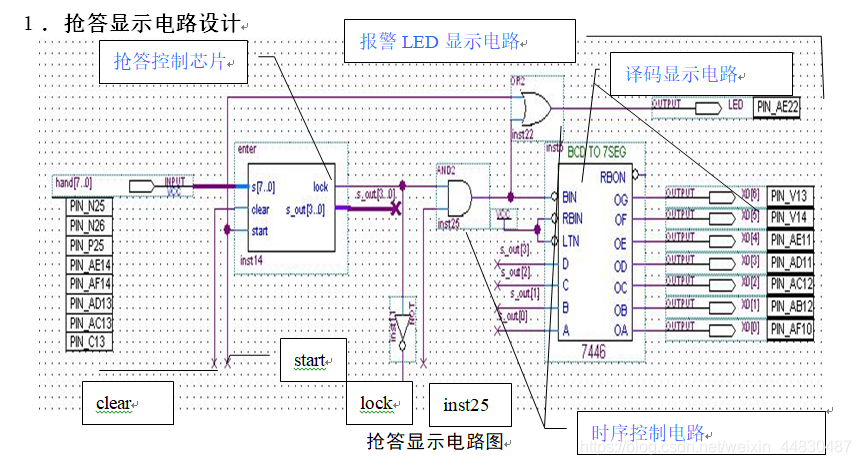

报警LED显示电路

inst2525

clear

start

lock

译码显示电路

时序控制电路

抢答控制芯片

抢答显示电路图

抢答电路的功能有三个:一是能分辨出选手操作按键的先后,并锁存优先抢答者的编号,供译码显示电路用;二是要使其他选手的按键操作无效;三是按下开始按键(采用高电平触发按键)LED**(LEDG[0])闪烁,并且抢答后LED(LEDG[0])**亮(不灭)以此说明抢答成功。

为了实现以上功能可以编写VHDL源程序,生成原理图。显示采用74HC46译码器。

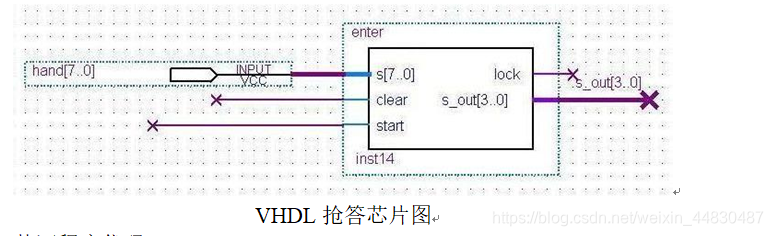

VHDL抢答芯片图

其源程序代码:LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

entity enter is

port( s:in std_logic_vector(7 downto 0);

clear,start:in std_logic;

lock:buffer std_logic;

s_out:out std_logic_vector(3 downto 0) );

end enter;

ARCHITECTURE s_enter of enter is

signal sig_start:std_logic;

begin

process(s,clear,start)

begin

if clear=‘1’ then

lock<=‘0’;

sig_start<=‘0’;

s_out<=“0000”;

elsif start=‘1’ then

sig_start<=‘1’;

elsif (lock=‘0’ and sig_start=‘1’) then

if s(0)=‘1’ then s_out<=“0001”;lock<=‘1’;

elsif s(1)=‘1’ then s_out<=“0010”;lock<=‘1’;

elsif s(2)=‘1’ then s_out<=“0011”;lock<=‘1’;

elsif s(3)=‘1’ then s_out<=“0100”;lock<=‘1’;

elsif s(4)=‘1’ then s_out<=“0101”;lock<=‘1’;

elsif s(5)=‘1’ then s_out<=“0110”;lock<=‘1’;

elsif s(6)=‘1’ then s_out<=“0111”;lock<=‘1’;

elsif s(7)=‘1’ then s_out<=“1000”;lock<=‘1’;

end if;

end if;

end process;

end s_enter;

其功能描述如下:

输入s[7…0]为1至8号抢答按键(输入)。

输出s_out[3…0]

输出优先抢答者的编号,供译码显示电路使用且使其他选手的按键操作无效。

输入clear(KEY[0])是低电平触发按键,实现清零功能,输入start是连接低电平触发按键begin(KEY[1]),供主持人使用。

输出lock。当有人抢答后输出为“1”,否为“0”实现译码显示电路处于灭零或工作状态,同时也能实现倒计时停止的功能。

抢答显示电路工作原理:

主持人按下clear(KEY[0])按键,系统清零,数码管处于灭零状态;当主持人按下start(KEY[1])按键后,

LED**(LEDG[0])**闪烁一下以其代替05S的声响,抢答芯片处于工作状态。lock为低电平“0”,

与74HC46Bin’端连接,故数码显示处于灭零状态。当有人抢答(先后按下s7-s0,优先者为准,高电平有效)由上述VHDL源程序可知,抢答芯片可以实现输出优先者的编号且使其他选手的按键操作无效。此时输出lock为“1”则74HC46处于工作状态,显示优先抢答者的编号。例如,当按下s0按键后,s_out输出“0001”送到74HC46译码器最后显示为“1”。按其他按键无效。当优先抢答者回答完问题后,由主持人操作清零clear(KEY[0])按键,使抢答电路复位,以便于进行下一轮抢答。

5 结论与问题讨论

5.1完成程度

对设计的要求,除了报警电路和秒数设定方面,基本实现抢答器的设计要求。设计中,扬声器所获电路用发光二极管代替。秒数任意设定方面,我把秒数直接设为30秒。

5.2问题与解决方法

第一天,刚接到QuartusII

软件,对这软件的用途及使用不清楚。经过老师的讲解、同学指教和实例练习,基本了解掌握QuartusII

软件的使用。

知道自己要设计八位抢答器之后,由于对基本的元器件使用不清楚,没有什么设计思路。经过上网,去图书馆找资料,老师提供的资料,复习《模电》和《数电》,重新对元器件掌握。根据资料,完成基本的设计框图。

根据自己的设计方案,分两大模块:抢答显示电路和倒计时显示电路。

抢答显示电路用74HC148、RS锁存器和74HC46译码器实现。而倒计时显示电路用74HC192和74HC46实现在QuartusII

软件画出原理图。进行编译修改,但经过多次修改。加载后还是不行,两个部分都不行。于是进行各个模块分别编译、加载,实现计数功能。但抢答部分还是不行。最后,决定用VHDL编程实现抢答部分的功能。通过请教同学、老师,用VHDL实现抢答部分功能。最后把两大部分进行整合,用时序电路对两大部分进行整合。经过修改,两大整合成功,基本实现抢答的功能。还有的是对于分频器设计,不了解。经老师指导,请教同学使用软件本身可编程器件实现分频功能。

5.3不足及改进

刚设计好的抢答器有以下不足:

不能实现报警功能,即没有定时时间到达后无提示。改进思路:利用74HC192十位借位输出端BON’,工作时BON=1,不工作时及借位溢出时BON’=0,而发光二极管,高电平发光,低电平灭。故采用发光二极管代替扬声器,把BON’端加反相后与LED24发光二极管连接。当定时时间到,即显示“00”状态,二极管发光。

选手抢答后,无声响提示。改进思路:利用lock输出端实现。当有选手抢答时,lock输出“1”,否则输出为“0“。而发光二极管,高电平发光,低电平灭。故采用发光二极管代替扬声器,把LED发光二极管与lock输出端连接。则当选手抢答后,二极管发光提示。

主持人按下begin按键,无0.5秒声响。改进思路:利用begin(KEY[1])按键,其低电平触发,即按下为低电平。故输入begin接反相后与lock输出作为或门的输入。而或门输出连接LED发光二极管。当按一下begin按键,二极管会闪烁一下。这样就实现了主持人按下begin按键,以二极管的闪烁代替0.5秒的声响。

存在缺陷:由计数器清零时,借位端BON’=0,这使得LED24发光。

当按下clear按键后,LED24即报警电路会发光。抢答器工作时,两发光二极管都灭,但定时时间到达后LED24发光。只能利用时序电路使得按下clear按键后,二极管闪烁一下,不能使它灭掉。

5.3收获及心得体会

通过这次数字电子课程设计,我了解到EDA技术、数字可编程器件在电子应用方面的重要性。

了解到数字电子技术在一些基础性应用的方便性和重要性。掌握到数字电子设计开发软件如QuartusII

软件,了解到数字电子技术设计一般采用电路原理图方法设计,分为以下几个步骤:

(1).分析任务要求,总体方案设计

1)单元电路的细节设计

(2).单元电路设计

- 在单元电路中控制电路的设计尤为重要,含控制电路才能称为一个系统。

(3).在前面的基础上,完成总系统的电路原理图。

(4).使用可编程逻辑器件的QuartusII

软件,用图形输入方法,通过编译、仿真和综合地,结合学习机设置各输入、输出端重新综合,并下载到相应芯片中。最后在学习机上验证结果。

(5).在验证结果正确以后,确定最终方案并绘制电路图》

(6).写出总结报告,进一步完善设计文档资料,如设计报告、使用说明书等式。

体会到“冰冻三尺非一日之寒,滴水石穿非一日之功”。要想掌握一门设计方法必需多做多练!通过课程设计掌握工程的基本设计方法,提高动手能力;加深对自己专业的了解和认识。深化专业知识,为以从事相关工作打下基础。

参考文献

**《现代电子技术实践课程指导》**谢云 等 主编,机械工业出版社

**《SOPC技术与应用》**江国强,机械工业出版社,2006年10月

**《EDA技术与应用》**江国强,电子工业出版社,2007年1月

《FPGA与SOPC设计教程: DE2实践》

张志刚编著. - 西安: 西安电子科技大学出版社, 2007.334页+光盘1片

5195

5195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?