第八章控制单元

一、控制单元功能

1.1微操作命令分析

-

控制单元具有发出各种微操作命令(即控制信号)序列的功能。

-

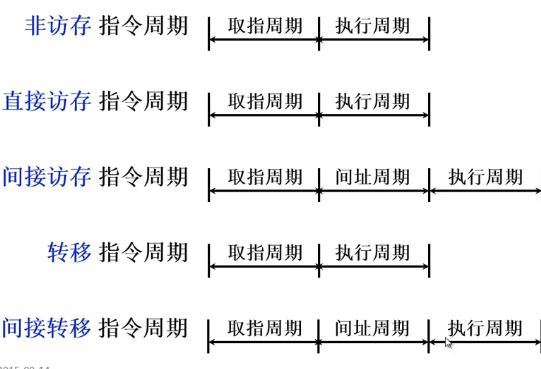

控制单元在完成一条指令需要发送各种控制信号(即微操作命令),完成一条指令分为4个工作周期:取指周期、间址周期、执行周期、中断周期

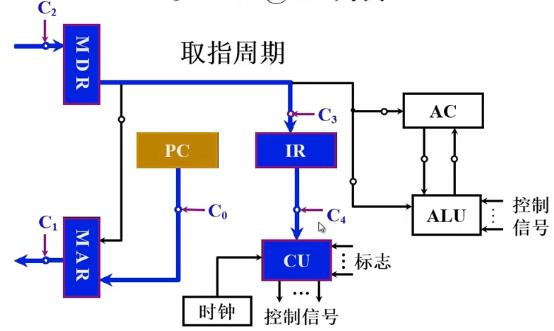

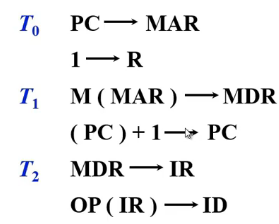

1.取指周期操作

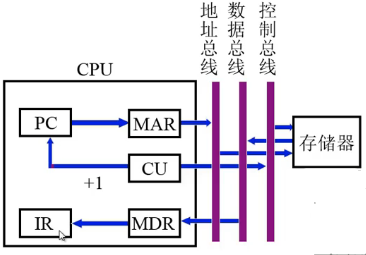

①现行指令地址送到地址寄存器,记作PC→MAR

②CU向主存发送读命令,启动主存读操作,记作1→R

③将MAR所指的主存单元中的内容经过数据总线送至MDR,记作M(MAR)→MDR

④将MDR的内容送至IR,记作MDR→IR

⑤指令操作码送至CU译码,记作OP(IR)→CU

⑥形成下一条指令的地址,记作(PC)+1→PC

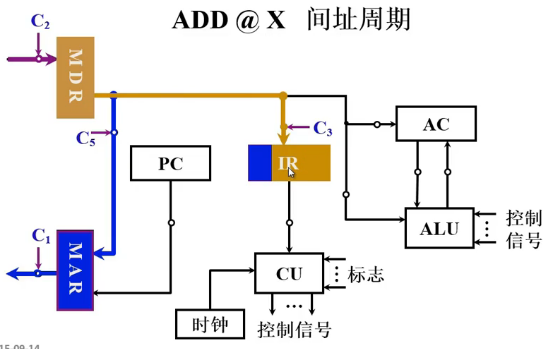

2.间址周期操作

①将指令地址码部分(形式地址)送至地址寄存器,记作Ad(IR)→MAR

②向主存发出读命令,记作1→R

③将MAR所指的主存单元内容经过数据总线送到MDR,记作M(MAR)→MDR

④将有效地址送到指令寄存器的字段,记作MDR→Ad(IR)

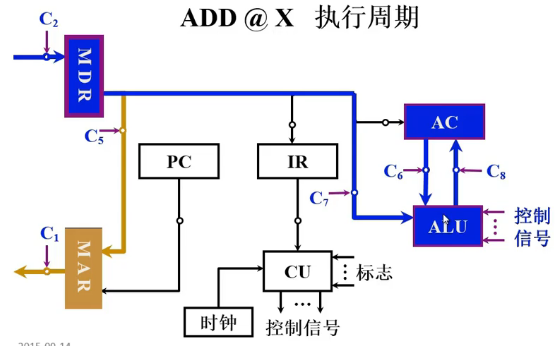

3.执行周期

(1)非访存指令

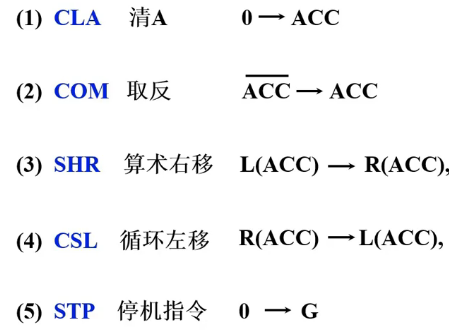

- CLA:表示清除累加器ACC操作

- COM:表示累加器内容取反

- SHR:表示算术右移,符号位不变

- CSL:表示循环左移,也就是内容左移,且左移的第一位放到最后。

- STP:表示将运行标志触发器置“0”。计算机中有一个运行标志触发器G,G=1时表示机器运行,G=0时表示停机。

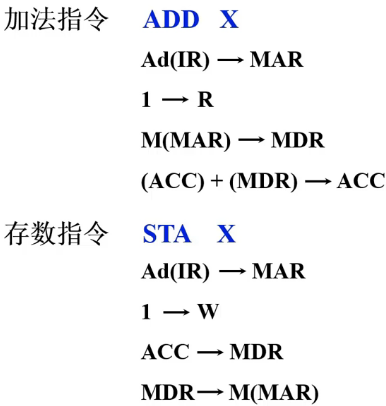

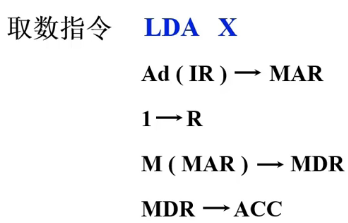

(2)访存指令

(3)转移指令

①无条件转移指令:JMP X

- 该阶段完成将指令地址码部分X送入PC操作,记作Ad(X)→PC

②条件转移:例如,BAN X(负则转)

- 改指令根据上一条指令运行结果,如果是负数则指令地址码送入PC,否则继续执行原指令。

(4)三类指令的指令周期

4.中断周期

- 中断周期中保存断点有两种方式:保存断点存入"0"地址、程序断点进栈

- 以保存断点存入"0"地址为例:

①将特定地址“0”送入地址寄存器,记作0→MAR

②向主存发出写命令,记作1→W

③将PC内容(程序断点)送至MDR,记作PC→MDR

④将MDR的内容(程序断点)通过数据总线写入MAR所指的主存单元,记作MDR→M(MAR)

⑤将向量地址形成部件输出送至PC,记作向量地址→PC

⑥关中断,允许中断触发器为EINT,记作0→EINT

- 以程序断点进栈为例:

只需要将①改为(SP) - 1→ SP→MAR。

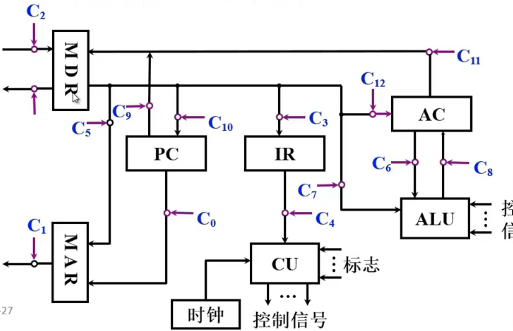

1.2控制单元(CU)功能

1.输入信号

(1)时钟信号

- 为了使控制单元按一定先后顺序、一定节奏发出各种控制信号,CU受时钟信号控制。

- 一个时钟脉冲使控制单元发送一个操作命令或者一组同时执行的操作命令。

(2)指令寄存器

- 当指令寄存器保存了要执行的指令,指令的操作码部分必须送入CU,由CU进行译码指出要做的操作。OP(IR)→CU

(3)标志

- 控制单元受CPU当前所处状态产生信号的标志控制。

(4)外来信号

- 如INTR的中断请求,HRQ的总线请求,以及DMA请求。

2.输出信号

(1)CPU内各种控制信号

- 主要用于CPU内寄存器之间传输,以及控制ALU实现不同操作。

(2)送至系统总线(控制总线)的信号

- 例如,访存控制信号、访I/O存储器的控制信号、读命令、写命令、中断响应信号、总线的应答信号

1.3控制信号

1.不采用CPU内部总线方式

以ADD @X为例,也就是加法指令,这条指令采用间接寻址方式,@是间接寻址的标志

(1)取指周期

①控制信号C0有效,打开PC送往MAR的控制门。

②控制信号C1有效,打开MAR送往地址总线的输出门。

③通过控制总线向主存发出读命令

④C2有效,打开数据总线送至MDR的输入门。

⑤C3有效,打开MDR和IR之间的控制门,将指令送至IR。

⑥C4有效,打开指令操作码送至CU的输出门,CU在时钟和操作码的控制下产生各种控制信号。

(2)间址周期

①MDR通过C5控制门将指令形式地址送入MAR

②MAR通过C1送到存储器中地址信号

③CU通过控制总线向主存发出读指令

④通过C2把内存单元中读出的数据通过数据总线传入MDR。

⑤将MDR保存的地址通过C3放出IR地址码字段。

(3)执行周期

①通过C5,将MDR中有效地址送至MAR,MAR通过C1送至存储器中地址信号。

②CU通过控制向主存发出读命令,并通过C2送入MDR。

③通过C6和C7,以及内部控制总线发出的控制信号,在ALU进行内容相加

④将相加完成的内容通过C8存储AC。

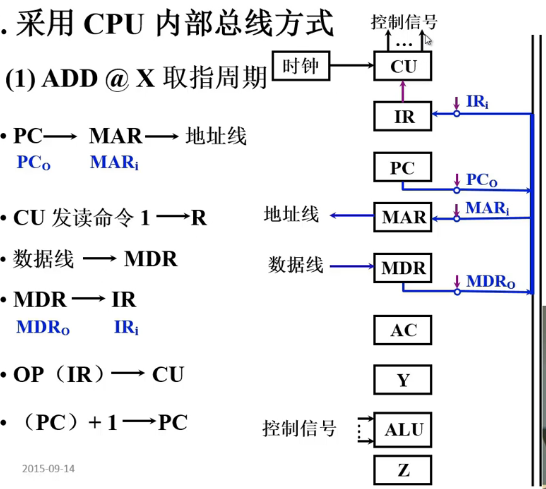

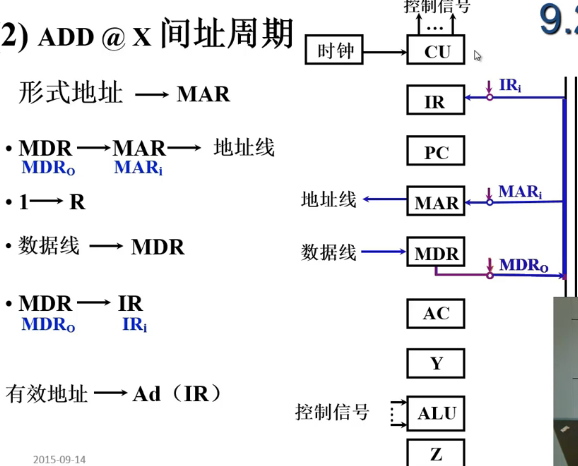

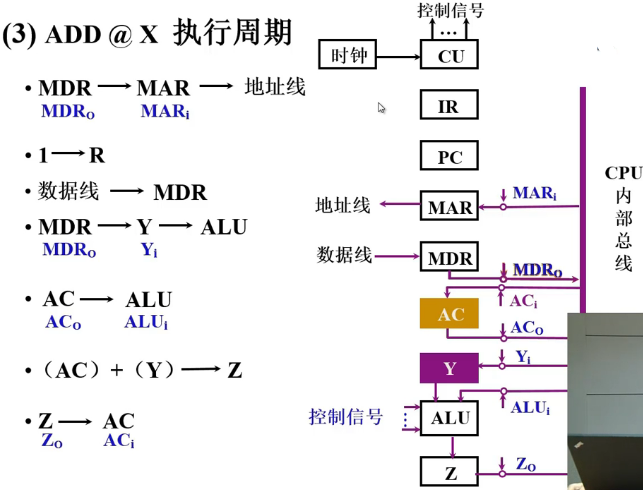

2.采用CPU内部总线方式

以ADD @X为例,也就是加法指令,这条指令采用间接寻址方式,@是间接寻址的标志

(1)取指周期

(2)间址周期

(3)执行周期

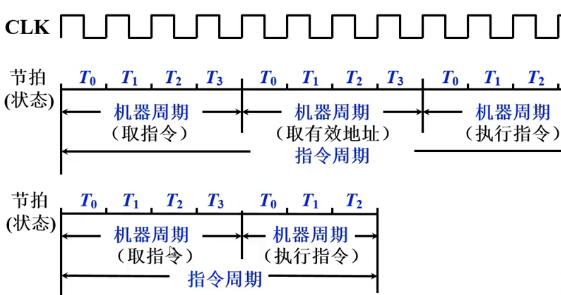

1.4多级时序系统

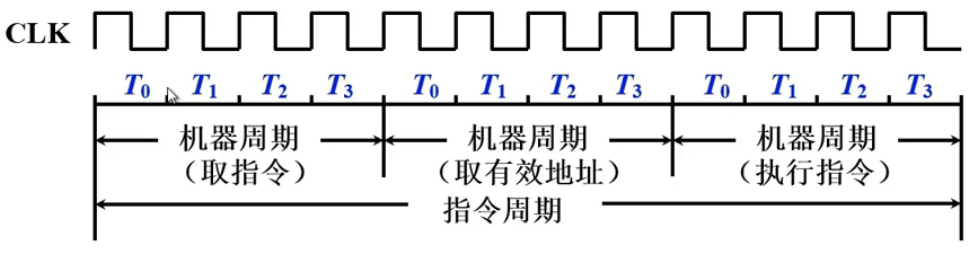

1.机器周期

- 机器周期:所有指令执行过程的有一个基准时间。也就是每个指令执行每个步骤所需的时间

- 基准时间:以完成最复杂指令功能的时间作为基准。以访问一次存储器的时间为基准。

- 若指令字长=存储字长,则取指周期=机器周期。

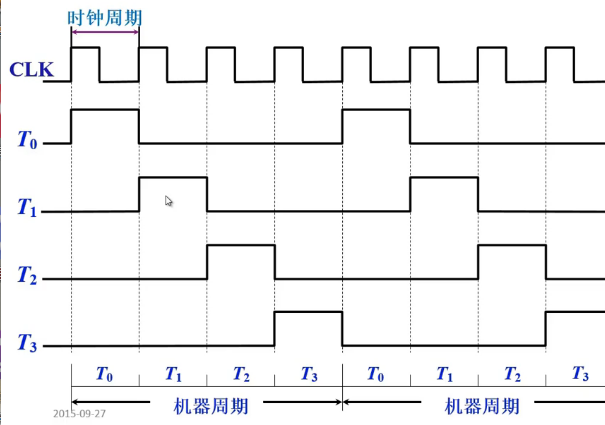

2.时钟周期

-

时钟周期:每个微操作需要的一定时间,一个机器周期内可以完成若干个时钟周期。是控制计算机操作的最小单位时间。

-

用时钟周期控制产生一个或几个微操作指令

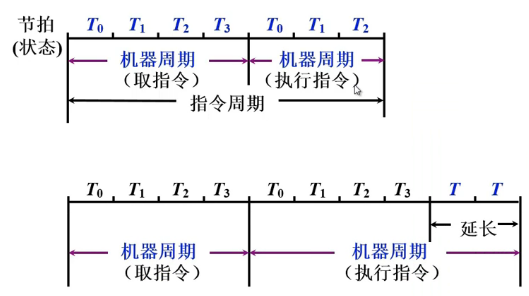

3.多级时序系统

- 机器周期、节拍组成多级时序系统。

- 一个指令周期包含若干个机器周期,一个机器周期包含若干个时钟周期。

4.机器速度与机器主频的关系

- 在机器周期所含时钟周期数相同前提下,机器主频越快,机器的速度越快。且平均指令执行速度之比等于两机主频之比。

- 机器速度不仅与主频有关,还与机器周期中所包含时钟周期数以及指令周期所含机器周期数有关。

1.5控制方式

- 产生不同微操作命令序列所用的时序控制方式

(1)同步控制方式

- 同步控制:任意微操作均有统一基准时标的时序信号控制。

①采用定长的机器周期

- 以最长的微操作序列和最复杂的微操作作为标准。机器周期内节拍数相同

②采用不定长的机器周期

- 机器周期内节拍数不等

(2)异步控制方式

- 无基准时标信号,采用应答方式

(3)联合控制方式

- 同步和异步相结合。

二、组合逻辑设计

2.1组合逻辑设计

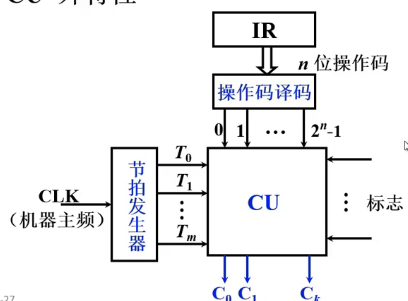

1.CU外特性

①CU要发出各种控制信号之间是有先后关系的,由节拍发生器设定的。节拍发生器由时钟外端接的是时钟,产生多个节拍信号。

②IR当中指令操作码经过操作码译码后,移码结果对应了CU要做什么操作。

③CU的输入也包括了一系列标志。

④在①②③的输入下,在给定时钟周期CU就会给定控制信号。

【节拍信号示意图】

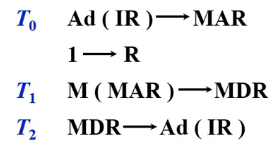

2.微操作的节拍安排

【假设】机器采用同步控制,每个机器周期包含3个节拍,且CPU内部采用非总线方式。

(1)取指周期微操作的节拍安排

(2)间址周期微操作的节拍安排

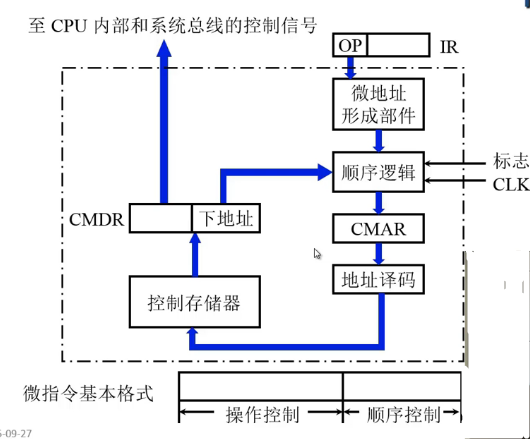

2.2微程序设计

- 微程序设计:一条机器指令对应了一个微程序,一个微程序包含多个微指令,一个微指令包含了多个微操作命令。

- 按照存储逻辑,把逻辑信号存储在存储器当中。

【微程序控制单元基本框图】

且CPU内部采用非总线方式。

[外链图片转存中…(img-QCEANrZt-1693816292168)]

(1)取指周期微操作的节拍安排

[外链图片转存中…(img-VWGplX5H-1693816292168)]

(2)间址周期微操作的节拍安排

[外链图片转存中…(img-IcnQ4hZ7-1693816292168)]

2.2微程序设计

- 微程序设计:一条机器指令对应了一个微程序,一个微程序包含多个微指令,一个微指令包含了多个微操作命令。

- 按照存储逻辑,把逻辑信号存储在存储器当中。

【微程序控制单元基本框图】

计算机组成原理——刘宏伟

参考文献:计算机组成原理第2版—唐朔飞

本文详细阐述了控制单元的功能,包括微操作命令分析、不同周期操作(取指、间址、执行、中断)及其控制信号,以及同步和异步控制方式的应用。此外,还涉及组合逻辑设计和微程序设计,展示了机器周期与时钟周期的关系以及具体操作的节拍安排。

本文详细阐述了控制单元的功能,包括微操作命令分析、不同周期操作(取指、间址、执行、中断)及其控制信号,以及同步和异步控制方式的应用。此外,还涉及组合逻辑设计和微程序设计,展示了机器周期与时钟周期的关系以及具体操作的节拍安排。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?