注意及引用

由于本人学习FPGA尚处于初级阶段,大部分资料学习来源于 Xilinx暑期学校以及《Xilinx FPGA原理与实践》,故部分内容引用于以上两处,且一般以目前流行的 Xilinx 7 系列 FPGA 进行分析,由于个人能力问题,思考难免出现问题,恳请各位大佬进行批评指正。

FPGA整体概述

FPGA,Field-Programmable Gate Array,学术解释为现场可编程门阵列,用人话来说就是由多个 可以编程 且 互连连接的可配置逻辑块 (CLB),组成矩阵,构成的一个整体的半导体器件。

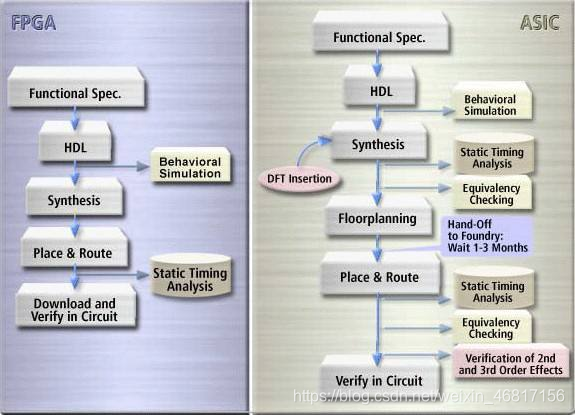

FPGA, 其实是很多代可编程器件升级迭代的集成化产物,他经历了PAL(70年代,一次性的可编程阵列逻辑)、GAL(通用阵列逻辑)、CPLD(复杂可编程阵列逻辑)。他改变了专用集成电路(ASIC)中大部分算法“冻结”无法更改的缺陷,一旦设计制造完成后电路就固定的问题在FPGA中得以解决,并且也克服了可编程器件门电路数量有限的缺点。但不可否认的是,ASIC由于其特定性,成本低体积小是它的一个优势。

总结:FPGA是制程工艺上年的逻辑实现虚拟化层,允许芯片流片后再决定电路

FPGA相关术语

可编程(Programmable)

开发者视角,可以对FPGA进行编程

可重构(Reconfigurable)

针对器件特性的描述,器件上的电路可以被重构

可定制(Customizable)

针对应用/客户,可以为其定制硬件

软件定义(Software)

可用软件设计方式重新定义硬件功能

FPGA基本逻辑结构

FPGA因为其采用逻辑单元阵列,故分为 可配置逻辑模块(CLB)、输入输出模块(IOB)、内部连线(Interconnect)三个部分。

整体来讲,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器(具有记忆功能的,两个稳定状态“0”和“1”)的输入端,模块之间通过连线互相连接,通过触发器再去驱动其他逻辑电路。

可配置逻辑单元(CLB)

CLB是FPGA体系结构的核心。在CLB中一般情况下包含很多个Slice。Slice是一个包括查找表、进位链和寄存器的组合模块。

Slice又分为SliceM和SliceL,配合使用使芯片在保证能力和性能的同时,实现低成本和低功耗。

SliceM:能够实现补码运算、移位寄存器、储存器功能

SliceL:只能实现逻辑函数的查找表

1.查找表

基于7系列的FPGA,每个查找表LUT都有1个6输入和2个独立输出。

2.存储元件

每一个Slice具有8个存储元件,可以配置为触发器和锁存器。

3.分布式RAM资源

分布式RAM资源是同步资源,对一个Slice,所有的触发器有统一的时钟输入。

输入输出单元(IOB)

与外界电平兼容的输入输出IO接口,IOB是FPGA对外的接口。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?