数据结构

图的概念

路径

从顶点 v p v_p vp到顶点 v q v_q vq之间的一条路径是指顶点序列 v p v_p vp, v i 1 v_{i1} vi1, v i 2 v_{i2} vi2, v i 3 v_{i3} vi3,…, v q v_q vq。路径上的边的数目称为路径长度。

简单路径

简单路径是一条不经过重复顶点路径。

回路

对顶点序列顶点序列

v

p

v_p

vp,

v

i

1

v_{i1}

vi1,

v

i

2

v_{i2}

vi2,

v

i

3

v_{i3}

vi3,…,

v

q

v_q

vq,若

v

q

v_q

vq与

v

p

v_p

vp间存在路径,即存在顶点序列

v

p

v_p

vp,

v

i

1

v_{i1}

vi1,

v

i

2

v_{i2}

vi2,

v

i

3

v_{i3}

vi3,…,

v

q

v_q

vq,

v

p

v_p

vp,则称这条路径为回路。

即:第一个顶点与最后一个顶点相同的路径称为回路

简单回路

除第一个顶点和最后一个顶点外,其他顶点序列均不重复的回路称为简单回路。即绕一圈,只有起点和终点重合

欧拉路径

通过图上所有边的简单路径

欧拉回路

闭合的欧拉路径,即从顶点 v p v_p vp开始,经过图中所有边回到 v p v_p vp,途中不经过重复顶点

计算机组成原理

IEEE754标准

32位单精度格式

| 符号(1位) | 阶码(8位) | 尾数(23位) |

|---|

64位双精度格式

| 符号(1位) | 阶码(11位) | 尾数(52位) |

|---|

其中阶码移码表示,尾数原码表示

阶码移码的偏置值,对单精度浮点数偏置值为127,对双精度浮点数偏置值为1023。假设阶码为E,该浮点数的阶数为k,则有E = k + 偏置值

尾数部分为纯小数,对规格化的二进制浮点数,数值的最高位总是1,IEEE754标准在尾数最高位隐含了一位1,23位尾数实际上表示了24位有效数字。

【例题】 float型数据用IEEE 754单精度浮点数格式表示。若编译器将float型变量x分配到一个32位浮点寄存器FR1中,且x=-8.25,则FR1的内容是 C104 0000H。

【分析】

x

=

−

8.25

x=-8.25

x=−8.25,即

x

=

−

1000.01

B

=

−

1.00001

B

∗

2

3

x=-1000.01B=-1.00001B*2^3

x=−1000.01B=−1.00001B∗23。

故该浮点数的阶码E = 127 + 3 = 130 = 1000 0010B,尾数部分为00001。

| 符号(1位) | 阶码(8位) | 尾数(23位) |

|---|---|---|

| 1 | 100 0001 0 | 000 0100 0000 0000 0000 0000 |

FR1寄存器的内容即为C104 0000H

IEEE 754浮点数的范围

| 格式 | 最小值 | 最大值 |

|---|---|---|

| 单精度 | E = 1 , M = 0 1.0 ∗ 2 1 − 127 = 2 − 126 E = 1,M = 0\\ 1.0*2^{1-127} = 2^{-126} E=1,M=01.0∗21−127=2−126 | E = 254 , M = . 1111 ⋅ ⋅ ⋅ 1.111 ⋅ ⋅ ⋅ 1 ∗ 2 254 − 127 = 2 127 ∗ ( 2 − 2 − 23 ) = 2 128 − 2 104 E = 254,M = .1111···\\ 1.111···1*2^{254-127} = 2^{127} * (2 - 2^{-23}) = 2^{128}-2^{104} E=254,M=.1111⋅⋅⋅1.111⋅⋅⋅1∗2254−127=2127∗(2−2−23)=2128−2104 |

| 双精度 | E = 1 , M = 0 1.0 ∗ 2 1 − 1023 = 2 − 1022 E = 1,M = 0\\ 1.0*2^{1-1023} = 2^{-1022} E=1,M=01.0∗21−1023=2−1022 | E = 2046 , M = . 1111 ⋅ ⋅ ⋅ 1.111 ⋅ ⋅ ⋅ 1 ∗ 2 2046 − 1023 = 2 1023 ∗ ( 2 − 2 − 52 ) = 2 1024 − 2 971 E = 2046,M = .1111···\\ 1.111···1*2^{2046-1023} = 2^{1023} * (2 - 2^{-52}) = 2^{1024}-2^{971} E=2046,M=.1111⋅⋅⋅1.111⋅⋅⋅1∗22046−1023=21023∗(2−2−52)=21024−2971 |

最大值部分的-23、-52分别为单精度、双精度的尾数部分长度。

中断屏蔽技术——中断屏蔽字

1表示屏蔽该中断请求,0表示可以正常中断。

【例题】 某计算机有五级中断

L

4

L_4

L4~

L

0

L_0

L0,中断屏蔽字为

M

4

M

3

M

2

M

1

M

0

M_4M_3M_2M_1M_0

M4M3M2M1M0。中断响应优先级从高到低的顺序是

L

4

→

L

0

→

L

2

→

L

1

→

L

3

L_4→L_0→L_2→L_1→L_3

L4→L0→L2→L1→L3,则

L

1

L_1

L1的中断处理程序中设置的中断屏蔽字是01010

【分析】 首先,每一级中断均屏蔽同级中断,同位置1,后续只需将优先级更低的置1即可。

L

1

L_1

L1屏蔽的中断为

L

1

L_1

L1、

L

3

L_3

L3,故该中断屏蔽字为01010

中断屏蔽字只与响应优先级有关

操作系统

操作系统的I/O层次结构

| 用户层I/O软件 |

|---|

| 设备独立性软件 |

| 设备驱动程序 |

| 中断处理程序 |

| 硬件 |

故用户程序发出磁盘I/O请求后,系统的正确处理流程为用户程序→系统调用处理程序→设备驱动程序→中断处理程序。

设备驱动程序更靠用户I/O层,比中断处理先

抖动

在页面置换的过程中,频繁发生刚刚换出的页面马上又要换入主存或刚刚换入的页面马上又要换出主存的现象,则称这种频繁出现缺页中断的页面调度行为称为抖动

故撤销部分进程可以减少所要用到的页面数,防止抖动。

频繁出现缺页中断还有一个原因是分配给进程的物理块不够,故给该进程分配更多物理块也可以减少抖动现象。

具有对换功能的操作系统,通常会把外存分为文件区和对换区。对换区用于存放从内存换出的进程。故对换区的大小与抖动的发生没有关系。

计算机网络

波特率B与数据传输率C与带宽W

由奈奎斯特定理,

理

想

低

通

信

道

下

的

极

限

数

据

传

输

速

率

C

=

2

W

l

o

g

2

V

(

单

位

b

/

s

)

理想低通信道下的极限数据传输速率C=2Wlog_2V(单位b/s)

理想低通信道下的极限数据传输速率C=2Wlog2V(单位b/s)。其中B = 2W。

主机进行WEB请求综合

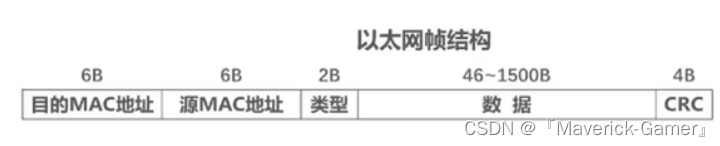

数据的封装(网络层-数据链路层)

主机进行Web请求时,数据向下封装。IP数据报位于以太网帧的数据部分。

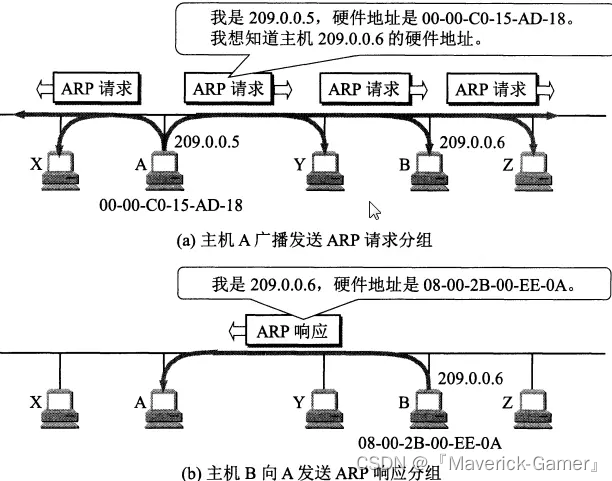

其中,在主机的以太网帧中,源MAC地址是主机的MAC地址。路由器是主机的默认网关,目的MAC地址是路由器R的MAC地址。在网络请求时,主机知道路由器的IP地址但不知道路由器的MAC地址,此时需要通过地址解析协议(ARP协议,实现IP地址到MAC地址的映射,工作于网络层) 来获取MAC地址。

首先主机先在ARP高速缓存中查看有无主机B的IP地址,若有即可直接查询到主机B的MAC地址。若无,则主机A通过使用目的MAC地址为FF-FF-FF-FF-FF-FF的帧来封装并广播ARP请求分组使得同一个局域网的所有主机都接受到此ARP请求。但主机B是单独向主机A发送ARP响应分组,其包含了主机B的IP于MAC的映射关系。

在以太网帧数据部分IP分组头中,源IP地址是主机的IP地址。由于是主机进行Web请求,目的IP地址为Web服务器的IP地址。

在请求传输的过程中,有些数据应当修改。由于中间的点将数据逐级解包,数据链路层和物理层需重新封装,故以太网帧的目的MAC地址、源MAC地址、CRC均需要修改。且源MAC地址为当前点(路由器),目的MAC地址为下一跳的MAC地址。

在IP数据报中,需要修改的内容为源IP地址、生存时间以及首部检验和。源IP地址修改为当前点(路由器) 的IP地址。

注:仅实现了NAT的路由器会对IP地址进行修改,目的网络处的NAT路由器会修改目的IP地址。

应用层协议----HTTP协议

HTTP协议的工作方式

非持久连接

每个网络元素对象都需要单独建立TCP连接

持久连接

万维网服务器在发送响应后仍保持这条链接,可以继续在连接上传输后续的请求和响应报文。持久连接又分为非流水线和流水线两种方式。

非流水线方式:收到前一个响应后才能发出下一个请求。此时每个引用都必须有一个RTT延迟。

流水线方式:每遇到一个对象引用就立即发送请求。此时所有应用对象共计经历一个RTT延迟。

9533

9533

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?