1.理解时序逻辑电路与组合逻辑电路的区别

时序逻辑的核心元件是触发器,边沿触发器仅在始终跳变是读取新值,其他时间保存该值,利用这个属性,与加法器结合可以组成计数器,即一个时钟周期,计数值加一,其他情况保存该计数值。

2.同步清零和异步清零

同步清零和异步清零,同步清零的always@()中的敏感事件表仅有clock信号无rst信号,异步清零的敏感事件表中有rst信号。

3.如何确定目标计数值(!!有误区)

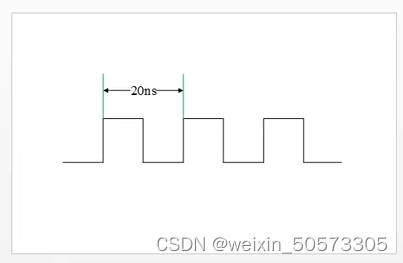

如设置小灯闪烁时间为500ms(亮500ms,灭500ms),即周期为1s(但是周期无所谓,只看他需要多长时间翻转一次即可),而晶振频率为50MHz,时间为20ns,说明时钟周期为20ns,(如果占空比为50%,则clock信号每10ns翻转一次),目标每500ms翻转一次(即500ms来一次触发翻转的信号),则目标计数值为500ms/20ns=25000000。

!!重大误区在于纠结小灯的周期和时钟周期,计算目标计数值时直接使用小灯周期除以时钟周期,这样是不对的,事实上只需要得到小灯周期的一半即可,因为小灯的周期是由亮的一半时间加上灭的一半时间得到的。

4.代码

module led_twinkle(

input wire clock;

input wire rst_n;

output reg led;

);

reg [25:0] counter;

always@(posedge clock or negedge rst_n) begin

if(!rst_n)

counter <= 0;

else if(counter == 25000_000-1)

counter <= 0;

else

counter <= counter+1;

end

always@(posedge clock or negedge rst_n) begin

if(!rst_n)

led <= 1'b0;

else if(counter == 25000_000-1)

led <= !led;

else //可以不写全,即省略else,因为本身就是时序逻辑,本身就是要生成锁存器的。

led <= led;

end

endmodule

5.流水灯实现

重点学习循环左移与循环右移以及拼接符的用法

实现流水灯可以使用三种基本方法:reg [7:0] Led;

(1):每计数500ms,Led <= Led<<1;

当Led==8'b1000_0000 || 8‘b0000_0000;Led <= 8'b0000_0001;

(2):每计数500ms,Led[7:0] <= {Led[6:0],Led[7]};//此为循环左移的写法!!!

(3):reg [3:0] cnt2,,每计数500ms,cnt2+1,然后通过调用基本的组合逻辑电路3-8译码器来实现流水灯。代码略

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?