一、晶闸管(可控硅)两端为什么并联电阻和电容在实际晶闸管(可控硅)电路中,常在其两端并联RC串联网络,该网络常称为RC阻容吸收电路。

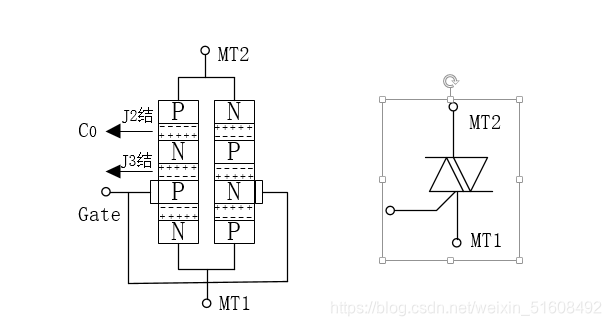

我们知道,晶闸管(可控硅)有一个重要特性参数-断态电压临界上升率(Critical Rate of Rise of Off-State Voltage),即:dlv/dlt。它表明晶闸管(可控硅)在额定结温和门极断路条件下,使晶闸管(可控硅)从断态转入通态的最低电压上升率。若电压上升率过大,超过了晶闸管(可控硅)的电压上升率的值,则会在无门极信号的情况下开通。即使此时加于晶闸管(可控硅)的正向电压低于其阳极峰值电压,也可能发生这种情况。因为晶闸管(可控硅)可以看作是由三个PN结组成,如下图图1所示。

图1

在晶闸管(可控硅)处于阻断状态下,因各层相距很近,其J2结结面相当于一个电容C0。当晶闸管(可控硅)阳极电压变化时,便会有充电电流流过电容C0,并通过J3结,这个电流起了门极触发电流作用。因为I=CdV/dt,如果晶闸管(可控硅)在处于关断的状态时&

本文介绍了晶闸管(可控硅)两端并联RC串联网络的必要性,以限制电压上升率,防止硬开通和保护晶闸管。在选择阻容吸收元件时,电容C通常根据直流电流值来计算,电阻R则根据功率需求选取。阻容吸收回路的时间常数一般为1~10毫秒,不同功率负载对应不同电阻和电容规格。此外,文中还提到了可控硅的关键参数。

本文介绍了晶闸管(可控硅)两端并联RC串联网络的必要性,以限制电压上升率,防止硬开通和保护晶闸管。在选择阻容吸收元件时,电容C通常根据直流电流值来计算,电阻R则根据功率需求选取。阻容吸收回路的时间常数一般为1~10毫秒,不同功率负载对应不同电阻和电容规格。此外,文中还提到了可控硅的关键参数。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5594

5594

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?