指令说明

MIPS32指令集架构中定义的移动操作指令共有6条: movn、movz、mfhi、mthi、mflo、mtlo,后4条指令涉及对特殊寄存器HI、LO的读/写操作。HI、LO寄存器用于保存乘法、除法结果。当用于保存乘法结果时,HI寄存器保存结果的高32位,LO寄存器保存结果的低32位; 当用于保存除法结果时,H寄存器保存余数,LO寄存器保存商。

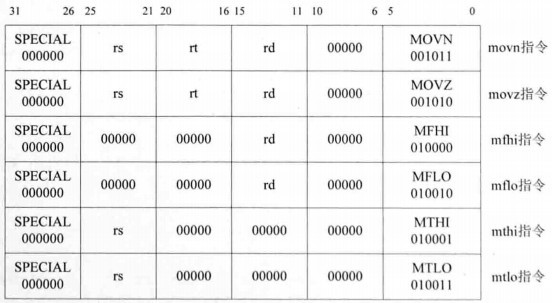

指令格式

movn指令

用法:movn rd, rs,rt

作用: if rt ≠0 then rd <- rs

判断地址为rt的通用寄存器的值。如果不为零,那么将地址为rs 的通用寄存器的值赋给地址为rd的通用寄存器;反之,保持地址为rd的通用寄存器不变

movz指令

用法:movz rd, rs, rt

作用: if rt = 0 then rd <- rs

与上面movn指令的作用正好相反,判断地址为rt的通用寄存器的值。如果为零,那么将地址为rs 的通用寄存器的值赋给地址为rd的通用寄存器;反之,保持地址为rd的通用寄存器不变

mfhi 指令

用法:mfhi rd

作用: rd <- hi

将特殊寄存器Hi的值赋给地址为rd的通用寄存器

mflo指令

用法:mflo rd

作用:rd <- lo

将特殊寄存器LO的值赋给地址为rd的通用寄存器

mthi 指令

用法:mthi rs

作用: hi<- rs

将地址为rs的通用寄存器的值赋给特殊寄存器HI

mtlo指令

用法:mtlo rs

作用:lo <- rs

将地址为rs的通用寄存器的值赋给特殊寄存器LO

代码的修改

- 增加HILO模块,用于实现HI、LO寄存器

- 执行阶段的EX模块增加判断是否要写入HILO模块

- 执行阶段的EX模块增加了与HILO有关的输入接口,解决数据相关问题

HI LO模块

读取HI、LO寄存器时仍会存在数据相关问题,解决方式仍是使用数据前推(上篇讲解过),将处于访存阶段、回写阶段的指令对HI、LO寄存器的操作信息反馈到执行阶段,执行阶段依据这些信息,确定HI、LO寄存器的正确值。

总结

我们在本章学到了移动操作指令的实现以及又处理了流水线数据相关。内容很好理解,后面的指令学起来也是大概也这样的,但也会越来越难的,我们继续加油!

2039

2039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?