一、综述

常见的低功耗技术

常见的技术可以总结为7种,其中前4种需要设计者重点关注,后面三种其实都集成到工具里了,不专门做这方面研究的知道原理即可。

(1)power gating, 关电压。手动设计,需要重点关注。

(2)多点源域设计。手动设计,需要重点关注。

(3)Frequency and Voltage scaling design。手动设计,需要重点关注。

(4)应用层面优化。手动设计。玄学。可以关注。

(5)Clock gating。知道原理即可,工具自动优化。

(6)逻辑门动态功耗优化。知道原理即可,工具自动优化。

(7)晶体管阈值优化。知道原理即可,工具链自动优化。

1、Power Gating

比较简单粗暴,关掉某一块不用的电源。这样动态功耗和静态功耗都被干掉了。这部分东西比较主流。

2、多电源域设计

设计多个电源域。不同的电源域用不同的电压。比如速度慢的用低电压,速度快的用高电压。细节可以看这个桔里猫:如何设计低功耗SOC(三,多电源域)。

3、Frequency and Voltage scaling design

通过降电压和频率来节省能量。这一条也比较关键。各种ISSCC文章水指标的秘籍。发文章和时机使用都非常有效。楼主曾经用65nm工艺下流片的测试结果发现只要频率足够低,供电电压能降到0.5-0.6之间。节省的功耗还是巨大的。细节看这个。

4、从应用层面降低功耗

顾名思义,从应用层面优化功耗。比如笔者在某一年国际会议上遇到一个MIT的小姐姐,她们做了一个神奇的工作,主要研究如何训练神经网络模型,让计算的时候翻转率变小从而节省功耗。不过这种东西可能更适合小公司,因为对于大公司来讲芯片做出来怎么用对于芯片设计者来讲基本上是不归你管的。不让你做防呆设计就不错了你还指望人家听你的给你搞这个。

上面方法是架构和前端需要重点关注的技术,后面这些前端已经要碰不到了。

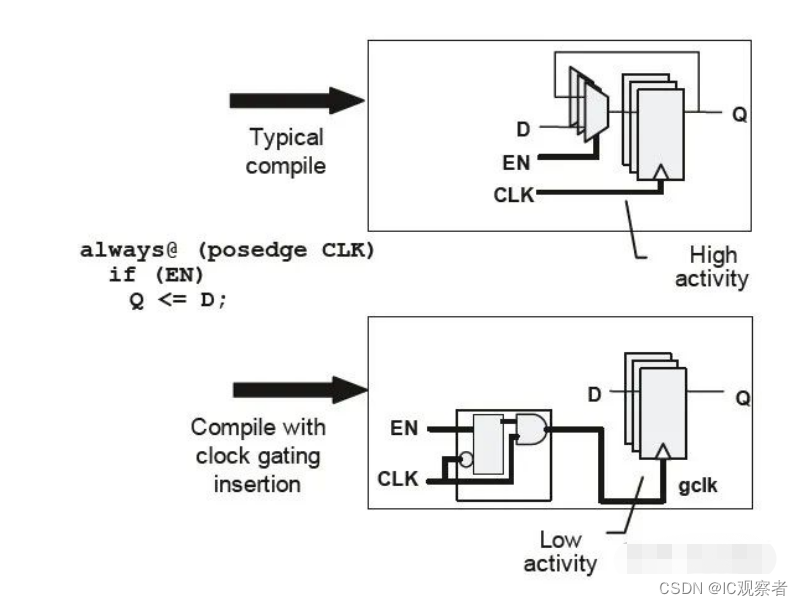

5、Clock Gating

直接把时钟停了,这样可以干掉动态功耗。实际上在数字芯片里时钟网络本来就占用了很大功耗,有可能超过50%。其原理是这样的。

比如有个EN信号,这个EN信号有效寄存器值才变,那不如直接用这个en把时钟屏蔽了。寄存器多的时候节省还是挺明显的。但需要注意的是,clock gating虽然是很直接的办法,但是一般来说你不要头铁自己去RTL层面写这个clock gating, 工具都会给你优化好。你自己头铁写个clock gating上去非常有可能产生个毛刺啥的影响正确性。

6、逻辑门动态功耗优化

综合工具除了能帮你搞clock gating, 还能帮你搞逻辑

本文深入探讨了数字IC设计中的低功耗技术,重点介绍了Power Gating、多电源域设计、频率和电压调整等关键方法。通过降低电压和频率可以显著节省能量,但同时也需要考虑恢复开销和设计复杂性。此外,文章还提到了动态电压和频率调整(DVFS)在实际应用中的挑战和优势。

本文深入探讨了数字IC设计中的低功耗技术,重点介绍了Power Gating、多电源域设计、频率和电压调整等关键方法。通过降低电压和频率可以显著节省能量,但同时也需要考虑恢复开销和设计复杂性。此外,文章还提到了动态电压和频率调整(DVFS)在实际应用中的挑战和优势。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?