在前面进行了riscv架构的初步了解以及汇编指令的初步学习之后,接下来可以在具体的一个riscv架构芯片上进行实践。

目前选用了沁恒微电子的青稞V4系列微处理器来进行实践学习。其采用了标准的RISC-V指令集架构,一个32位通用的MCU微处理器。具体选用型号CH32V307的MCU来进行本次专题的实践。

一、青稞V4F简介

青稞V4F内核支持如下指令集扩展:

- RV32:32位架构,通用寄存器位宽为32bit;

- I指令模块:支持整形操作,具有32个整形寄存器(通用寄存器);

- M指令模块:支持整形乘法和除法指令;

- A指令模块:支持原子指令;

- C指令模块:支持16位压缩指令;

- F指令模块:支持单精度浮点操作,具有32个浮点寄存器(用于浮点运算);

- XW指令模块:自扩展字节和半字操作的16位压缩指令。

同时青稞V4F只支持riscv架构中的两种特权模式:

- 机器模式,该模式具备最高权限,可以访问所有的CSR以及除物理内存保护单元锁定之外的所有物理内存;同时mcu上电时默认处于机器模式下,并且当执行mret指令后,根据CSR的mstatus寄存器中MPP位,来确定返回到哪个特权模式下。

- 用户模式,该模式仅具备最低权限,只能访问特定的CSR寄存器和物理内存保护单元运行的物理地址区域;当发生中断或异常时,mcu将进入机器模式。

二、青稞V4F的CSR寄存器简介

青稞V4F具备一部分riscv标准的csr寄存器,以及厂商自定义的csr寄存器。其csr寄存器列表如下图所示:

下面对部分csr寄存器进行简要的说明:

2.1 marchid:

架构id寄存器,此寄存器为只读寄存器,描述了青稞V4F内核的厂商、架构名称以及版本等信息;

2.2 mstatus:

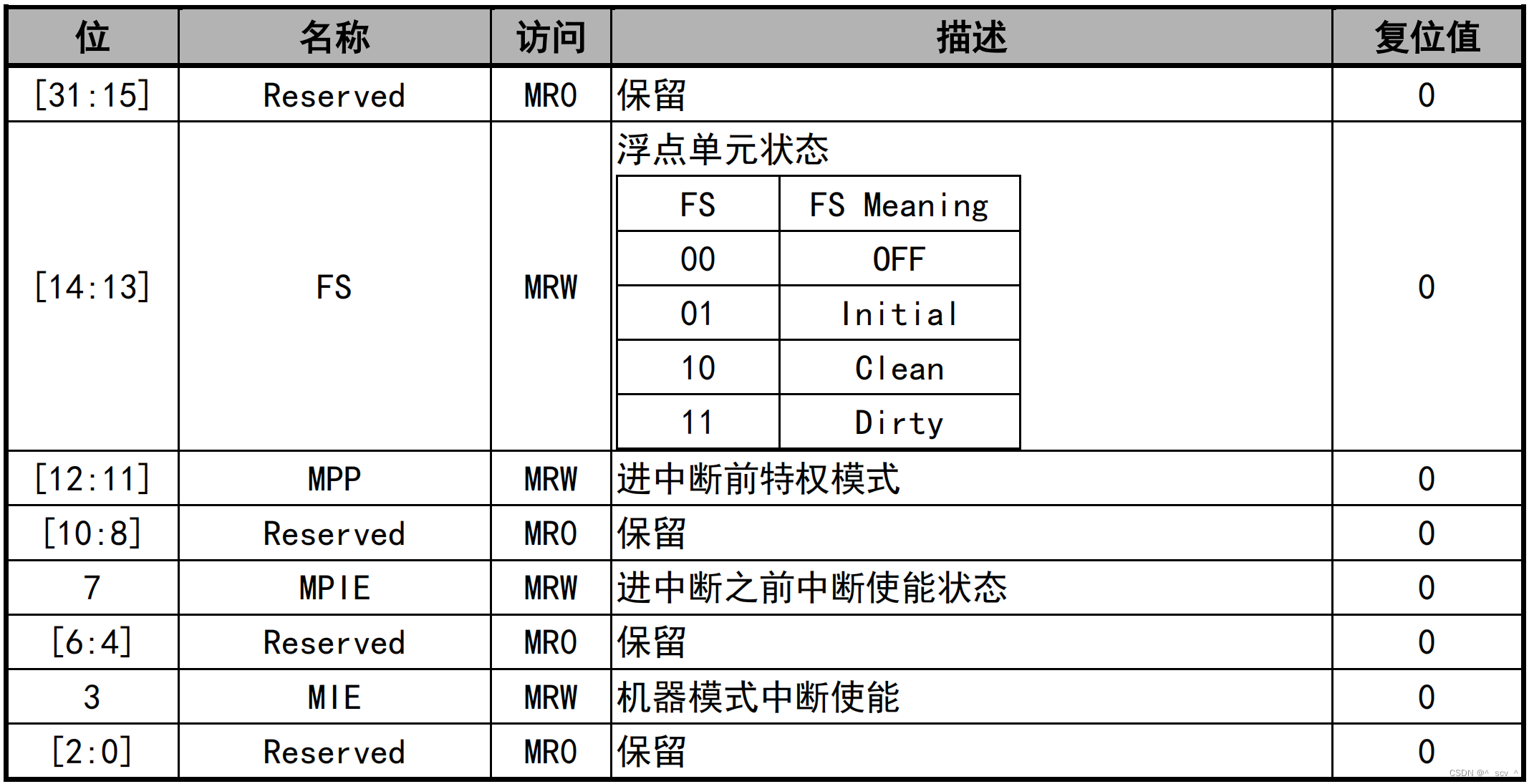

机器状态寄存器,此寄存器存为可读可写寄存器,青稞V4F内核厂商根据标准的riscv架构来进行设计的此寄存器,但是对比标准的mstatus寄存器,青稞V4F内核也仅实现了此寄存器的部分域,如下图所示:

此寄存器的FS域用于开启关闭硬件浮点运算功能,如此域为0x00,并且此时使用浮点指令,那么将出现指令异常;

MPP域为保存进入异常或中断前的特权模式,用于退出异常或中断后的特权模式恢复;例如在用户模式时,发生了异常或中断,此时MPP域的值将被更新为0;然后当异常或中断返回后,MCU将进入MPP域保存的模式;

MIE域为全局中断使能位,当进入异常或中断时,MPIE的值被更新为MIE值;当异常或中断返回时,MIE的值将恢复成MPIE的值。

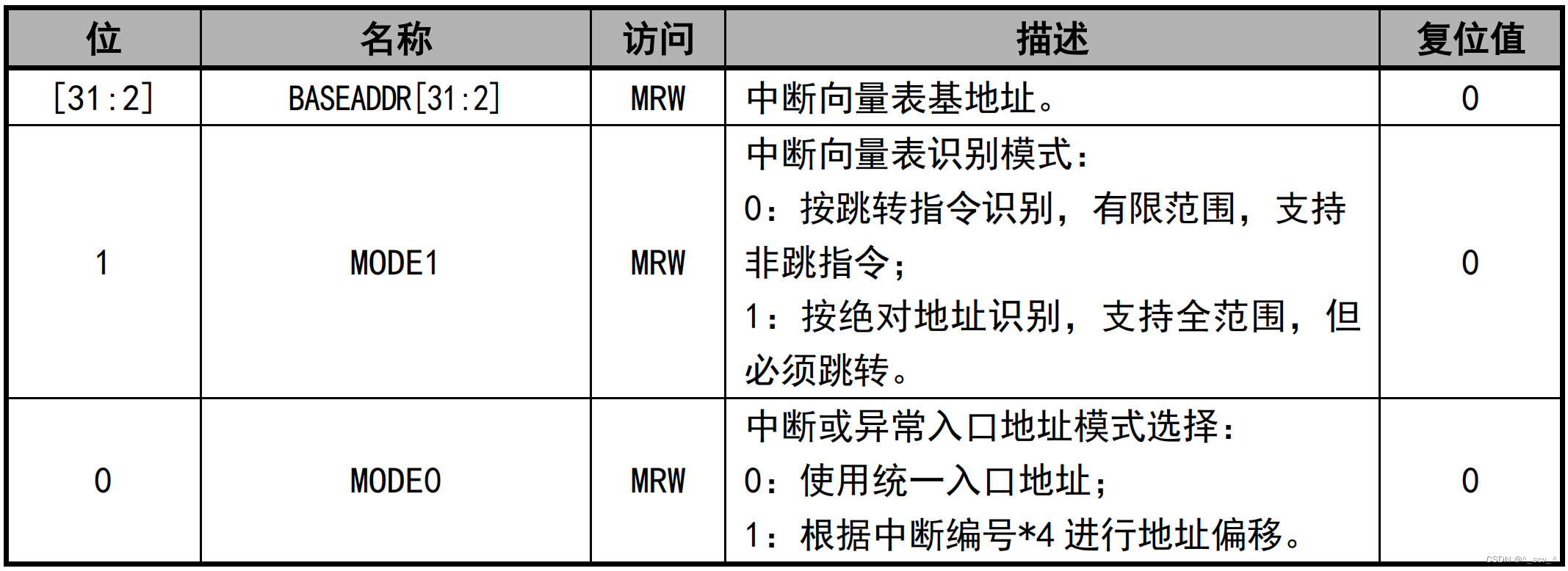

2.3 mtvec

该寄存器器用于存储异常或中断处理程序的基地址,并且低两位用于配置向量表的模式和识别方式。

bit0为选择中断或异常的入口模式,决定是采用统一入口地址,然后读取中断原因寄存器来执行相应中断处理函数分支的方式;还是采用独立入口编址,每个中断源被触发后,都会执行唯一对应的一个入口地址的方式。

bit[31:2]则为中断统一入口地址或向量表的基地址。

2.4 mepc

该寄存器用于保存进入异常或中断时的程序指针,其用于在产生异常或中断时保存进入异常前的指令 PC 指针,当处理完异常或中断后,mepc 被作为返回地址,用于异常或中断返回。 但值得注意的是:

- 当发生异常时,mepc寄存器被更新为当前产生异常的指令的PC值;

-

当发生中断时,mepc被更新为下一条指令的PC值。(也就是比异常的情况多+4)

本文介绍了在RISC-V架构的背景下,如何利用沁恒微电子的青稞V4F系列MCU(如CH32V307)进行实践学习,包括青稞V4F的指令集扩展、特权模式、CSR寄存器如marchid、mstatus、mtvec和mepc的功能详解。

本文介绍了在RISC-V架构的背景下,如何利用沁恒微电子的青稞V4F系列MCU(如CH32V307)进行实践学习,包括青稞V4F的指令集扩展、特权模式、CSR寄存器如marchid、mstatus、mtvec和mepc的功能详解。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?