Lab7 主要围绕具有特定复杂约束条件的设计展开,包括时钟、输入输出延迟、外部负载等方面的约束设定与分析,旨在让学习者掌握处理复杂约束设计的综合技术。能够对包含正沿和负沿触发寄存器、输入 / 输出由多条路径驱动 / 捕获、外部输入 / 输出路径具有非默认延迟以及输入驱动器扇出到额外外部负载等情况的设计进行约束。完成约束设计的编译,并理解时序报告中的条目与其相应约束的关系。

- 将 lab4/scripts/MY_DESIGN.con 文件复制并重命名为 lab7/scripts/MY_DESIGN.con。

- 根据后续页面的规范和原理图完成约束,检查并纠正语法(如同 Lab3 和 Lab4 中那样)。

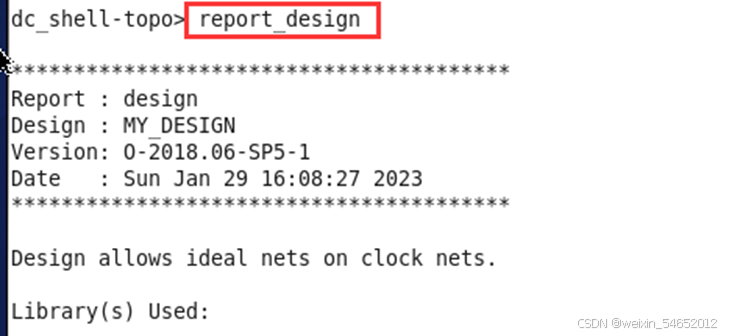

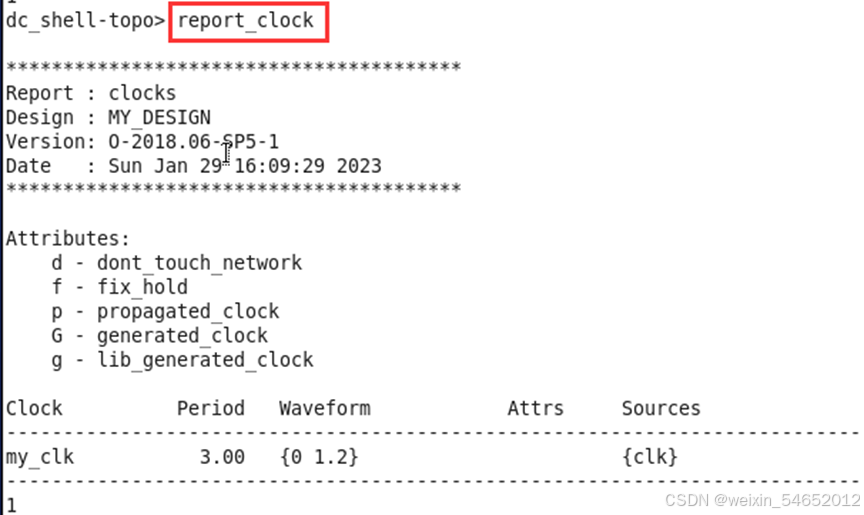

- 从 lab7 目录调用 Design Compiler,读取./rt1/MY_DESIGN.V 文件。

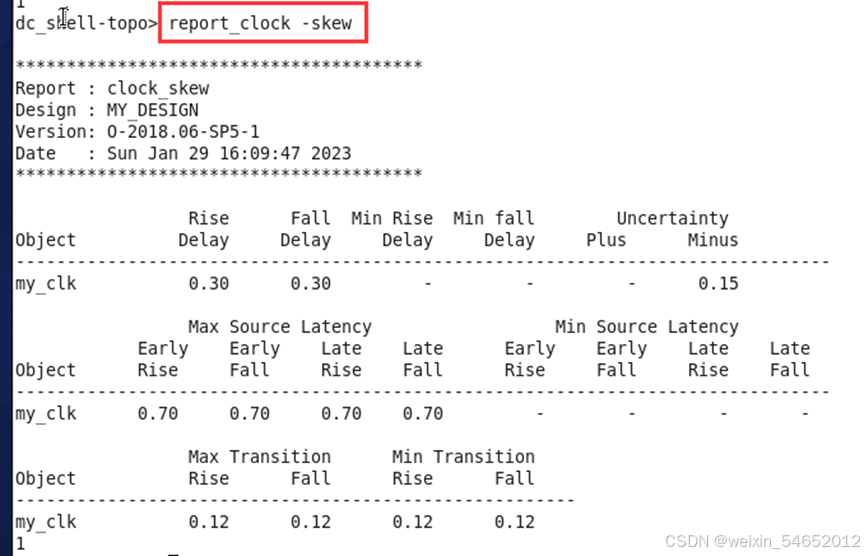

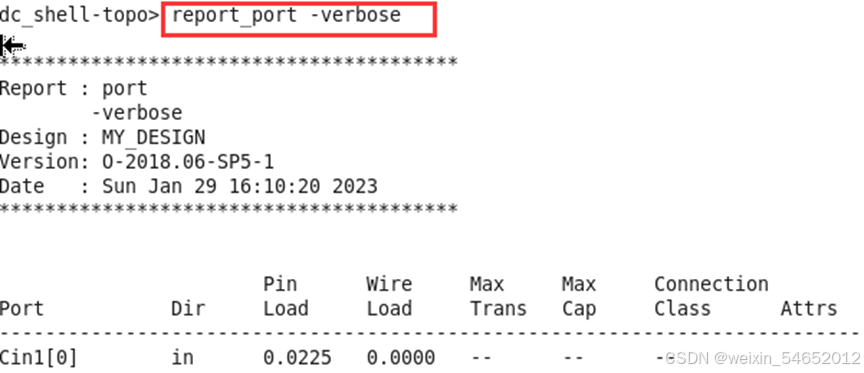

- 应用、验证并纠正约束(如 Lab3 和 Lab4 中操作),必要时与.solutions/MY_DESIGN.WSCr 或.solutions/MY_DESIGN.con 进行对比。

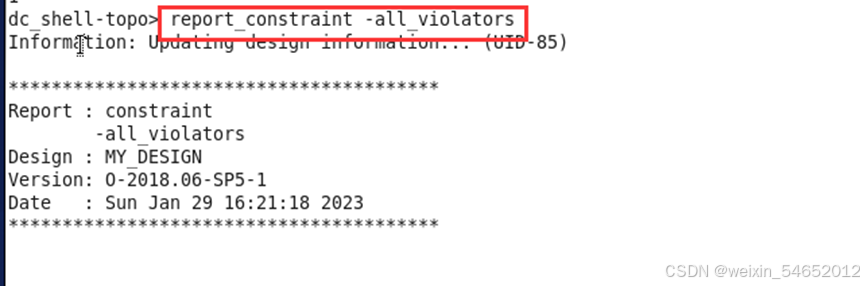

- 生成约束报告(report_constraint -all_violators),回答设计是否有时序或 DRC 违规等问题。

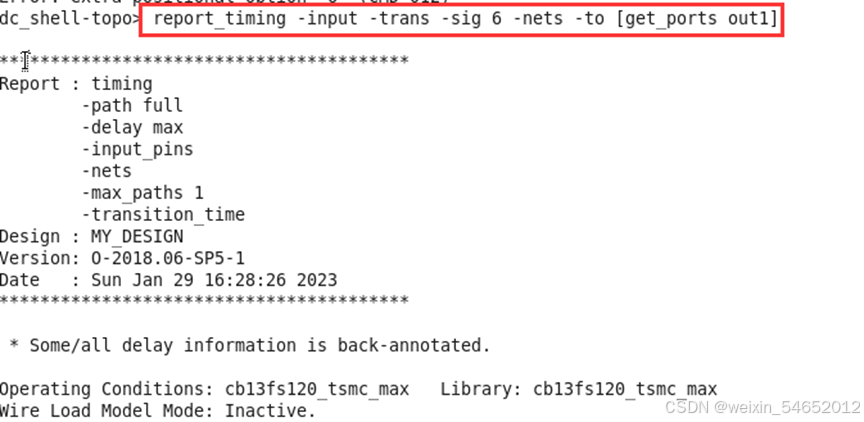

- 生成不同路径(如到 out1 输出路径、从 sel 输入到 Cout 输出路径等)的时序报告,报告中需显示特定信息(如网表转换时间、网延迟、扇出等),并根据报告回答相关问题,如路径起点、时钟相关参数、违规原因等。

![]()

- 验证 COMBO 路径(从 Cin * 到 Cout)是否符合 2.45ns 的规范要求。

- 保存设计到映射目录并退出 Design Compiler。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?