word文档免费下载地址:https://download.csdn.net/download/weixin_55953651/87962202

1.嵌入式系统调试方法概述

通用计算机一般采用桌面操作系统,调试器与被调试的程序常位于同一台计算机上,OS也相同,调试器进程通过OS提供的调用接口(API)来控制被调试的进程;

嵌入式应用程序通常采用嵌入式操作系统,运行在嵌入式系统上,开发主机常采用通用计算机,开发机和目标机处于不同的机器中,程序在开发主机上开发(编辑、交叉编译、连接定位等),然后下装到目标机(嵌入式系统)进行运行和调试(远程调试)。

由于这种差异,导出如下问题:

Ø 不同0S之上的调试器与被调试程序之间如何通信;

Ø 被调试程序出现异常如何告知调试器;

Ø 调试器如何控制及访问被调试程序等。

目前采用两种调试方法解决上述问题: monitor方式和片上调试方式。

1.1 monitor方式

monitor方式是在目标OS与调试器内分别内置专用功能模块,用于相互通信从而实现调试功能。两者应通过指定的通信端口并依据相同的远程调试协议来实现通信。

目标OS的所有异常处理最终都必须转向通信模块,通知调试器此时的异常号,调试器再依据该异常号向用户显示被调试程序发生了哪一类型的异常现象。调试器控制及访问被调试程序的请求都将被转换为对调试程序的地址空间或目标平台的某些寄存器的访问,目标OS接收到此类请求时可直接进行处理。

图1. monitor方式

限制:

➢采用monitor方式,目标OS必须提供支持远程调试协议的通信模块和多任务调试接口,此外还需改写异常处理的有关部分。目标OS需要定义一个设置断点的函数。

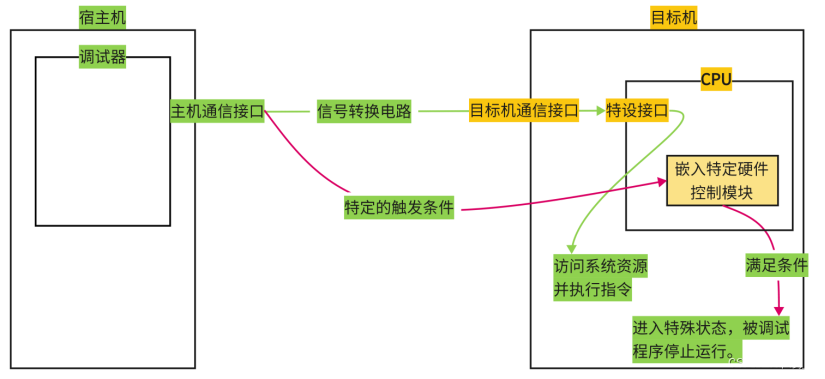

1.2 片上调试方式

片上调试方式是在CPU内部嵌入额外的硬件控制模块,当满足了特定的触发条件时进入某种特殊状态。在该状态下,被调试程序停止运行,主机的调试器可以通过CPU外部特设的通信接口来访问系统资源并执行指令。

限制:

➢主机通信端口与目标板调试通信接口通过一块简单的信号转换电路板连接。

➢内嵌的控制模块以监控器或纯硬件资源的形式存在,包括一些提供给用户的接口,如JTAG方式和BDM方式。

图2. 片上调试方式

2. 嵌入式系统调试方法

2.1 基于主机的调试

指没有目标机或目标机是通用计算机平台(如PC104)的一种调试。

基于C语言可移植性原理,有许多程序模块完全可以在主机上开发和调试,这些模块应该用标准C语言编写,与硬件无关,如各种算法程序。

对于汇编语言代码,可以在主机上使用指令模拟器( InstructionSet Simulator, ISS)运行它们,直到需要测试代码与目标系统特殊硬件之间的实时交互操作为止。

限制:

基于主机的调试主要存在两大问题,一是目标系统外设无法交互,二是两种计算机体系结构特征:字长与字节排序问题。

➢字长问题可以通过定义可移植的数据类型来解决。

➢字节排序问题主要是大小端问题。如果主机不支持大小端配置,那么需要在软件移植到目标系统上之后,调试大小端问题,或者将目标机的大小端配置成与主机的大小端配置相同。

举例:

基于主机的调试方法的例子如基于uC/OS-II操作系统的应用开发。基于uC/OS-II的应用开发可以通过计算机进行,该OS提供了可移植的数据类型定义,兼顾了大小端问题,开发完成后,只需要修改少量的移植代码,就可以把应用移植到目标系统中。

基于主机的调试方法的另一个例子是ATI公司的MNT ,Nucleus Plus是ATI公司的一个商用嵌入式实时多任务操作系统,支持众多的处理器。MNT是一个仿真开发平台,利用MNT,用户可以在基于Windows操作系统的计算机上,开发和调试基于Nucleus Plus的应用程序,等目标硬件调试完成后,直接移植到目标机上运行,实现嵌入式软件和硬件的并行开发。

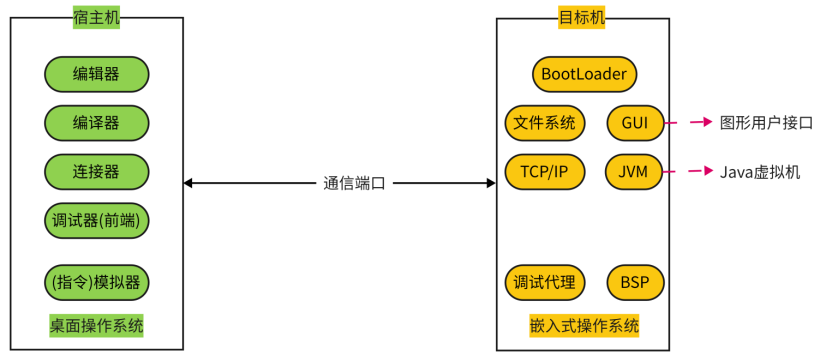

2.2 远程调试器与调试内核

嵌入式目标系统平台一般缺少支持具有完整特性的调试器所需的资源,嵌入式系统调试器通过分离自身来避开这种限制。调试器的大部分驻留在主机中,余下部分驻留在目标机中,留在目标系统中的主要是调试代理,即monitor。 调试器的两部分(主机部分和目标机部分)通过串口/并口/以太网等端口相互通信。典型调试体系结构如下图所示。

图3. 典型调试体系结构

2.2.1调试器的功能

调试器一般具有以下功能:

➢设置断点;

➢从主机中加载程序;

➢显示或修改内存与处理器的寄存器;

➢从某地址开始运行;

➢单步执行;

➢多任务调试;

➢资源查看(包括多任务信箱、信号量、队列、任务状态等) ;

➢远程调试内核功能与调试器前端的用户界面紧密配合。

2.2.2调试代理

调试代理需要两种目标系统资源:一是中断向量,二是软件中断。

调试代理以中断服务程序ISR的方式提供,中断源一般设置成高优先级中断,有时与NMI(不能屏蔽的中断)的中断优先级一样高,通常来自于串口/并口/以太网等设备,由主机控制中断发生与否,以保证调试器访问中断总能被处理到,否则如果某个应用程序关闭了所有中断,那么调试器就再也不能恢复对系统的控制了。

当主机发送命令给目标机,目标机就会立即停止应用软件代码的执行并进入调试代理ISR,保存当前CPU的上下文,然后调试器就控制了目标系统。

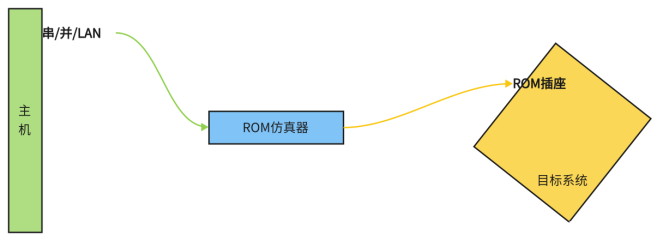

2.3 ROM仿真

2.3.1 ROM仿真器概述

ROM仿真器就是仿真ROM(只读存储器),是用RAM(随机存储器)以及附加电路制成。ROM仿真器是一个有2个电缆的盒子:

(1)一端连接到主机串口,下载新的程序到ROM仿真器;

(2)另一端插在目标系统的ROM插座上,目标平台认为它在访问ROM,而它实际访问的是ROM仿真器的RAM,该RAM中含有用户所下载的用于测试的程序。

图4. ROM仿真器

ROM仿真器的用途是为程序开发过程(编辑、编译、下载、调试)节省时间,不用频繁为EPROM进行插拔、擦除、烧写、校验等重复性耗时操作(用快速RAM替代EPROM)。使用ROM仿真器,可将生成程序用ROM仿真器下载到目标系统,运行它,并根据运行结果对主机程序进行修改,再下载,再运行,以至循环。

2.3.2 ROM仿真器的组成

ROM仿真器包括以下元件:

用于匹配目标系统ROM芯片接口的电缆和插座;

用于代替目标系统中ROM的快速RAM;

本地控制处理器;

连接到主机的通信端口;

附加特性,如跟踪存储器、闪存编程算法等。

2.3.3 ROM仿真器的功能

(1)EPROM采用MOS管,速度较慢。采用ROM仿真器可以缩短调试周期。烧写一个大的EPROM芯片有时长达几个小时。

(2)灵活设置断点。EPROM中的程序往往是“干净”的程序,不含调试信息,ROM仿真器实际上是RAM,可以在其中嵌入调试信息,从而轻松设置断点。

(3)仿真多种接口。有时目标机的通信端口不够用,ROM仿真器通过建立到主机的虚拟UART端口解决问题。

注意: ROM仿真器不是开发嵌入式系统必需的设备,如果目标系统有JTAG/BDM端口,或目标系统的调试采用monitor方式,则不需要。

2.4 在线仿真ICE

2.4.1 概述

在线仿真是最直接的仿真调试方法。ICE提供自己的CPU和MEM(内存),不再依赖目标系统的CPU和MEM。电缆或特殊的连接器使ICE的CPU能代替目标系统的CPU。ICE的CPU一般与目标CPU相同。ICE和目标系统通过连接器组合在一起,这个系统在调试时使用ICE的CPU和MEM、目标板上的I/O接口。完成调试之后,再使用目标板上的CPU和MEM实时运行应用程序。

目标系统程序驻留在目标内存中,而调试代理存放在ICE的MEM中。当处于正常运行状态时,ICE处理器从目标内存读取指令。当调试代理控制目标系统时,ICE从自己的本地MEM中读取指令。这种设计确保ICE始终保持对系统运行的控制,甚至在目标系统崩溃后也是如此,保护调试代理不受目标系统错误的破坏。

2.4.2 实时跟踪功能

当仿真器连接到目标系统上后,得到实时跟踪信息是一件很容易的事。只需将仿真器连接到所需处理器的三总线(地址总线、数据总线、控制/状态总线)上即可。

2.4.3 连接方法

ICE的连接器与目标系统的处理器引脚完全对应,ICE与目标系统完成连接后,ICE中的处理器代替了目标系统的处理器,因此,ICE的控制电路必须要插入到CPU引脚与目标系统之间,连接如下:

Ø 直接连接(适用于ICE的插座能很容易地插入目标系统)

如常用的MCS-51单片机的开发模式。其插座引脚设计与微处理器的引脚设计相匹配,实现轻松替换,方法是将目标系统上的CPU拔掉,插上ICE的仿真头。

Ø 间接连接(适用于ICE的插座不能很轻易地插入目标系统)

其原理就是不拔走目标系统的CPU,但使其所有引脚变成开路状态(三态)。某些处理器具有专用输入引脚,能使其进入关闭状态。调试人员就可以把带有仿真器信号的连接器作为覆盖物插入到目标系统中。

2.4.4 优缺点

优点是具有实时跟踪能力,缺点是价格较高,特别是高速CPU在线仿真器。一般用于中低速系统中,如单片机仿真器。

2.5 BDM

BDM ( Background Debug Model,背景调试模式)是Motorola公司的专有调试接口,该公司是第一个把具有CPU调试功能的特殊硬件放在CPU核心中的嵌入式微处理器厂商,BDM开创了片上集成调试资源的趋势。硬件设计仅仅需要把CPU的调试引脚连接到专用连接器(n-wire或Wiggler) 与调试工具上。

Ø n-wire优点:机械连接较简单,与目标系统上的CPU一起运行,与CPU的变化无关,简化设计工具,低成本、可重用、简单;

Ø n-wire缺点: 大多数只提供运行控制,特性受限于芯片厂商,非常慢,不支持覆盖内存,不能访问其它总线。

BDM首先在Motorola公司的683XX系统上实现,使用在ColdFire系列处理器中。它包括一个安装在目标处理器板上的26针连接器。BDM调试接口的引脚输出表如图。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-D7oUdW8y-1663405469064)(新建 Markdown/wpsB580.tmp.jpg)]](https://img-blog.csdnimg.cn/60966714e6c44747be8a62aeaa5d6ae7.png)

图5. 引脚输出表

Ø BDM同时支持处理器控制和定时跟踪监视方式。

Ø 4个二进制位DDATAO~DDATA3用于输入调试数据和控制命令;

Ø 4个二进制位PSTO~PST3用于在处理器运行时输出处理器状态;

Ø 通过分析来自BDM接口的信息流可以为开发人员提供关于处理器核心运行状态的重要信息。

Ø BDM中的命令是BDM直接发送到CPU,并且其操作独立于任何用户想要执行的代码(处理器指令系统中的代码)。

以下是BDM命令集。

注:

终止——为执行此命令,CPU必须终止运行;

周期窃取——命令产生一个总线周期,把它插入到CPU访问周期中;

并行——命令与CPU活动并行执行。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BqSenP6i-1663405469065)(新建 Markdown/wpsB581.tmp.jpg)]](https://img-blog.csdnimg.cn/8d82163fcb1a47cbbe36a302aa25b13d.png)

2.6 JTAG

从使用上看,JTAG (Joint Test Action Group,联合测试行动小组)与BDM类似,支持JTAG调试的 处理器上集成了符合JTAG协议的硬件调试接口。JTAG仿真器包括硬件和软件两部分。

硬件有两个接口,一个接口连接到计算机上,有串口、并口、网络口、USB口等;另一个接口与目标处理器的JTAG引脚相连。

软件把调试命令和数据通过仿真器发送到目标处理器中,然后接收目标处理器的状态信息。通过分析状态信息,可以了解目标处理器的工作情况;通过JTAG命令,用户可以控制目标处理器的运行(单步、断点、寄存器检查等)。

与BDM数据传输的并行方式不同,JTAG采用串行方式传输数据,占用较少的引脚。

JTAG是一种国际标准测试协议(IEEE 1149.1兼容),不同于BDM,JTAG接口是一个开放标准。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的

JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP (Test Access Port, 测试访问口),通过专用的JTAG测试工具对内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP (In-System Programmable, 在线编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程。

JTAG命令独立于处理器的指令系统,可以完全控制处理器的动作,因此JTAG调试方式是目前最有效的调试方式,与ICE相比成本低,与monitor方式相比功能强大,局限性小,可以查找硬件的故障点。

目前大多数嵌入式处理器厂商在其处理器上集成了JTAG接口,如ARM。不管ARM内核的处理器来源于哪个厂家,其JTAG接口是兼容的。通过JTAG仿真器,用户能采样并修改寄存器组、 存取内存,以及标准调试器所能做的任何事情。

由于JTAG采用串行协议,它只需要相对较少的微处理器I/O引脚就可以与调试器连接。数据流从进入CPU核心到输出CPU核心会形成一个很长的循环。

JTAG标准仅仅定义了与处理器一起使用的通信协议,而JTAG循环如何连接到核心元件,以及作为运行控制或观察元件的命令集做什么,都由厂商自己决定,因此具体做法只有厂商或很少的合作伙伴知道。

2.7 软件仿真器

软件仿真器即指令集模拟器(ISS) ,利用软件来模拟处理器硬件,模拟的硬件包括指令系统、外部设备、中断、定时器等。用户开发的应用软件像下装到目标系统硬件一样下装到软件仿真器中进行调试。

功能强大的ISS可以仿真处理器的每一个细节,包括外设和中断;简单的ISS至少可以仿真CPU的指令系统。

功能强大的ISS必须使应用程序认为自已运行在实际不存在的硬件上。应用程序的每一条被执行的指令都必须忠实地被ISS模拟。

低档ISS可能只简单地模仿一块芯片和内存的行为。

有的ISS提供了对指令的执行时间的仿真。其使用的软件时钟有两种:

Ø 一是实时时钟,利用CPU的时钟运行嵌入式处理器的指令,只仿真指令的执行结果,不仿真执行时间;

Ø 另一种是仿真时钟,用户可以设置仿真时钟与处理器的时钟相同,不仅可以仿真指令的执行结果,也可以仿真指令的执行时间和软件的执行时间,如ARM公司的AXD仿真器。

高档仿真器可建立一个较大实时系统的模型,甚至能仿真不存在的硬件。因此开发者可以就一个硬件还没有开始设计的项目进行软件开发,并验证软件的正确性、实时性等指标。

2.7.1 软件仿真器的优点

(1)可以使嵌入式系统的软件和硬件并行开发;

(2)可以发现和定位应用程序的逻辑错误,甚至可纠正某些与硬件相关的故障;

(3)可以评估嵌入式系统产品的设计性能。

2.7.2 软件仿真器的缺点

(1)运行速度慢(10~100倍)。低档嵌入式系统可仿真,高档嵌入式处理器只能进行正确性仿真,无法仿真系统性能。

(2)只能仿真软件的正确性,无法仿真与时序有关的错误,适用验证软件的算法。

可以设置仿真时钟与处理器的时钟相同,不仅可以仿真指令的执行结果,也可以仿真指令的执行时间和软件的执行时间,如ARM公司的AXD仿真器。

高档仿真器可建立一个较大实时系统的模型,甚至能仿真不存在的硬件。因此开发者可以就一个硬件还没有开始设计的项目进行软件开发,并验证软件的正确性、实时性等指标。

2.7.1 软件仿真器的优点

(1)可以使嵌入式系统的软件和硬件并行开发;

(2)可以发现和定位应用程序的逻辑错误,甚至可纠正某些与硬件相关的故障;

(3)可以评估嵌入式系统产品的设计性能。

2.7.2 软件仿真器的缺点

(1)运行速度慢(10~100倍)。低档嵌入式系统可仿真,高档嵌入式处理器只能进行正确性仿真,无法仿真系统性能。

(2)只能仿真软件的正确性,无法仿真与时序有关的错误,适用验证软件的算法。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?