目录

第一章-计算机系统基础

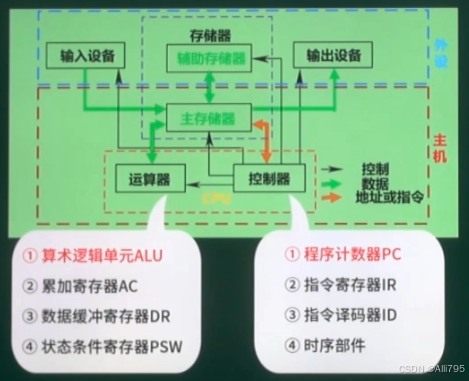

计算机的基本组成

运算器

1 算术逻辑单元ALU:数据的算术运算和逻辑运算

2 累加寄存器AC:通 用寄存器,为ALU提供一个工作区,用在暂存数据

3 数据缓冲寄存器DR:写内存时,暂存指令或数据

4 状态条件寄存器PSW:存状态标志与控制标志

控制器

1 程序计数器PC:存储下一条要执行指令的地址

2 指令寄存器IR:存储即将执行的指令

3 指令译码器ID:对进行分析解释

4 时序部件:提供时序控制信号指令中的操作码字段

基本概念

CPU的性能指标:主频、字长、CPU缓存、核心数量

总线的分类:数据总线、控制总线、地址总线

总线的性能指标:带宽、位宽、工作频率

BIOS/CMOS

系统性能评测方法:时钟频率、指令执行、等效指令速度法、数据处理速率(PDR)、核心程序法、基准测试程序

总线系统

一条总线同一时刻仅允许一个设备发送,但允许多个设备接收。

总线的分类:

数据总线:在CPU与RAM之间来回传送需要处理或是需要存储的数据。

地址总线:用来指定在RAM之中存储的数据的地址。

控制总线:将微处理器控制单元的信号,传送到周边设备。

总线的性能指标:

带宽、位宽、工作频率

寻址方式

立即寻址方式

特点:操作数直接在指令中,速度快,灵活性差

直接寻址方式

特点:指令中存放的是操作数的地址

间接寻址方式

特点:指令中存放了一个地址,这个地址对应的内容是操作数的地址

寄存器寻址方式

特点:寄存器存放操作数

寄存器间接寻址方式

特点:寄存器内存放的是操作数的地址

流水线

流水线:多条指令重叠进行操作的一种准并行处理实现技术。

——>取指——>分析——>执行——>

流水线的周期:执行时间最长的一段

流水线计算公式

1条指令执行的时间+(指令条数-1)*流水线周期

①理论公式:

②实践公式:

(不常用)

流水线的吞吐率(TP)计算的最基本的公式为:

流水线最大吞吐率:流水线周期的倒数

例:若指令流水线把一条指令分为取指、分析、执行三部分,且三部分的时间分别是取指2ns,分析2ns,执行1ns。那么,流水线周期是?100条指令全部执行完毕需要的时间就是?

多级存储器结构

存储器被组织成金字塔形的层次结构:

存储器自上而下,组成6个层次结构,依次变得更慢、访问频率更低、容量更大、每字节的造价更便宜

Cache

功能:提高CPU数据输入输出的速率,突破所谓的“冯·诺依曼瓶颈”

速度:在计算机的存储系统体系中,Cache是访问速度较快的层次

原理:使用Cache改善系统性能的依据是程序的局部性原理

组成:Cache由两部分组成:控制部分和Cache存储器部分

平均系统周期时间(以读操作为例:使用“Cache+主存储器”)

h代表对Cache的访问命中率,t1表示Cache的周期时间,t2表示主存储器周期时间,系统的平均周期为t3,(1-h)又称为失效率(未命中率)

8106

8106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?