一、引言

本期分享一些关于硬件电路设计的重点知识。在硬件电路中,晶振是电子系统中的重要组成部分,它能够为微控制器、数字电路以及处理器提供稳定的时钟信号。本期分享的是关于晶振电路的设计教程,后续关于硬件电路的其他设计都会做出详细教程,感兴趣的朋友点赞跟关注来支持一下小编吧!

二、晶振电路常识

晶振按不同分类可分为多种不同的晶振。比如:

按频率来分类可分为低频晶振、高频晶振、微波晶振。

按封装形式分类可分为插件晶振、贴片晶振。

按材料分类可分为石英晶振、陶瓷晶振、水晶晶振。

不同种类的用途都不同,其不同工作环境下的工作温度、负载电容的大小、频率精度以及驱动电平都具有不同的参数,应分析应用条件去挑选合适的晶振。但是不同的晶振在PCB设计上仍有相同的要求。

三、晶振电路的设计重点

1、基本电路设计

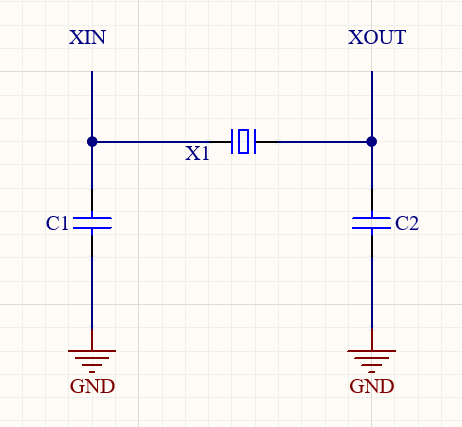

典型的晶体谐振器电路设计如图所示。其中XIN跟XOUT分别为晶振的输入跟输出信号。

2、负载电容计算

在基本电路设计中的电容C1、C2的取值计算需要通过该公式来计算:

CL = (C1 × C2)/(C1 + C2) + Cstray。其中的Cstray为PCB的寄生电容,通常在3到5PF之间。

3、反馈电阻选择

在晶振电路中反馈电阻Rf (并联在晶振两端或放大器输入输出之间的电阻 ) 的选择对电路的起振非常重要,它能够提高电路的稳定性。

通常选择低频晶振为1MΩ,高频晶振为470kΩ。

4、晶振驱动电平控制

在晶振电路中,驱动电平(Drive Level, DL)的控制能保证晶振稳定工作。驱动功率过高会导致晶振可能引起谐波失真并且过热缩短其寿命甚至损坏,功率过低也会导致其振荡不稳定甚至停振。

驱动电平的计算公式通常可用该公式:

![]()

Irms:流过晶振的交流电流有效值 Resr:晶振的等效串联电阻

四、PCB的布局与布线

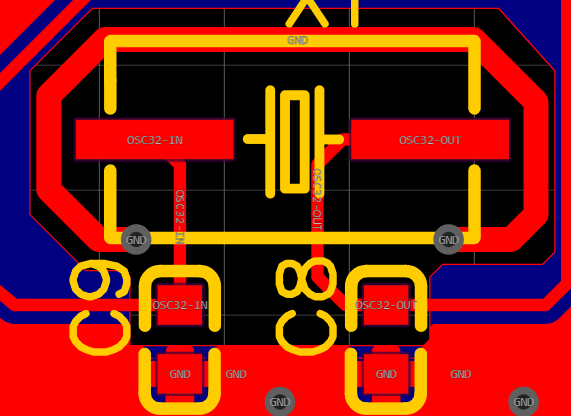

晶振的放置位置尽量靠近MCU时钟引脚,要避免去靠近发热的元器件,同时也要远离IO端口以及高速信号线。晶振电路的负载电容接地端直接与地层连接,注意要在晶振下方铺上地平面,该位置走线尽量用短直线,转角处使用45度或圆弧做转角处理。最后晶振周围做地环保护,有利于消除信号干扰。

如果在四层以及四层板以上的话优先布局在内层(地层之间),若需要在外层放置需在下方铺上完整地平面。

五、EMC设计以及屏蔽

在晶振周围可做接地铜皮环,需要高频环境时可用金属屏蔽罩保护。尽量避免晶振周围有敏感电路的放置。在接地环处每隔λ/20打接地过孔以及在负载电容接地端就近打过孔有利于优化高频信号的返回路径、抑制电磁干扰(EMI)并提高信号完整性。

六、常见问题分析

①晶振不起振:遇到晶振无法起振时需要检查电源电压供电是否稳定,若电源电压稳定需检查负载的电容值是否符合要求,检查PCB的布局是否正确(可能受到外界因素干扰)

②时钟信号不稳定:

办法一:优化电源的去耦电路

办法二:对接地PCB处理进行改善

办法三:检查信号是否完整

③频率偏差过大:优先确定晶振的规格参数,计算负载电容的参数是否正确,最后可查看PCB的寄生电容是否异常

七、总结

以上为小编在晶振电路设计的全部经验总结。在设计晶振电路时首先对器件进行选型,其次进行合理的电路设计然后进行优化PCB的布局处理,最后进行EMC设计规划及充分考虑。但无论设计那个电路模块,都需要统筹兼顾整体布局,实际情况实际处理做出最优的解决方案。 小编创作不易,对朋友们有帮助的话三连支持一下!下次出其他PCB的设计详细教程!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?