计算机组成原理 部分题目汇总

一. 简答题

- RISC和CICS 简要说明,比较异同

RISC(精简指令集)注重简单快速的指令执行,使用少量通用寄存器,固定长度指令,优化硬件性能,依赖软件(如编译器)来提升效率。

CISC(复杂指令集)包含多样复杂的指令,能一条指令完成多步操作,采用变长指令,减少指令数但可能增加执行时间,倾向于硬件直接支持复杂功能减轻软件负担。

两者均追求高性能,但RISC偏重硬件效率,CISC侧重指令集成度。现代设计趋向结合两者优点。

当浮点数运算的结果为非规格化时,要进行规格化处理,即左规。将尾数算数左移一位,阶码减1。

当浮点数运算的结果尾数出现溢出(双符号位为01或10)时,右规。将尾数算数右移一位,阶码加1。

在IEEE 754浮点数运算中,浮点运算结果是否溢出,主要看阶码是否溢出。在运算过程中,可能会发生阶码上溢或阶码下溢。阶码上溢时,说明结果的数值太大,无法表示,是真正的溢出;阶码下溢时,说明结果数值太小,可以把结果近似为0

(1) 计算机内部采用层次化存储体系统结构是为了平衡存储容量、访问速度和成本之间的关系。该结构由高速缓存(Cache Memory)、主存(RAM)、辅助存储器组成,逐层降低访问速度,增大存储容量,降低成本。

(2) SRAM 芯片具有速度快、稳定可靠的特点,常用于 CPU 缓存(Cache),但价格昂贵且密度低。DRAM 芯片具有密度高、成本低的优点,主要用于主存(RAM),但访问速度相对较慢,需定期刷新。

(3) CPU 和主存之间有两种通信定时方式:同步定时和异步定时。SDRAM 芯片采用同步定时方式与 CPU 交换信息,即 CPU 根据时钟信号发送读写请求,SDRAM 在指定周期内响应。

二. 综合题

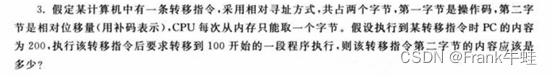

1. 指令系统

100 - (200 + 2) = -102,即补码表示为10011010B

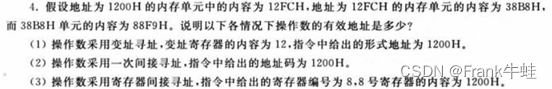

- 有效地址 EA=000CH+1200H=120CH,操作数未知

- 有效地址 EA=(1200H)=12FCH,操作数为38B8H

- 有效地址 EA=1200H,操作数为12FCH

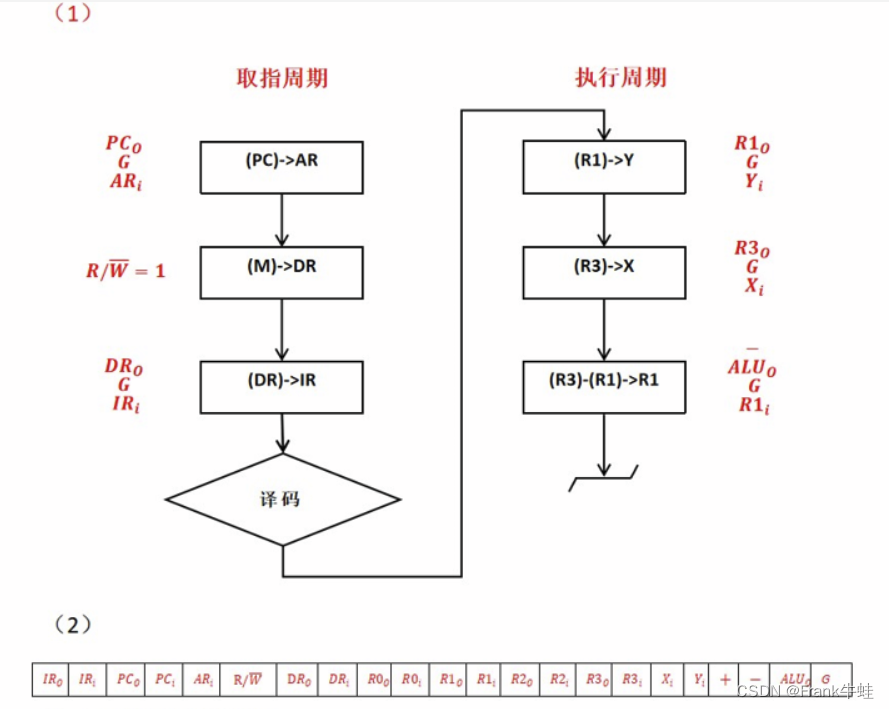

2. 中央处理器

3. 存储系统

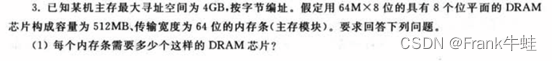

- 每个内存条的容量为512MB,而每个DRAM芯片的容量为64M×8位=64MB。所以每个内存条需要512MB/64MB=8个DRAM芯片。

- 主存的容量为2GB,而每个内存条的容量为512MB。所以需要2GB/512MB=4个内存条。

- 主存的最大寻址空间为4GB,按字节编址,所以主存地址共有32位。64M×8 位的DRAM芯片,26位用于片内行地址,1 位用于片内列地址,5位用于选择芯片.

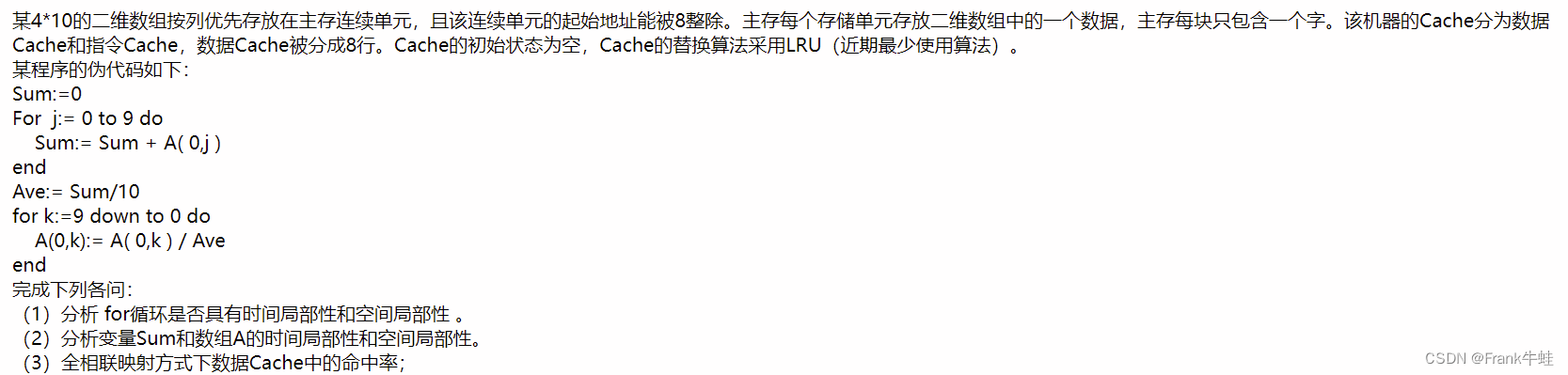

- for循环具有时间和空间局部性。

- 变量Sum只有时间局部性,没有空间局部性;二维数组按列优先存放,数组A没有空间局部性,没有时间局部性。

- 全相映射方式下数据Cache中的命中率为8/20=40%,其中8次为在Cache命中次数,程序中20为访问cache的总次数。

某外传送信息的最高频率为40K次/秒,而相应的中断处理程序的执行时间为40us,问该外设是否可以采用中断方式工作?为什么?

外设传送一个数据的时间 t = 1/f = 1/(40 *1000)s = 25us,中断请求周期为 25us。由题目条件知,采用中断方式执行一次 I/O 的时间最少是 40,因此如果采用中断方式实现 I/O 将导致部分数据的丢失,故不能采用中断方式。

1598

1598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?