基本描述

FL-L系列设备是使用浮动栅极技术和65纳米工艺光刻技术的非易失性闪存产品。这些设备通过串行外设接口(SPI)与主机系统连接。支持传统的SPI单比特串行输入和输出(单I/O或SIO),以及可选的两比特(双I/O或DIO)和四比特宽的四倍I/O(QIO)和四倍外设接口(QPI)命令。此外,对于QIO和QPI,还有双数据速率(DDR)读命令,可以在时钟的两个边缘传输地址和读取数据。

解释:

FL-L系列设备是一种特殊的存储芯片,使用了一种叫做浮动栅极技术的方法来存储信息,而且是在很细小的尺寸上(65纳米工艺)进行制造的。这种芯片能长时间保存数据,即使断电也不会丢失信息,因此被称为非易失性存储设备。

这些芯片通过一种叫做SPI(串行外设接口)的方式与电脑或其他设备连接。SPI是一种允许电子设备之间进行数据交换的方法。FL-L系列支持几种不同的SPI工作方式:

单I/O或SIO:标准的一线通信方式,一次发送一个数据位。

双I/O或DIO:升级版的通信方式,一次可以发送两个数据位。

四倍I/O(QIO)和四倍外设接口(QPI):更高级的通信方式,一次可以发送四个数据位。

四倍I/O(Quad I/O, 简称QIO)和四倍外设接口(Quad Peripheral Interface, 简称QPI)是SPI(串行外设接口)的高级通信模式,它们能够一次性传输四个数据位,从而显著提高数据传输的速度。

在标准的SPI通信中,数据通常是通过单一的数据线(MOSI用于数据发送,MISO用于数据接收)逐位串行传输的。然而,在QIO模式下,数据传输使用了四条数据线(而不仅仅是MOSI和MISO),这四条线同时用于数据的输入和输出。这意味着在每个时钟周期内,可以同时发送或接收四个数据位,相比单线或双线SPI,数据传输效率得到了显著提升。

QPI模式则是QIO的一个变种,它进一步优化了通信协议,以支持更高效的数据传输。QPI通常用于高速闪存存储设备,它不仅使用四条数据线进行数据传输,而且还优化了命令和地址传输的方式,使得整个通信过程更加高效。

简而言之,QIO和QPI通过同时使用四条数据线来传输数据,大大加快了数据的读写速度,非常适合需要快速数据访问的应用,如高速闪存、高性能嵌入式系统等。这使得设备能够快速启动和运行程序,提高了整体性能。

此外,这些芯片还支持一种叫做双数据速率(DDR)的读取命令,这意味着它们可以在时钟信号的上升沿和下降沿同时传输数据,这样可以更快地读取数据。

想象一下时钟的摆动,它有上升的动作(上升沿)和下降的动作(下降沿)。在传统的数据传输中,每次时钟摆动只在一个动作上(比如上升沿)传输数据。这就像是每次心跳只在心脏收缩时推动血液流动,而在心脏舒张时不推动血液。

双数据速率(DDR)技术改变了这一点,它利用时钟的上升沿和下降沿来传输数据。这意味着在时钟的每一次摆动中,数据可以在上升沿传输一次,在下降沿再传输一次,从而使得数据传输的速率加倍。回到心脏的比喻,就像是心脏在收缩时也好,舒张时也好,都能推动血液流动,效率自然就翻倍了。

所以,当我们说FL-L系列芯片支持双数据速率(DDR)读命令时,意思是这些芯片能够在时钟信号的每个周期内传输两次数据,大大提高了数据的读取速度。这对于需要高速处理大量数据的应用来说,是一个非常有用的功能。

简而言之,FL-L系列芯片是一种高级的存储设备,能以非常快的速度与电脑或其他电子设备进行数据交换,适合需要快速读写大量数据的应用场景。

FL-L系列的架构特点包括一个页面编程缓冲区,允许一次操作编程最多256字节,并提供单独的4KB扇区、32KB半块扇区、64KB块扇区或整个芯片擦除。

通过在支持的更高时钟频率下使用FL-L系列设备,配合四倍命令,指令读取传输率可以匹配或超过传统的并行接口、异步NOR Flash存储器,同时大幅减少信号数量。

FL-L系列产品提供高密度以及移动或嵌入式应用所需的灵活性和快速性能。这些存储器为有限的空间、信号连接和电源的系统提供了理想的存储解决方案。它们提供的灵活性和性能远超普通的串行闪存设备,非常适合代码影射到RAM、直接执行代码(XIP)和存储可重新编程数据。

特点

这段描述提到的特性属于一种先进的串行外设接口(SPI)闪存,具备多种输入/输出(I/O)选项和其他高级功能。

SPI与多I/O特性

时钟极性和相位模式0和3:支持灵活的时钟设置,以适应不同的通信需求。

双数据率(DDR)选项:允许在每个时钟周期传输两次数据,提高数据传输效率。

四倍外设接口(QPI)选项:通过增加数据线的数量来进一步提高传输速率。

扩展地址:支持24位或32位地址选项,使得可以访问更大的存储空间。

与S25FL-A、S25FL1-K、S25FL-P、S25FL-S和S25FS-S SPI系列兼容:确保了与现有产品的兼容性。

读取功能

命令:支持多种读取命令,包括常规读取、快速读取、双I/O、四I/O等,以适应不同的应用场景。

模式:支持突发包装、连续读取(XIP)和QPI模式,提高灵活性和效率。

序列闪存可发现参数(SFDP):通过标准化方式获取配置信息,简化设备初始化和配置过程。

编程架构

256字节的页面编程缓冲区:允许一次编程多个字节,提高编程效率。

程序挂起和恢复功能:提供更大的操作灵活性,特别是在多任务环境中。

擦除架构

统一的4 KB扇区擦除、32 KB半块擦除、64 KB块擦除:提供多种擦除选项,以适应不同的应用需求。

芯片擦除:允许一次性擦除整个芯片。

擦除挂起和恢复功能:增加了操作的灵活性。

耐用性和数据保持

至少100,000次的程序-擦除循环:确保了芯片的长期可靠性。

至少20年的数据保持能力:数据长期稳定存储,不易丢失。

安全特性

状态和配置寄存器保护:提高安全性,防止未授权访问。

四个安全区域,每个安全区域 256 字节,位于主闪存 arra 之外

传统块保护:块范围

四个安全区域:提供额外的数据保护,用于存储敏感或关键信息。

多种锁定方式:包括易失性和非易失性的扇区/块范围保护,以及安全区域的电源锁定、密码或永久保护。

技术规格

65纳米浮动栅技术:先进的制造工艺,确保了高性能和低功耗。

单一供电电压与CMOS I/O:2.7V至3.6V,适应多种电源需求。

温度范围/等级和封装

支持多种温度等级:从工业级(-40°C至+85°C/105°C)到汽车级(AEC-Q100等级1至3),满足不同环境条件下的应用需求。

多种封装选项:包括SOIC、USON、WSON和BGA,以及已知良品(KGD)和已知测试良品,提供灵活的选择以适应不同的装配和应用场景。

这种闪存芯片集成了先进的功能和高度的灵活性,非常适合需要高速、大容量且可靠的数据存储的应用,如移动设备、嵌入式系统和汽车电子。

性能概要

这个性能总结提供了关于该闪存产品的性能指标,包括最大读取速率、典型的编程和擦除速率以及典型的电流消耗情况。下面各个表格的详细描述:

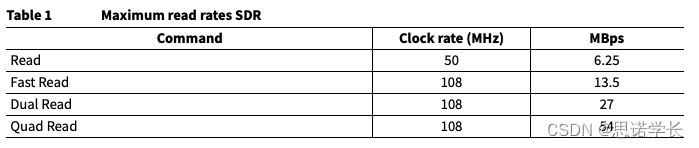

表1 最大读取速率 SDR(单数据速率)

Read(读取):在50MHz的时钟频率下,最大读取速率为6.25MB/s

Fast Read(快速读取):在108MHz的时钟频率下,最大读取速率为13.5MB/s

Dual Read(双倍读取):在108MHz的时钟频率下,最大读取速率为27MB/s

Quad Read(四倍读取):在108MHz的时钟频率下,最大读取速率为54MB/s

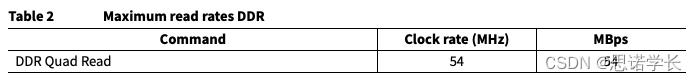

表2 最大读取速率 DDR(双数据速率)

DDR Quad Read(DDR四倍读取):在54MHz的时钟频率下,最大读取速率为54MB/s。

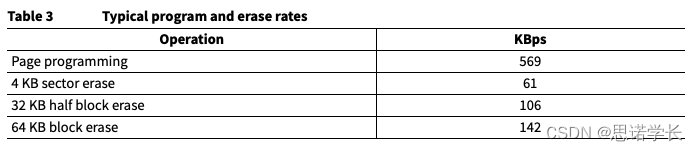

表3 典型的编程和擦除速率

页面编程:569KB/s

4KB扇区擦除:61KB/s

32KB半块擦:106KB/s

64KB块擦除:142KB/s

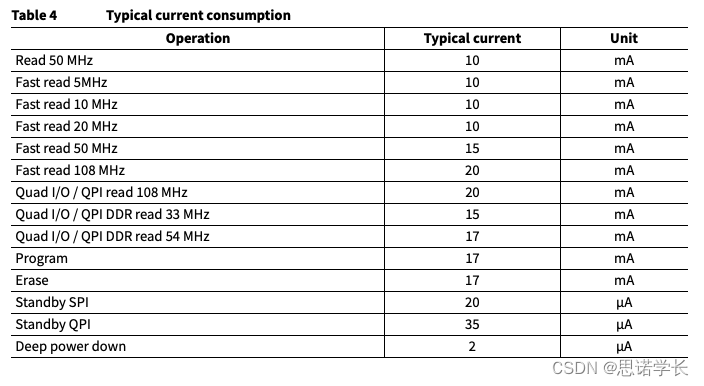

表4 典型的电流消耗

读取(50 MHz):10mA。

快速读取(5-108 MHz):根据频率不同,电流消耗在10mA到20mA之间。

Quad I/O / QPI读取(108 MHz):20mA。

Quad I/O / QPI DDR读取(33 MHz和54 MHz):在33MHz时为15mA,54MHz时为17mA。

编程:17mA。

擦除:17mA。

待机SPI:20µA。

待机QPI:35µA。

深度休眠:2µA。

这些数据表明了该存储产品在不同操作下的性能表现,其中包括读取、编程和擦除操作的速度,以及这些操作在不同条件下的电流消耗情况。这对于设计低功耗和高性能的嵌入式系统非常重要。

目录

这份文档是一份关于64Mb(8MB)FL-L闪存,支持SPI多I/O,工作电压3.0V的数据手册的目录摘要。这里提供了一个概览,用于解释目录中的各个部分:

综述:介绍了FL-L系列闪存的基本信息,包括其使用的技术和工艺。

特点:概述了产品的主要特性,如使用的技术、支持的接口类型等。

性能总结:提供了关于读取速率、编程和擦除速率以及电流消耗的数据。

目录:即当前阅读的内容部分,列出了数据手册的所有章节和主题。

1. 产品概览:详细描述了产品的概况,包括迁移说明。

2. 连接图:展示了不同引脚布局和封装类型的图表,如SOIC 16引脚、8-连接器封装等。

3. 信号描述:详细说明了SPI多输入/输出接口的信号,包括序列时钟、片选信号、输入/输出信号等。

4. 模块图:展示了系统的模块组成和框图。

5. 信号协议:解释了SPI时钟模式、命令协议、接口状态和数据保护机制。

6. 地址空间映射:描述了闪存阵列、ID地址空间、SFDP空间和安全区域的地址分布。

7. 数据保护:详细介绍了安全区域、深度掉电模式、写使能命令等数据保护相关的内容。

8. 命令:列出并解释了支持的所有命令,包括识别、寄存器访问、读取、编程、擦除、安全区域和保护相关的命令。

9. 数据完整性:介绍了擦除耐久性和数据保留能力。

10. 软件接口参考:提供了JEDEC JESD216B SFDP参数和设备ID地址映射的信息。

11. 电气规格:列出了绝对最大额定值、锁存特性、热阻和工作范围等。

12. 时序规格:提供了时钟波形的关键信息、AC测试条件、复位、SDR和DDR的AC特性等。

13. 订购信息:解释了如何根据不同的标准和汽车级别/AEC-Q100标准订购产品。

14. 物理图:展示了物理尺寸图和封装信息。

修订历史:记录了数据手册的更改和更新历史。

这份目录提供了关于FL-L系列闪存的全面信息,从产品的电气特性到物理尺寸,从性能数据到编程和安全特性,非常适合工程师和技术专家参考。

1 产品概览

1.1 迁移说明

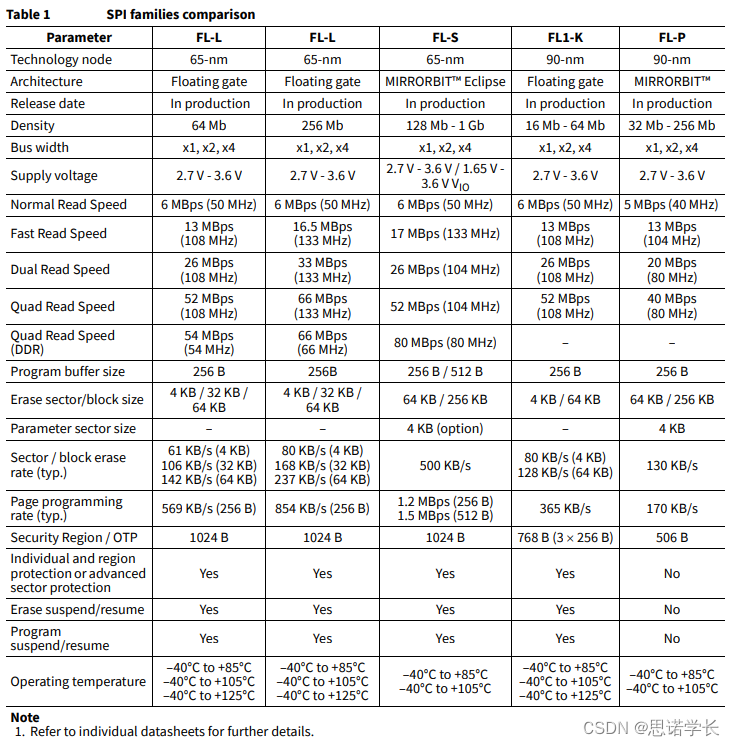

1.1.1 功能对比

FL064L 系列是命令子集,封装与上一代 FL-S、FL1-K 和 FL-P 系列兼容。

这段内容提供了FL-L系列与之前几代闪存产品(FL-S, FL1-K, FL-P)的功能对比。这些比较基于几个关键参数,如技术节点、架构、发布日期、密度、总线宽度、供应电压、读取速度、编程缓冲区大小、擦除扇区/块大小、安全区域和保护功能。下面是对比较表的中文解释:

技术节点

FL-L系列和FL-S使用了65纳米工艺,而FL1-K和FL-P则使用了较老的90纳米工艺。

架构

FL-L系列使用了浮动栅极架构。FL-S和FL1-K采用了MIRRORBIT™ Eclipse技术。

发布日期

所有系列产品都已在生产中。

密度

FL-L系列提供64Mb和256Mb两种密度选项,而FL-S系列密度范围更广,从128Mb到1Gb不等。FL1-K系列提供的密度从16Mb到64Mb,FL-P系列则从32Mb到256Mb。

总线宽度

所有系列都支持x1、x2和x4的总线宽度。

供应电压

大部分系列的供应电压范围为2.7V到3.6V。FL-S系列有一部分产品支持1.65V到3.6V的电压范围。

读取速度

在标准读取和快速读取方面,各系列产品性能相近,但在双倍读取和四倍读取方面,FL-L系列在相同频率下提供了较高的数据传输速率。FL-L系列还支持DDR四倍读取,提供了更高的速率。

编程缓冲区大小

FL-L系列、FL-S系列和FL-P系列的标准编程缓冲区大小为256B,FL1-K系列提供了256B和512B两种选项。

擦除扇区/块大小

FL-L系列提供了更多的擦除选项,包括4KB扇区擦除、32KB半块擦除和64KB块擦除。

安全区域/一次性编程(OTP)

FL-L系列提供了1024B的安全区域,相较于FL1-K的768B和FL-P的506B有所增加。

保护功能

FL-L系列支持个别和区域保护或高级扇区保护,并且支持擦除挂起/恢复功能,而FL-P系列不支持这些功能。

这个对比总结展示了FL-L系列在多个方面的技术进步,包括更先进的工艺技术、更高的读取速度和更灵活的数据保护选项,使其成为适合需要高速和高安全性存储解决方案的移动或嵌入式应用的理想选择。

这部分内容继续对FL-L系列与其他SPI家族(FL-S, FL1-K, FL-P)的功能进行对比,特别关注了编程挂起/恢复功能和操作温度范围。

### 编程挂起/恢复

- FL-L系列、FL-S系列、FL1-K系列均支持编程挂起和恢复功能,这允许在编程操作中断后,可以恢复编程而不失去数据。FL-P系列不支持这项功能。

### 操作温度范围

- FL-L系列、FL-S系列和FL1-K系列都提供了多种操作温度范围,包括:

- 标准温度范围:-40°C到+85°C

- 扩展温度范围:-40°C到+105°C

- 工业高温范围:-40°C到+125°C

- FL-P系列也提供了类似的温度范围选项。

通过这些信息,我们可以看到FL-L系列在功能上与早期的产品家族兼容,同时提供了更广泛的操作温度范围,以适应不同环境条件下的应用需求。这些特性使得FL-L系列产品非常适合在苛刻环境下使用,包括那些需要高可靠性和长时间运行的嵌入式系统和工业应用。

1.1.2 与前几代产品的已知差异

1.1.2.1 错误报告

FL-K、FL1-K 和 FL-P 存储器要么没有错误状态位,要么在受保护扇区上尝试编程或擦除时不设置错误状态位。此产品系列确实具有用于编程和擦除操作的错误报告状态位。

当内部无法编程或擦除时,或者尝试编程或擦除受保护扇区时,可以设置这些设置。在这些情况下,程序或擦除操作未按照命令的要求完成。

P_ERR 位或 E_ERR 位以及 WIP 位将在 SR1V 中设置为并保持 1。必须发送 Clear Status Register 命令以清除错误并将设备返回到 STANDBY 状态。

1.1.2.2 状态寄存器保护 1 位

配置寄存器 1 SRP1 位 CR1V[0],锁定传统块保护位 (SR1NV[5:2] & SR1V[5:2])、CMP_NV (CR1NV[6]) 和TBPROT_NV位 (SR1NV[6]) 的状态,就像前几代冻结一样。

在 FS-S 和 FL-S 系列中,Freeze 位还锁定配置寄存器 1 BPNV_O位 (CR1NV[3]) 和安全硅区域 (OTP) 区域的状态。

1.1.2.3 WRR单寄存器写入

在某些传统SPI器件中,只有一个数据字节的写入寄存器(WRR)命令将更新状态寄存器1并清除配置寄存器1中的某些位,包括四模式位。这可能会导致意外退出四方模式。此产品系列仅在提供单个数据字节时更新状态寄存器 1。在这种情况下,配置寄存器 1 不会被修改

1.1.2.4 不支持其他旧命令

• 自动引导相关命令 • 银行地址相关命令 • Hold# 替换为 Reset#

1.1.2.5 新功能

该产品系列为英飞凌SPI类别存储器引入了新功能: • 安全区域密码保护 • IRP 单个区域保护

2 接线图

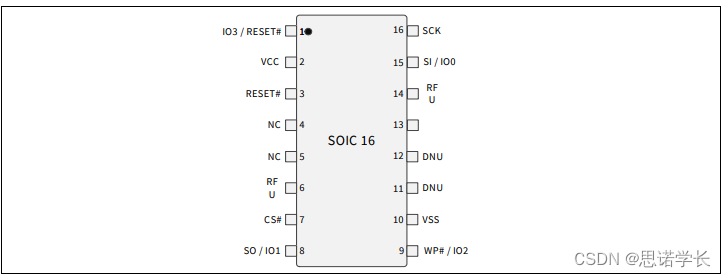

2.1 SOIC 16引脚

图1 16引脚SOIC封装(SO3016),顶视图

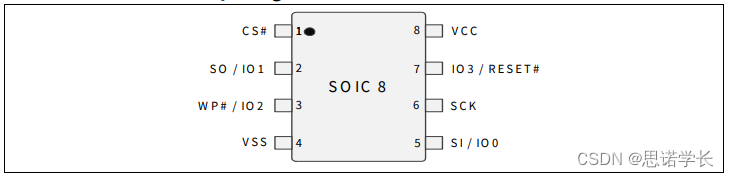

2.2 8- 连接器封装

图2 8引脚塑料小外形封装(SOIC8)

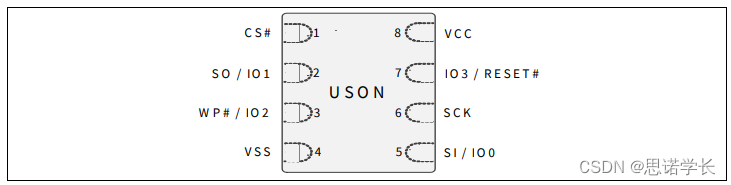

图 3 8 连接器封装 (USON 4 x 4),顶部

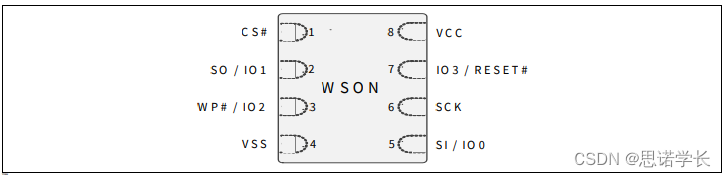

图 4 8 连接器封装 (WSON 5 x 6),顶视图

2.3 BGA球封装

注意事项 2.信号连接与FAC024 BGA的相对位置相同,允许单个PCB封装使用任一封装。3. RESET# 输入具有内部上拉功能,如果未使用四通道模式和硬件复位,则系统中可能未连接。4. 信号连接与FAC024 BGA的相对位置相同,允许单个PCB封装使用任一封装。5. RESET# 输入具有内部上拉功能,如果未使用四通道模式和硬件复位,则系统中可能会保持未连接状态。

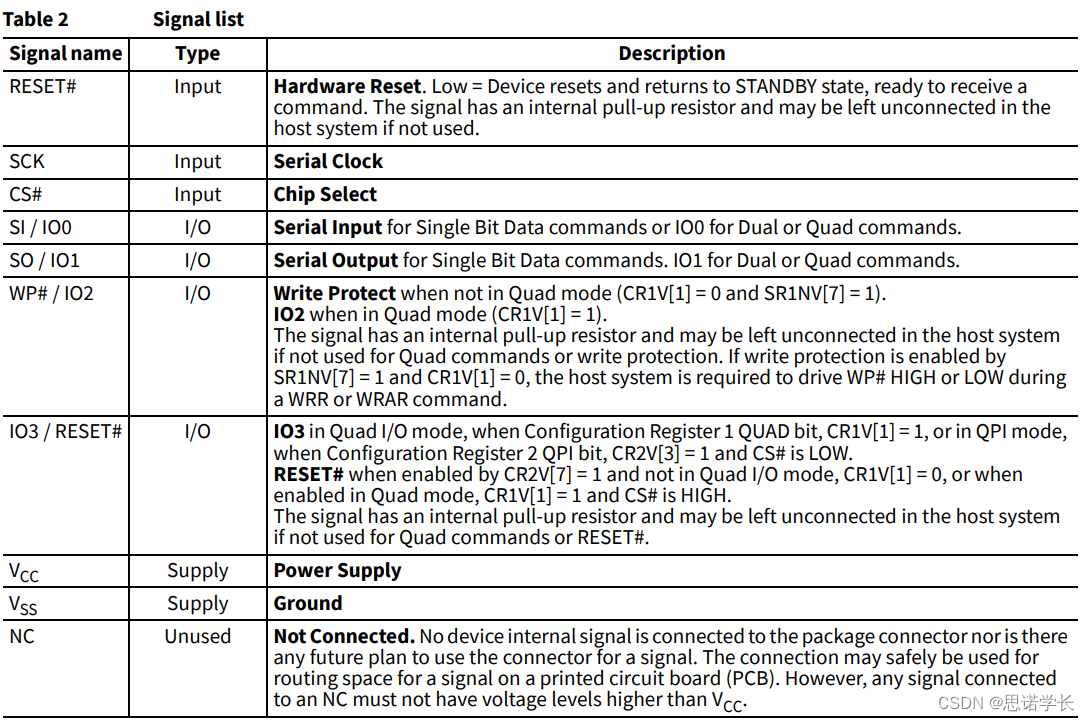

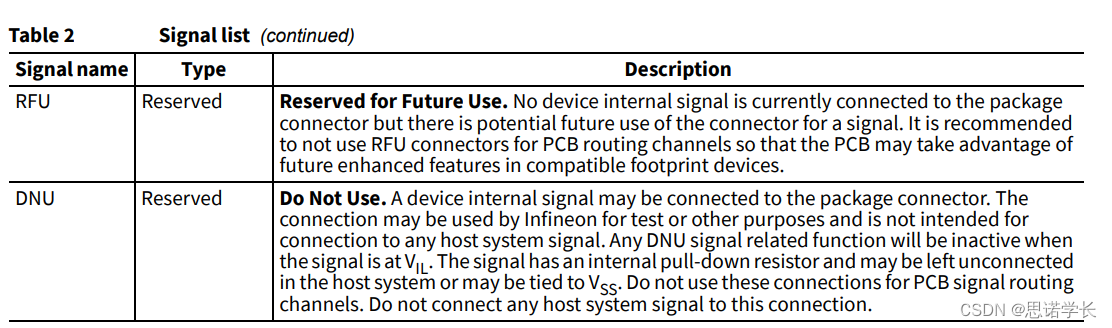

3 信号说明

3.1 具有多输入/输出的串行外设接口 (SPI-MIO)

许多存储设备通过单独的并行控制、地址和数据信号与宿主系统连接,这需要大量的信号连接和更大的封装尺寸。大量的连接增加了功耗,因为如此多的信号需要切换,而较大的封装增加了成本。

S25FL-L系列通过在六个信号线上串行传输所有控制、地址和数据信息,减少了与宿主系统连接所需的信号数量。这降低了存储封装的成本,减少了信号切换的功耗,并且减少了宿主连接数量或为提供其他功能释放了宿主连接器。

S25FL-L系列使用行业标准的单比特SPI,并且还支持可选的扩展命令,用于两比特(双线)和四比特(四线)宽的串行传输。这种多宽度接口称为SPI多I/O或SPI-MIO。

3.2 输入/输出摘要

注意事项:

带有内部上拉或下拉的输入引脚驱动电流小于2微安。仅在上电过程中,电流会在4微秒内增大到150微安。在标准工艺下,当Vcc=3.3V时,上拉或下拉电阻的阻值在-40°C时约为4.5兆欧,而在90°C时约为6.6兆欧。

3.3 多输入/输出(MIO)

传统的SPI单比特宽指令(单线或SIO模式)仅通过串行输入(SI)信号从宿主传输信息至存储器。数据可以通过串行输出(SO)信号串行地发送回宿主。

双线或四线输入/输出(I/O)指令仅通过SI/IO0信号向存储器发送指令。地址或数据作为两比特对通过IO0和IO1,或作为四比特(半字节)组通过IO0、IO1、IO2和IO3从宿主传输至存储器。数据以类似的方式,作为两比特对通过IO0和IO1,或作为四比特(半字节)组通过IO0、IO1、IO2和IO3返回给宿主。

QPI模式通过IO0、IO1、IO2和IO3以四比特(半字节)组的形式传输所有指令、地址和数据从宿主至存储器。数据以类似的方式,作为四比特(半字节)组通过IO0、IO1、IO2和IO3返回给宿主。

简言之,MIO技术通过增加数据线的数量(从单线到双线或四线),使得数据传输的宽度增加,从而提高数据传输的速率。这对于需要快速数据读写的应用来说非常有用,如高速闪存存储器。QPI模式则是在此基础上进一步提高了数据传输效率,通过同时使用四条数据线进行数据传输。

3.4 串行时钟(SCK)

该输入信号为SPI接口提供同步基准。指令、地址或数据输入被锁存在SCK信号的上升沿。在 SDR 命令中,SCK 的下降沿之后的数据输出会发生变化

3.5 芯片选择 (CS#)

芯片选择信号指示命令何时向设备传输信息或从设备传输信息,并且其他信号与存储设备相关。

当CS#信号处于逻辑高电平状态时,不选择器件,忽略所有输入信号,所有输出信号均为高阻抗。设备将处于待机电源模式,除非正在进行内部嵌入式操作。

嵌入式操作由状态寄存器 1 正在进行的写入位 (SR1V[0]) 设置为 1 指示,直到操作完成。

一些嵌入式操作示例包括:编程、擦除或写入寄存器 (WRR) 操作。

将 CS# 输入驱动到逻辑 LOW 状态使设备启用,使其处于有功功率模式。上电后,在开始任何命令之前,都需要 CS# 上的下降沿。

3.6 串行输入 (SI) / IO0

此输入信号用于将数据串行传输到设备中。它接收要编程的指令、地址和数据。这些值被锁存在串行SCK时钟信号的上升沿。

SI 变为 IO0 - 双通道和四通道命令期间的输入和输出,用于接收要编程的指令、地址和数据(锁存在串行 SCK 时钟信号上升沿上的值)以及移出数据(在 SCK 的下降沿,在 SDR 命令中,以及在 SCK 的每个边沿,在 DDR 命令中)

3.7 串行输出 (SO) / IO1

此输出信号用于将数据串行传输出设备。数据在串行SCK时钟信号的下降沿移出。

SO 变为 IO1 - 在双通道和四通道命令期间的输入和输出,用于接收地址和要编程的数据(锁存在串行 SCK 时钟信号上升沿上的值)以及移出数据(在 SDR 命令中位于 SCK 的下降沿,以及在 DDR 命令中位于 SCK 的每个边沿)

3.8 写保护 (WP#) / IO2

当 WP# 被驱动为低电平 (VIL) 时,当状态寄存器 1 (SR1NV[7]) 或 (SR1V[7]) 的状态寄存器保护 0 (SRP0_NV) 或 (SRP0) 位设置为 1 时,无法写入状态寄存器、配置寄存器或 DLR 寄存器。在此情况下,将忽略选择 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的命令,并且不会设置任何错误。

这样可以防止对旧块保护设置进行任何更改。因此,如果在更改状态寄存器、配置寄存器或 DLR 寄存器的命令期间 WP# 为低电平,则内存区域中受传统块保护功能保护的所有数据字节也受到硬件保护,防止数据修改,SRP0_NV设置为 1。同样,安全区域锁位 (LB3-LB0) 也受到编程保护。

当启用四通道模式 (CR1V[1] = 1) 或启用 QPI 模式 (CR2V[3] = 1) 时,WP# 函数不可用。在四通道模式或启用 QPI 模式 (CR2V[3] = 1) 期间,用于输入和输出 WP# 函数的 WP# 功能被替换为接收地址和要编程的数据(值锁存在 SCK 信号的上升沿上)以及移出 SCK 下降沿、SDR 命令和 SCK 每个边沿的数据, 在 DDR 命令中)。

WP# 具有内部上拉阻力;未连接时,WP# 处于 VIH 状态,如果不用于四模式或 QPI 模式或保护,则可能在主机系统中保持未连接状态。

3.9 IO3 / RESET#

IO3 用于四通道模式 (CR1V[1] = 1) 或启用 QPI 模式 (CR2V[3] = 1) 期间的输入和输出,用于接收地址,并对数据进行编程(值锁存在 SCK 信号的上升沿)以及移出数据(在 SCK 的下降沿,在 SDR 命令中, 在 SCK 的每个边缘,在 DDR 命令中)。

当 IO3 / RESET# 功能通过写入配置寄存器 2 易失性或非易失性位 7 (CR2V[7] = 1) 或 (CR2NV[7] = 1) 启用时,IO3 / RESET# 输入也可用于启动硬件复位功能。仅当器件未处于四通道模式 (114,144,444)、CR1V[1] = 0 或 CS# 为高电平时,输入才被视为 RESET#。当使用四通道模式时,CR1V[1] = 1或启用QPI模式(CR2V[3] = 1),并且使用CS# LOW选择设备,IO3 / RESET#仅用作IO3进行信息传输。当 CS# 为 HIGH 时,IO3 / RESET# 不用于信息传输,而是用作复位输入。通过在四通道模式 (114,144,444) 期间对 CS# HIGH 进行复位操作,复位功能在四通道模式 (114,144,444) 期间仍然可用。

当系统进入复位状态时,作为复位过程的一部分,CS# 信号必须被驱动为高电平,IO3 / RESET# 信号被驱动为低电平。当 CS# 变为 HIGH 时,IO3 / RESET# 输入从 IO3 转换为复位输入。当 CS# 保持高电平且 IO3 / RESET# 信号对于 tRP 保持低电平时,将检测到复位条件。如果不打算复位,则系统需要主动将 IO3 / RESET# 驱动到 HIGH,同时在将数据传输到内存结束时将 CS# 驱动为 HIGH。将数据传输到主机系统后,内存将在 tCS 期间将 IO3 驱动为高电平。这将确保 IO3 / RESET# 不会浮动或被内部或外部被动上拉缓慢拉高。因此,在 tRP 结束之前,IO3 / RESET# 未被识别为高电平不会触发意外复位。

当 (CR2V[7] = 0) 时,IO3 / RESET# 输入复位功能被禁用。

IO3 / RESET# 输入具有一个内部上拉电阻器,如果不用于四通道模式或复位功能,则主机系统中可能未连接。在主机系统主动将信号驱动为高电平,然后停止驱动信号后,内部上拉将保持IO3 / RESET# HIGH。请注意,如果多个 SPI-MIO 存储器中的任何一个在四通道 I/O 模式下运行,则 IO3 / RESET# 输入不能由多个 SPI-MIO 存储器共享,因为 IO3 被驱动到一个选定存储器或从一个选定存储器驱动,可能看起来像是共享相同 IO3 / RESET# 信号的第二个非选定存储器的复位信号

3.10 RESET

RESET# 输入提供了一种硬件方式,用于将设备重置到待机状态,准备接收命令。当RESET# 被拉低到逻辑低电平(VIL)并至少保持一段时间tRP时,设备开始硬件复位流程。

RESET# 触发的初始化过程与电源上电时执行的初始化过程相同,需要一定的上电时间tPU。RESET# 可以在任何时候被拉低到低电平。为了确保数据完整性,任何被硬件复位中断的操作都应该在设备准备好接受命令序列后重新启动。

RESET# 内置了上拉电阻,如果在宿主系统中不使用,可以不连接。内部上拉会在宿主系统主动将信号拉高后停止驱动该信号时,保持RESET# 高电平。

并非所有封装选项都提供RESET# 输入。当RESET# 输入不可用时,设备的RESET# 输入会被固定在非激活状态。

3.11 电压供应 (VCC)

VCC 是所有器件内部逻辑的电压源。它是用于所有器件内部功能(包括读取、编程和擦除)的单电压

3.12 电源和信号接地 (VSS)

VSS 是器件内核、输入信号接收器和输出驱动器的通用电压漏极和接地基准电压源

3.13 未连接 (NC)

没有设备内部信号连接到封装连接器,也没有任何未来计划将连接器用于信号。该连接可以安全地用于印刷电路板 (PCB) 上信号的路由空间。

3.14 保留供将来使用 (RFU)

封装连接器当前没有设备内部信号连接到封装连接器,但连接器将来可能会使用。建议不要将 RFU 连接器用于 PCB 布线通道,以便 PCB 可以利用兼容封装设备中未来的增强功能。

3.15 请勿使用 (DNU)

设备内部信号可以连接到封装连接器。英飞凌可将该连接用于测试或其他目的,不用于连接到任何主机系统信号。当信号处于 VIL 时,任何与 DNU 信号相关的功能都将处于非活动状态。该信号具有一个内部下拉电阻器,可以在主机系统中保持未连接状态,也可以连接到 VSS。请勿将这些连接用于 PCB 信号路由通道。请勿将任何主机系统信号连接到这些连接

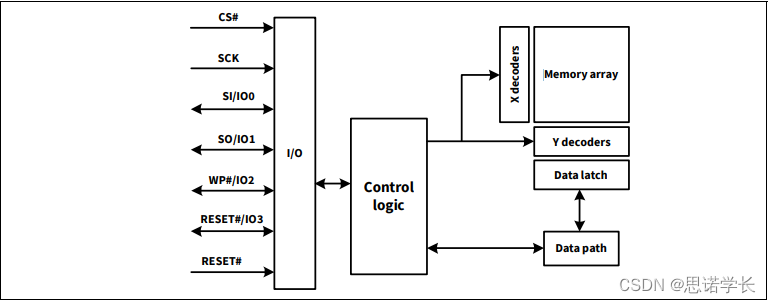

4 框图

4.1 系统框图

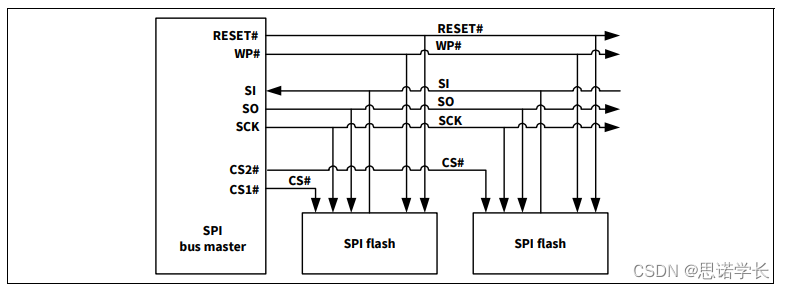

图7 SPI总线上的总线主控器件和存储器件 - 单位数据路径

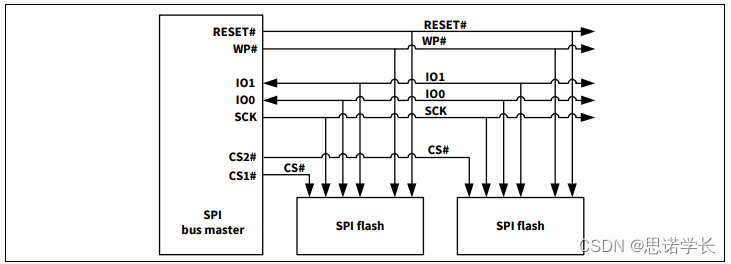

图8 SPI总线上的总线主控器件和存储器件 - 双位数据路径

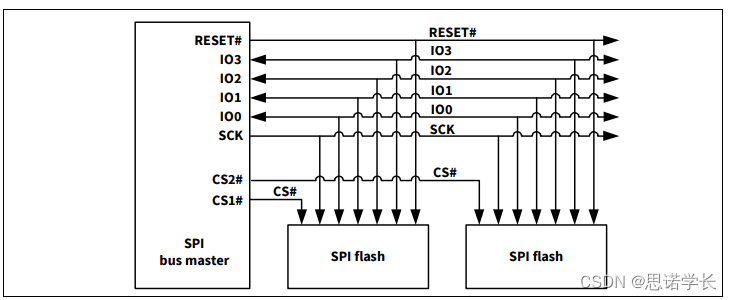

图 9 SPI 总线上的总线主控器件和存储器件 - 四位数据路径 - 单独的 RESET#

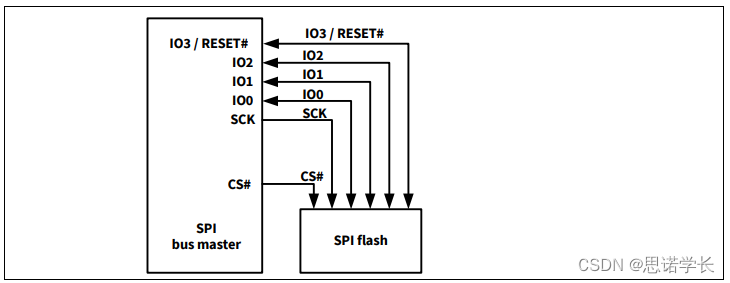

图10 SPI总线上的总线主控器件和存储器件 - 四位数据路径 - I/O3 / RESET#

5 信号协议

5.1 SPI 时钟模式SPI clock modes

5.1.1 单数据速率 (SDR)

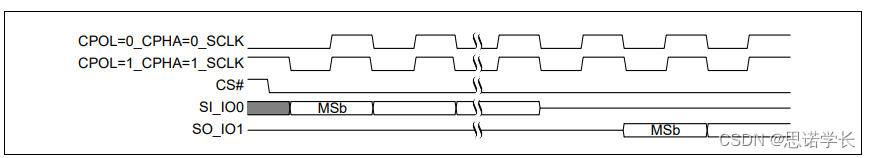

FL-L系列可由嵌入式微控制器(总线主控bus master)驱动,采用以下两种时钟模式之一。

• 模式 0,时钟极性polarity (CPOL) = 0,时钟相位phase (CPHA) = 0

• 模式 3,CPOL = 1,CPHA = 1

对于这两种模式,输入器件的数据始终锁存在 SCK 信号的上升沿,输出数据始终可从 SCK 时钟信号的下降沿获得。两种模式的区别在于总线主站处于待机Standby模式且不传输任何数据时的时钟极性。

• SCK 将保持在逻辑低电平状态,CPOL = 0,CPHA = 0

• SCK 将保持在逻辑高电平状态,CPOL = 1,CPHA = 1

图 11 支持的 SPI SDR 模式

文档其余部分的时序图通常同时显示为模式 0 和 3,方法是在 CS# 下降时将 SCK 同时显示为 HIGH 和 LOW。

在某些情况下,时序图可能仅显示 CS# 下降时 SCK 为低电平的模式 0。在这种情况下,模式 3 时序仅意味着 CS# 下降时时钟为高电平,因此模式 3 不需要设置 SCK 上升沿或保持 CS# 下降沿的时间。

SCK循环是从SCK的一个下降沿到SCK的下一个下降沿的测量(计数)。在模式 0 中,命令中第一个 SCK 周期的开始是从 CS# 的下降沿到 SCK 的第一个下降沿测量的,因为 SCK 在命令开始时已经是低电平

如何理解这段话

这段话描述了FL-L系列芯片的单数据速率(SDR)操作模式,具体是指该芯片与嵌入式微控制器(总线主控设备)之间的时钟信号配合方式。以下是对这段话的详细解释:

### 两种时钟模式

FL-L系列芯片可以在两种时钟模式下工作:

1. 模式0:时钟极性(CPOL)= 0,时钟相位(CPHA)= 0

2. 模式3:时钟极性(CPOL)= 1,时钟相位(CPHA)= 1

### 时钟信号特性

输入数据:设备(即FL-L芯片)在SCK(串行时钟)信号的上升沿(从低到高的跳变)时接收数据。

输出数据:设备在SCK信号的下降沿(从高到低的跳变)时输出数据。

### 模式之间的区别

两种模式的主要区别在于总线主控设备处于待机模式(不传输数据)时的时钟极性:

模式0(CPOL=0,CPHA=0):在待机模式下,SCK时钟信号保持在低电平(逻辑低状态)。

模式3(CPOL=1,CPHA=1):在待机模式下,SCK时钟信号保持在高电平(逻辑高状态)。

总结

在模式0下,总线待机时,SCK为低电平。

在模式3下,总线待机时,SCK为高电平。

在两种模式中,数据的输入都是在SCK的上升沿被设备锁存,数据的输出都是在SCK的下降沿可用。

这种设计的目的是为了确保数据传输的同步性和可靠性,通过调整CPOL和CPHA的值,用户可以选择适合其系统需求的时钟模式。

理解这段话中的“输入数据”和“输出数据”与时钟信号(SCK)之间的关系,可以通过以下几点来解释:

输入数据和输出数据的定义

输入数据:指的是总线主控设备(例如微控制器)发送到FL-L系列芯片的数据。

输出数据:指的是FL-L系列芯片发送回总线主控设备的数据。

时钟信号的作用

SCK(串行时钟)信号用于同步数据的传输。时钟信号的上升沿和下降沿决定了何时传输和接收数据。

### 具体时序

1. **输入数据(从微控制器到FL-L芯片)**:

- 数据是在SCK信号的上升沿(从低到高的变化)被FL-L芯片接收和锁存的。

- 这意味着当SCK从低电平变为高电平时,微控制器发送的数据会被FL-L芯片读取。

2. **输出数据(从FL-L芯片到微控制器)**:

- 数据是在SCK信号的下降沿(从高到低的变化)由FL-L芯片发送的。

- 这意味着当SCK从高电平变为低电平时,FL-L芯片准备并发送数据,微控制器可以在这个时候读取数据。

### 时钟模式和待机状态

两种时钟模式的主要区别在于待机状态时SCK信号的电平:

- **模式0**(CPOL=

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?