https://www.cnblogs.com/oneMr/p/11496450.html

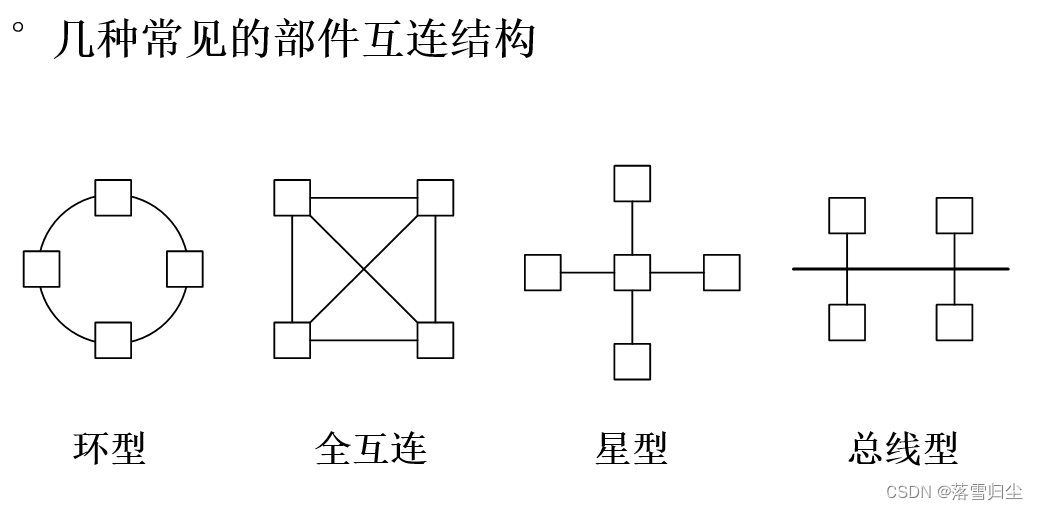

互联结构

关于为什么是C盘?

最开始没有硬盘,只有软盘(A、B).

总线的基本概念

°总线(BUS)是一组信号线,用于将两个或两个以上部件连接起来,形成部件之间的公共通信通路,每个部件将自己的信号线与总线相连。

总线是计算机系统中各系统功能部件之间传输数据和控制信号的公共传输通道\通道\传输通道。

特点

总线具有以下两个最主要的特点:

C.减少了信息传输线的条数

总线的一次信息传送一般分为请求总线、总线仲裁、寻址(目的地址)、信息传送、状态返回(或错误报告)共5个阶段。

互连方式

划分

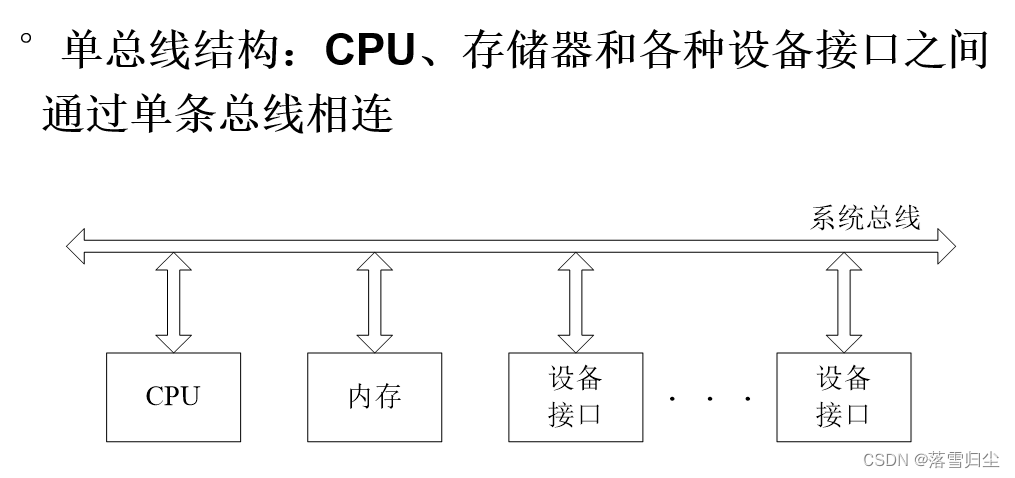

常见的总线结构有三种,即单总线结构、双总线结构和三总线结构。

根据总线的功能划分

°地址总线:地址总线上传送的是由CPU等主设备发往从设备的地址信号。当CPU对存储器或I/O接口进行读写时,必须首先给出所要访问的存储器单元的地址或I/O端口的地址,并在整个读写周期一直保持有效。 单向的。

°数据总线:数据总线上传送的是各部件之间交换的数据信息。数据总线通常是双向的,即数据可以是由从设备发往主设备(称为读或输入),也可以是由主设备发往从设备(称为写或输出)。

°控制总线:控制总线上传送的是一个部件对另一个部件的控制或状态信号,如CPU对存储器的读、写控制信号,外部设备向CPU发出的中断请求信号等。

°另外,总线也提供电源线和接地线等。

地址总线专门用来传送地址信息,指定数据总线上数据的来源和去向。

按所连接的不同部件或设备划分

°系统总线 :用于将CPU、存储器和输入输出接口及I/O通道连接起来的一组信号线就称为系统总线。

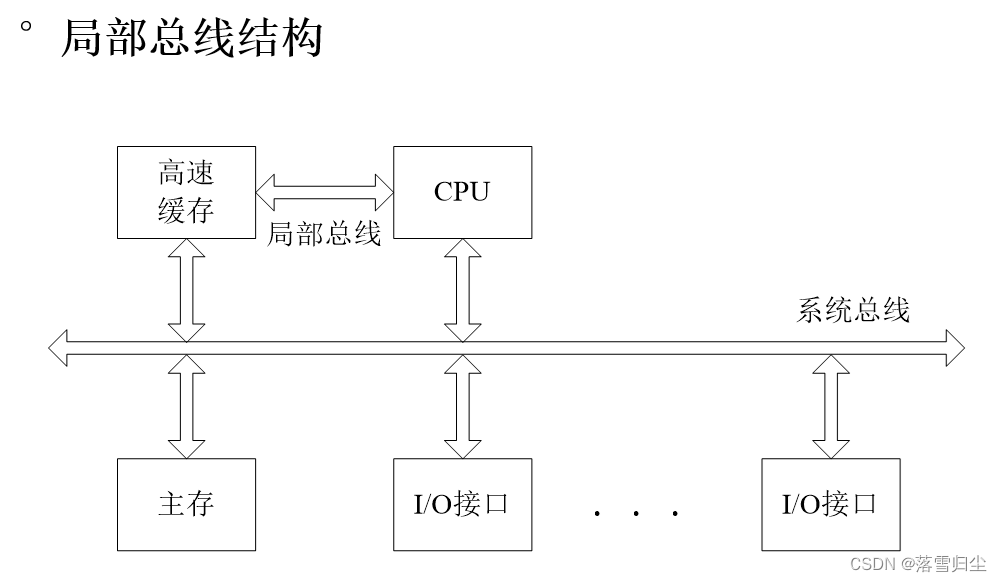

°局部总线 :随着计算机对CPU访存速度和图像处理速度的要求越来越高,现代机器往往采用多总线结构设计,即将CPU与存储器及显示器适配器相连接的信号线从系统总线中分离出来,形成CPU与存储器和CPU与显示器适配器之间的专用总线,称为局部总线。

°外部总线 :外部总线主要是指计算机与计算机、计算机与外部设备之间的通信总线。

在系统总线上的信号有数据信号、控制信号、地址信号。

系统总线是用于连接CPU、存储器和I/O设备。

系统总线中地址线的功能是用于指定主存和I/O端口的地址\用于传送选择主存单元和I/O接口的地址。

系统总线中控制线的功能是供主存、I/O接口设备的控制信号和响应信号。

系统总线中地址线的功能是选择进行信息传输的设备。(×)

日常所说的总线指系统总线。

按相对于CPU或其它芯片的位置

总线可以分为片内总线和片外总线两大类。

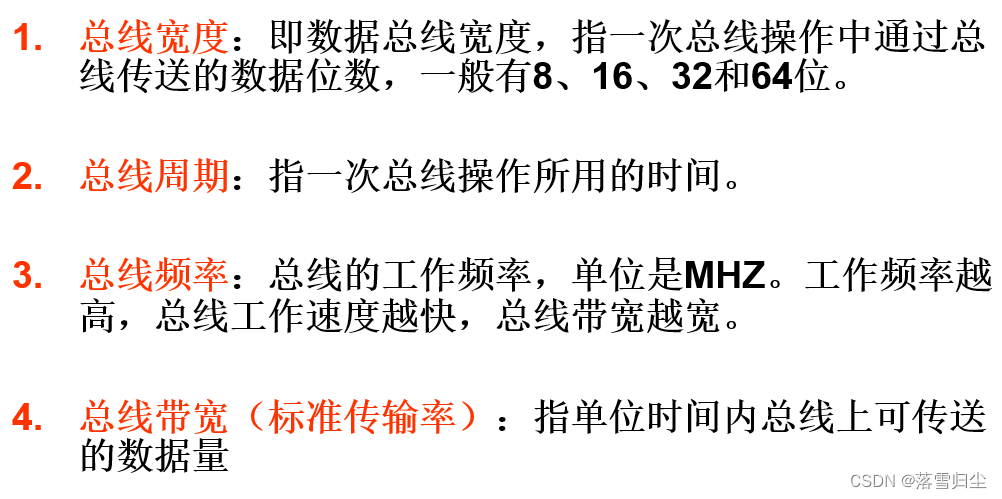

总线的性能指标

总线互联

计算机的工作过程就是CPU不停地取指令存指令的过程。对于速度要求比较高,但不能占用总线(独占性);CPU跟IO是随机的,但CPU跟cache是每时每刻的。所以单独拉根线。

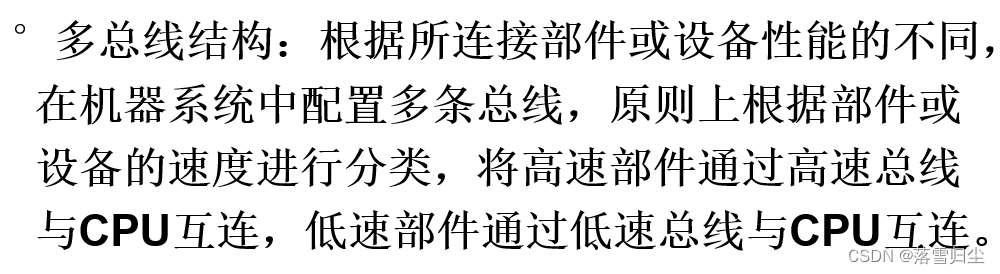

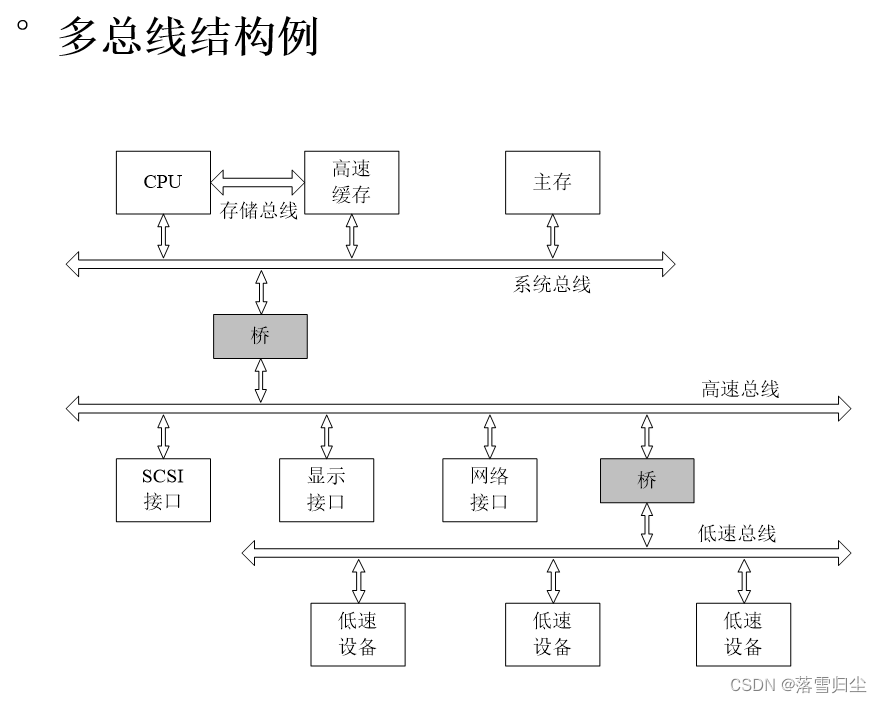

CPU在通过存储总线拿数据。如果没有,则在主存中取。(IO离散的)按速度分类。

在单机系统中,单总线结构总线结构的访问外设与访问主存单元一样。

在单总线的微型计算机系统中,外设可和主存储器单元统一编址,因此可以不使用I/O指令。

从总线利用率看,三总线系统的效率最低。

总线的控制方式

总线的仲裁

°按照总线仲裁电路的位置不同,仲裁方式分为集中式仲裁和分布式仲裁两种。

°总线仲裁的目的是为了指定计算机中的某个设备为主设备,然后由它启动从设备。

°通过总线仲裁实现对总线的占用。

集中式仲裁

链式查询方式

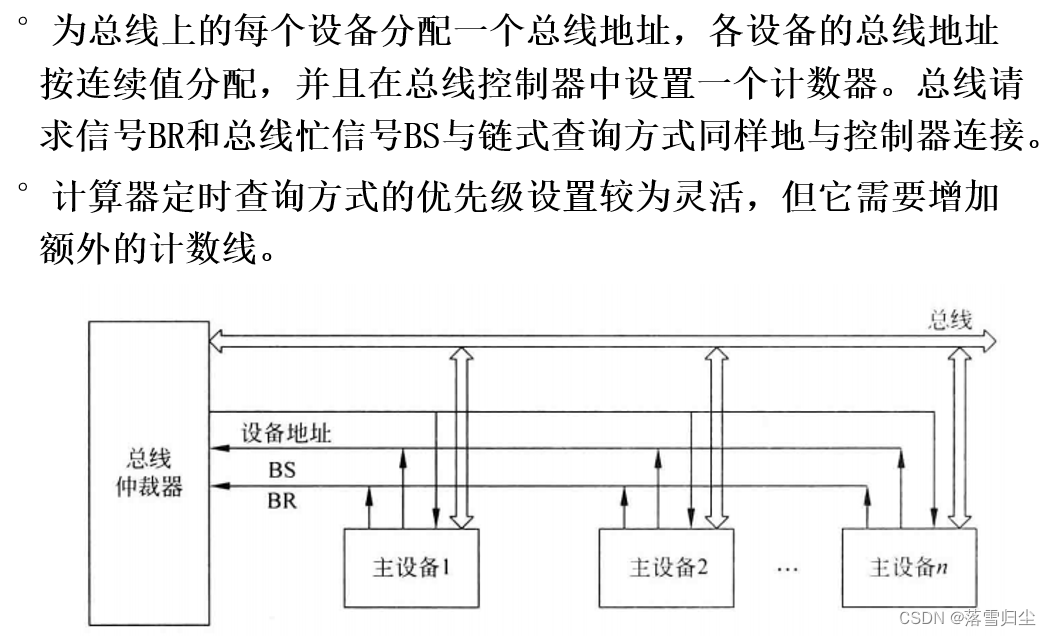

计数器定时查询方式

时序电路且一共需要+2个控制线(假设有N个设备,计数器的位数等于

)。与链式查询方式对比,多了一组设备地址线,少了BG线,

CPU通过地址去寻找设备。计数器对应哪个值时,哪个值才可以发送数据。

比较公平,谁都有机会发送数据(优先级方式比较灵活)

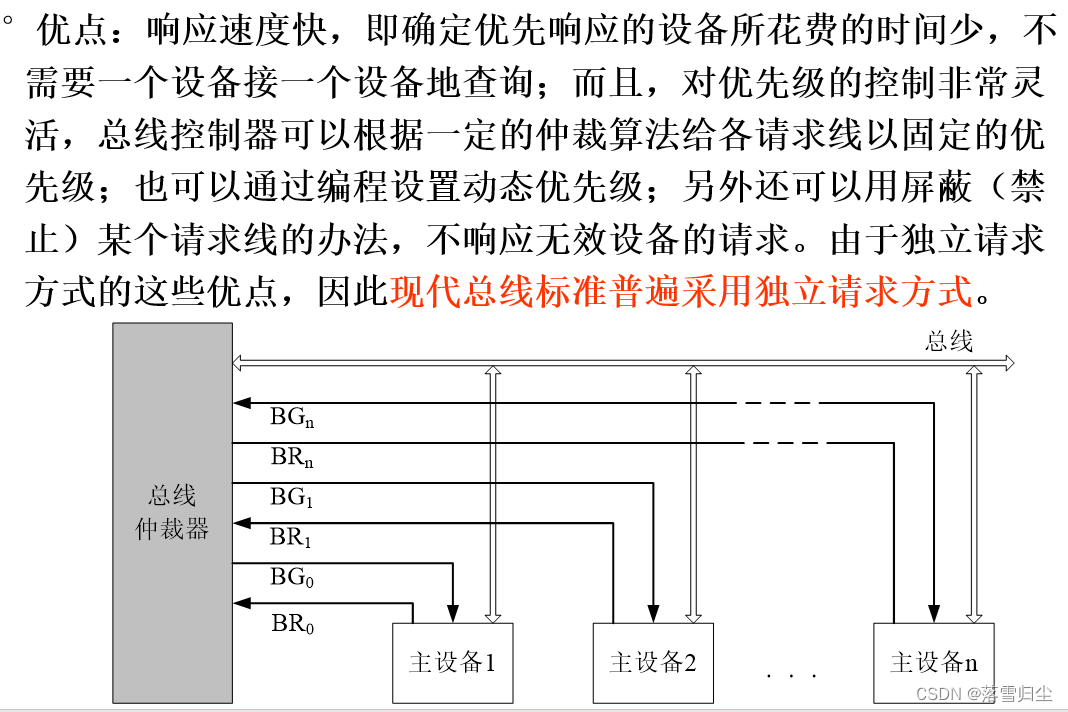

但上述两种方式无法屏蔽某一个设备的请求,只有独立请求方式可以。

场景:如果设备坏了,BR被不停地发(会影响其他设备地执行),这时就需要把它的需求给屏蔽掉或者判断出打印机坏了(?)

独立请求方式

分布式仲裁

总线的定时

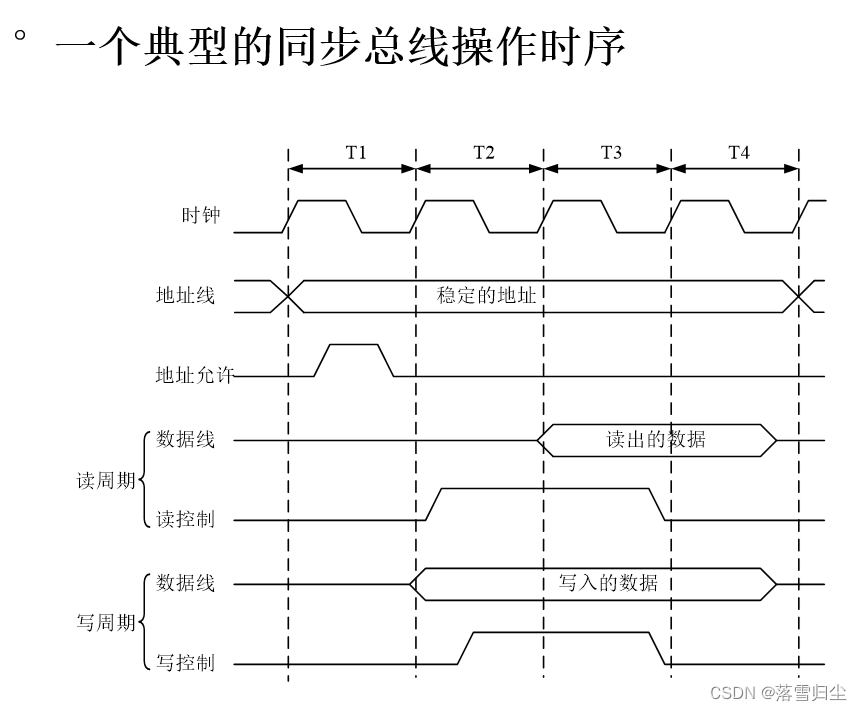

回顾:CPU读程序要先给什么信号?

先给片选信号,再给地址信号,再给读信号。(写入尽在最后一步变成写信号)具有时序性,三步不是同时进行的。

同步时序

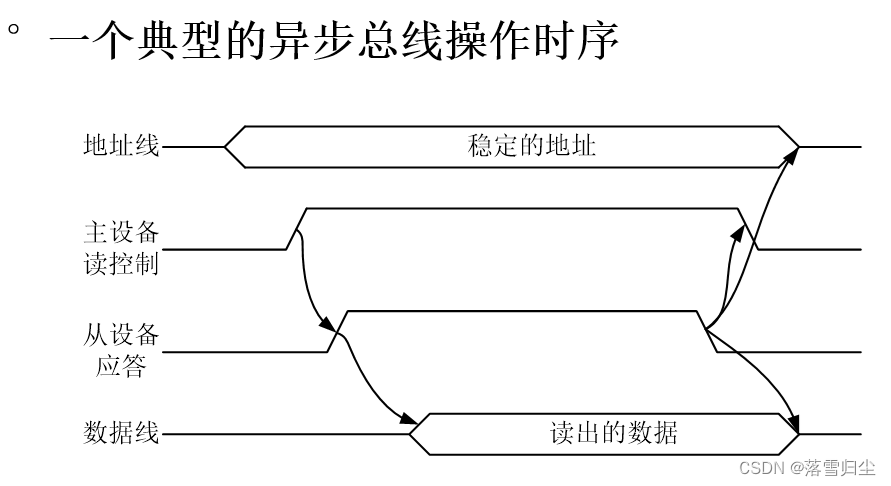

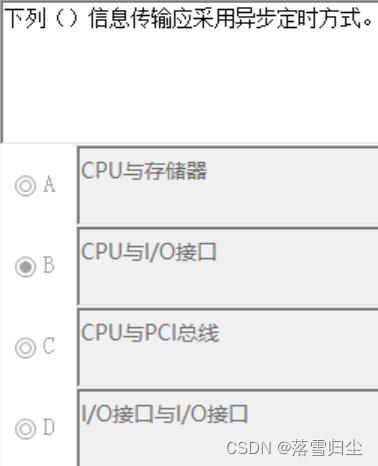

异步时序

总线标准及举例

系统总线

ISA

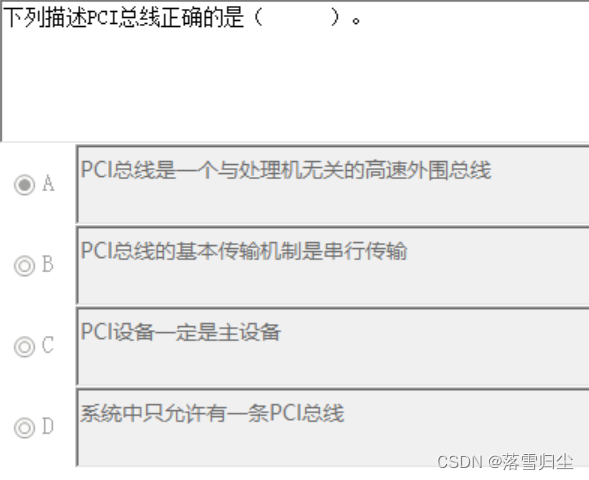

PCI

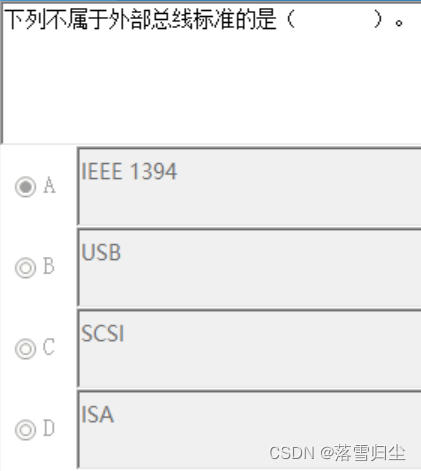

外部总线

D.ISA 最早出现的微型计算机的系统总线

B.PCI总线的基本传输机制是串行传输

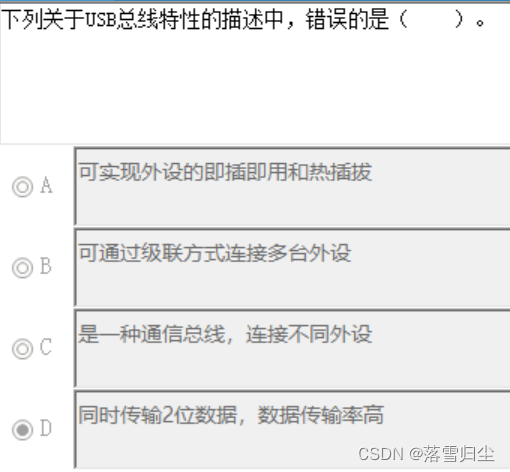

D.同时传输2位数据,数据传输率高

下列关于USB 总线特性的描述中,错误的是( )。__牛客网

B

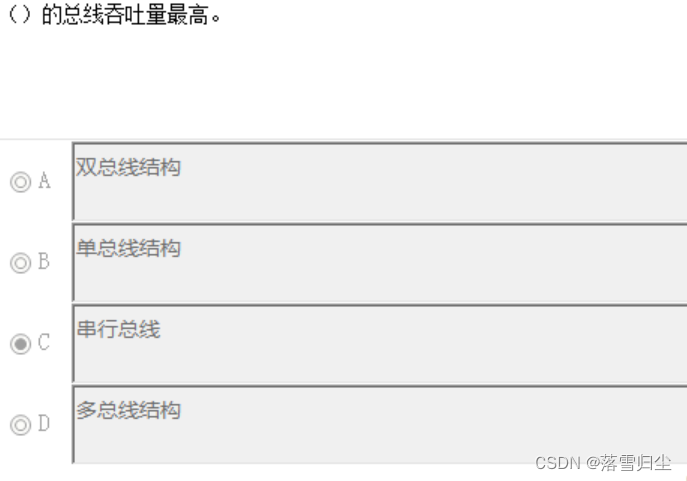

吞吐量:在单位时间内通过某个网络(信道/接口)的数据量。

也就是说,是指单位时间内总线完成的请求量,跟传输量是不一样的概念。单总线因为只有一条总线去传输数据,所以总线非常繁忙,因此单位时间内总线处理的请求非常多,吞吐率就最高了。

PCI总线的基本传输机制是猝发式传输

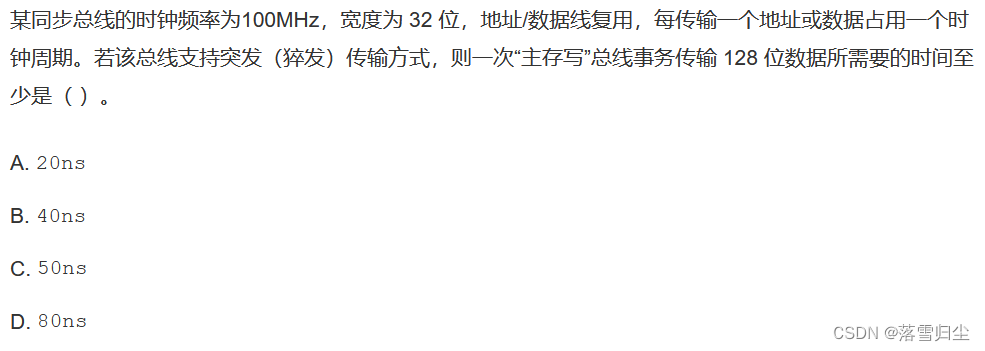

某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传送一次地址或数据占用一个时钟周期。如该总线支持突发(猝发)传输方式,则一次"主存写"总线事物传输128位数据所需要的时间至少是( 50ns )。

- 时钟频率为100MHz,则时钟周期为1/100MHz=10ns

- 传输128位数据需要128/32=4个时钟周期

- 接受“主存写”这一命令还需要1个时钟周期

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?