一.引言

E D A技术在当今社会为现代电子设计领域提供了可能性,这也是E D A 技术飞速发展的理由。现如今,E D A技术不再是某一门课程的分支,也不是某种新的技术,而是一门综合性学科。让计算机软件与计算机硬件相结合,他代表了电子设计技术的不断发展方向。

在当今社会EDA技术为现代电子设计领域提供了可能性,这也是E D A 技术飞速发展的理由。现如今,E D A技术不再是某一门课程的分支,也不是某种新的技术,而是一门综合性学科。通过计算机软件与计算机硬件相结合,代表了电子设计技术的不断发展方向。

数字钟的应用十分的广泛,每一个家庭,车站,教室等公共场所都应该会有数字钟的身影,给人们带来极大的方便和快捷。

随着科技的进步和人们生活水平的提高,我们对于时钟的要求也在不断的提高。现在时钟已经不再是一个简单的报时工具,在很多特殊的时刻我们还需要用到时钟的其他功能。在这种新形势下,制作数字电子钟成为时代的主流设计和发展方向。数字钟是利用数字电路实现时、分、秒的计时装备,较以往的机械钟具有更强的直观性和准确性,并且延长了时钟的使用寿命。

二.设计目的

12进制数字钟的计时装置的周期是12小时,显示满刻度为11小时59分59秒。

制作数字钟是为了了解数字钟的工作原理和工作过程,能够自主独立的编写和修改各种进制数字钟的语言。熟练使用EDA课程中使用的软件和将所学到的知识理论应用于实践中。并能因为此次实验对EDA程序设计产生浓厚兴趣,因为只有真正喜欢上这门课程,才能在未来的学习中不断进步。

三.实验内容

利用M A X+p l u s II 10.2软件设计12进制数字钟。

四.实验原理和思路

由于我设计的是12进制数字钟,所以在设计过程中我让数字钟在“时”上从0-11循环,在“分”和“秒”上依旧实现0-59的循环。

在《EDA技术与应用》这篇课本p205页中我们可以见到60进制的计数器,我设计的12进制数字钟原理其实和60进制计数器是一样的,不同之处只是12进制是十位在0时,个位实现0-9的循环,十位等于1时,个位实现0-1的循环。

五.数字钟模块设计

5.1“时”程序段设计

过程如下:

1.打开M A X+p l u sⅡ10.2,新建 Text Editor file

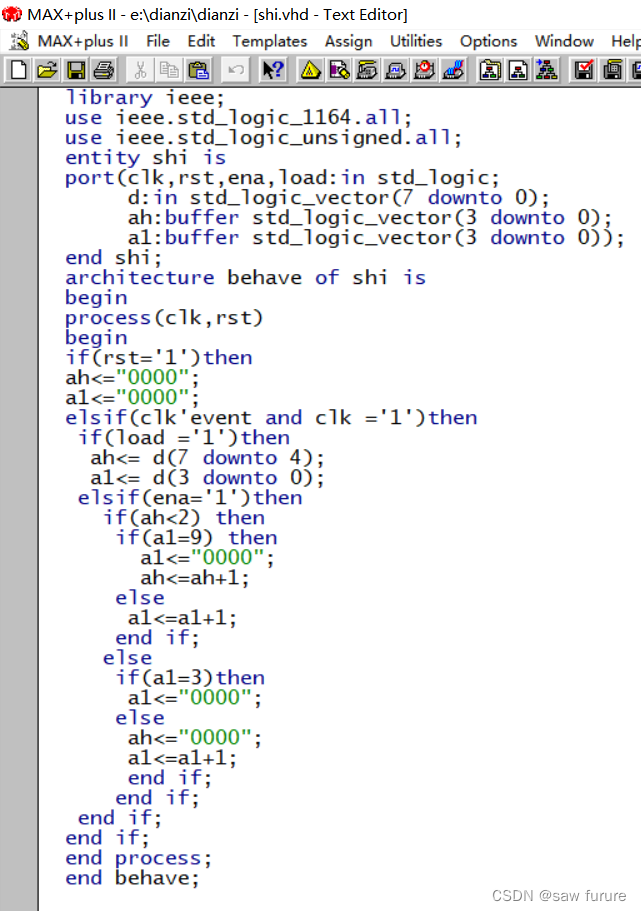

2.编写程序如图:

3.点击 ctrl + shift + j 将设计项目设置成工程文件,注意类型为.vhd。

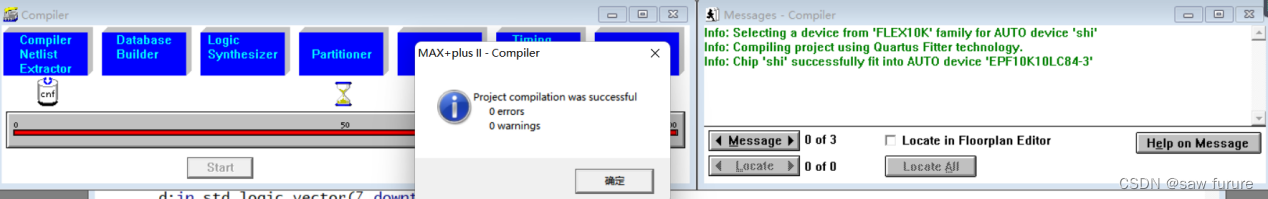

4.点击M A X + p l u s Ⅱ下的compiler进行编译

library ieee;

use ieee.std_logic_1164.all

本文介绍了使用EDA技术设计12进制数字钟的实验过程,包括设计目的、实验内容、原理和思路。通过MAX+PLUS II 10.2软件,分别设计了“时”、“分”、“秒”的计数器和七段显示译码器,最终通过静态译码方式实现数码管显示。实验中发现静态显示存在的问题和改进方案,如采用动态显示以节省资源并提高显示效果,以及增加自动校时模块减少计数误差。通过本次实验,作者不仅提升了EDA技能,还体验到解决问题和自我学习的重要性。

本文介绍了使用EDA技术设计12进制数字钟的实验过程,包括设计目的、实验内容、原理和思路。通过MAX+PLUS II 10.2软件,分别设计了“时”、“分”、“秒”的计数器和七段显示译码器,最终通过静态译码方式实现数码管显示。实验中发现静态显示存在的问题和改进方案,如采用动态显示以节省资源并提高显示效果,以及增加自动校时模块减少计数误差。通过本次实验,作者不仅提升了EDA技能,还体验到解决问题和自我学习的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6226

6226

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?