数制与编码

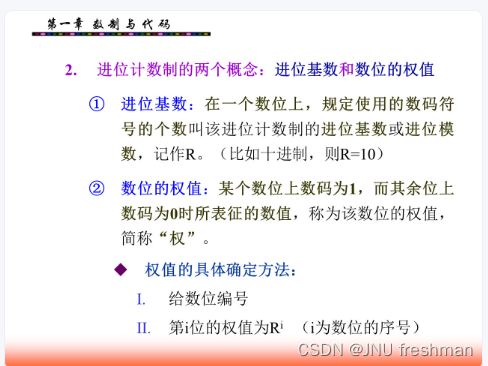

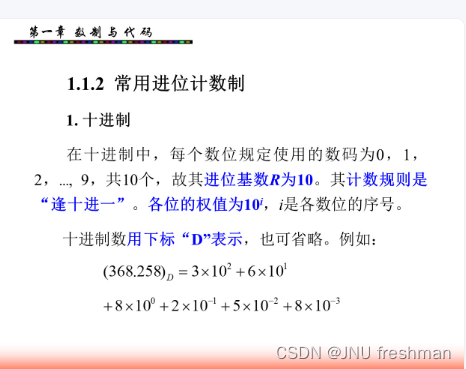

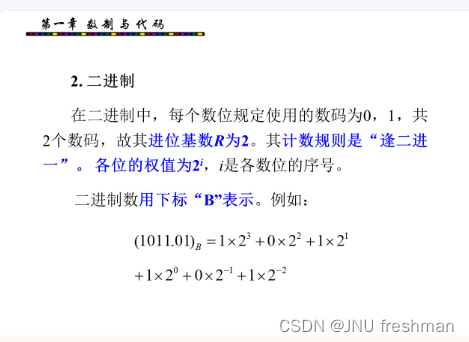

进位计数制

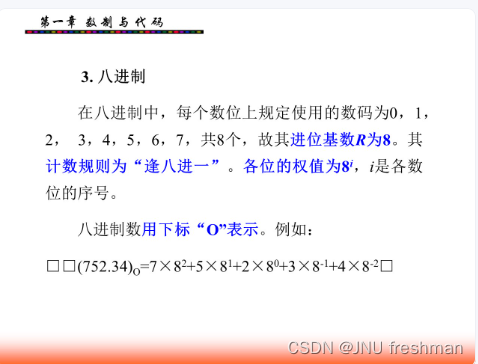

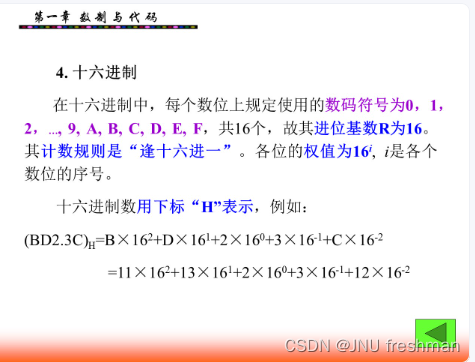

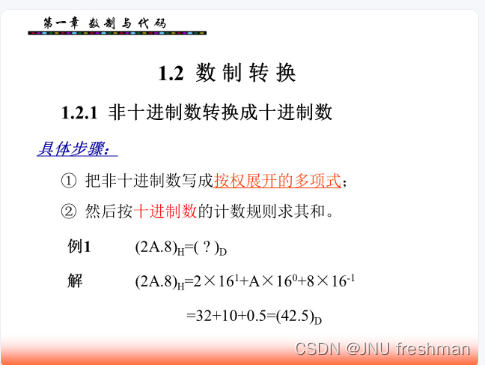

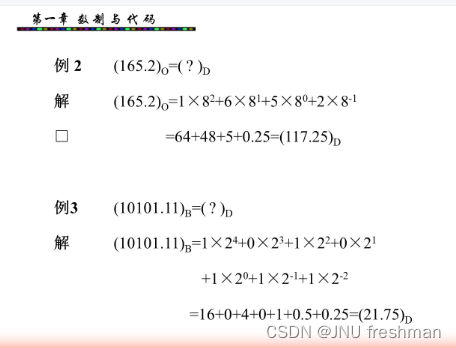

数制转化

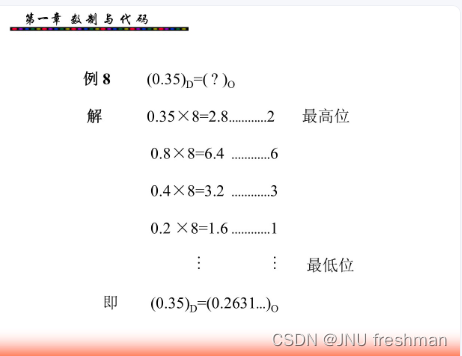

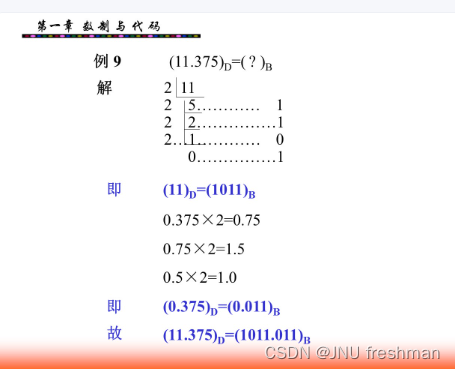

十进制与非十进制之间的转化

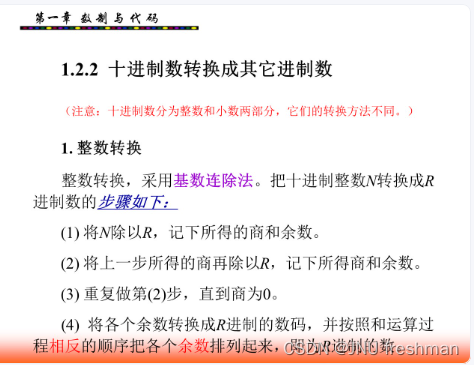

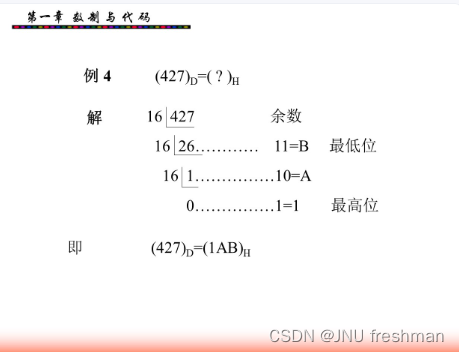

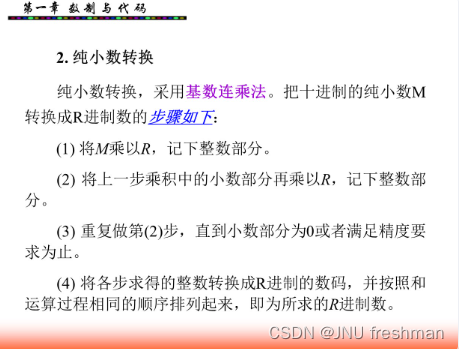

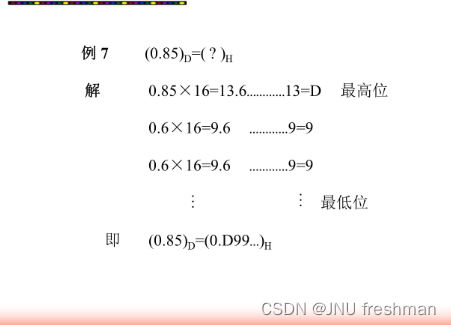

小结:其他的进制转化为十进制是很简单的就是按照权值逐一展开后相加,对于十进制转化为其他进制,对于十进制的整数部分,采用类似于辗转相乘,每次将余数留作结果,商继续运算;对于小数部分的转化就是用乘法运算,每次都用小数部分乘相对应的进制,整数部分作为结果,小数部分继续运算十进制转化:整数部分开始得到的数字是低位的,小数部分的转化,开始得到的部分是高位的,一句话,开始得到的就是靠近小数点的

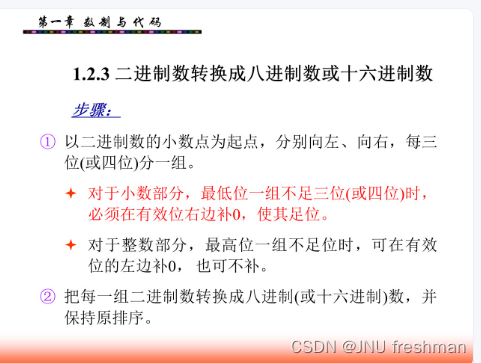

二进制转化为八进制和十六进制

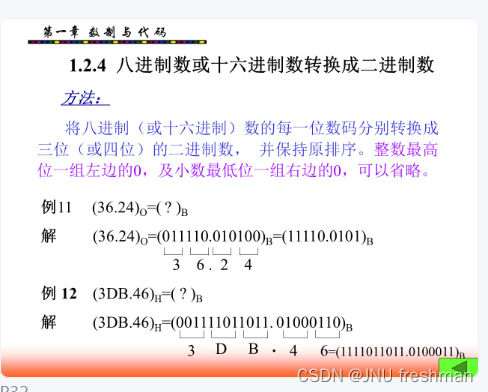

八进制或者十六进制转化为二进制

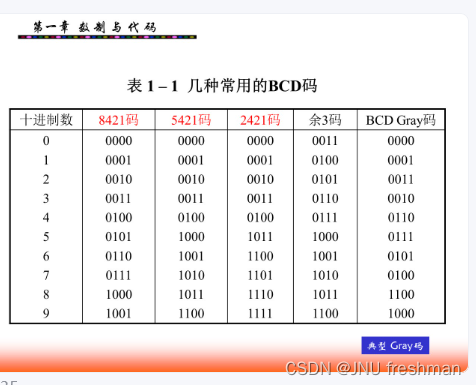

常用代码

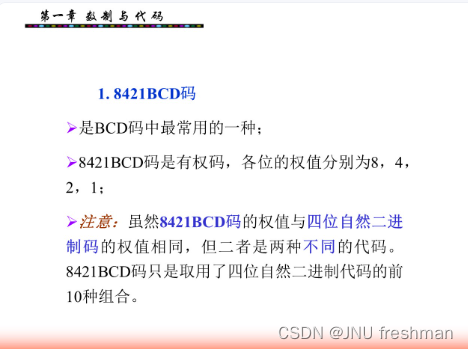

8421BCD 编码

余3码

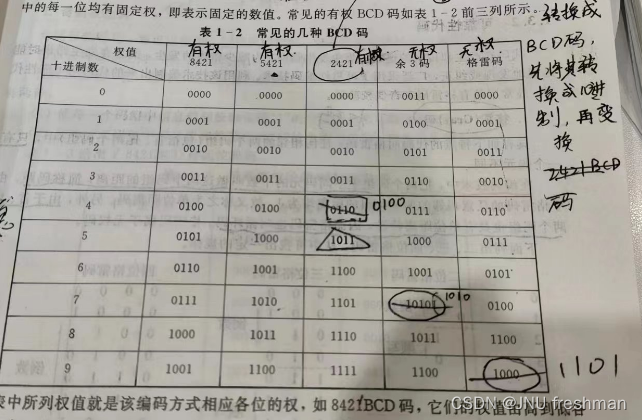

2421BCD 编码

汇总

特别注意2421 的 5 是 1011 ,4 是 0100 ,两个刚好互补,这样可以方便记忆,对于 5421码,的5是1000,启动高位嘛

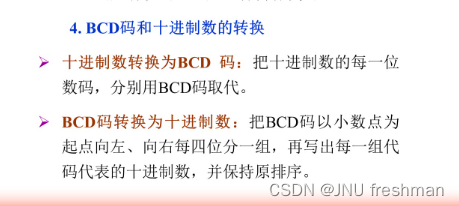

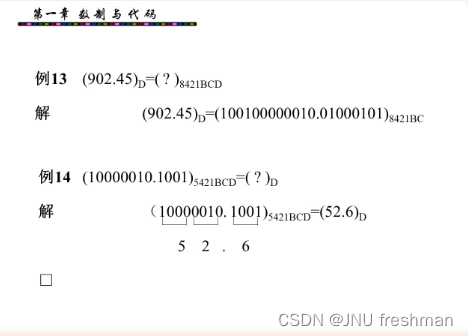

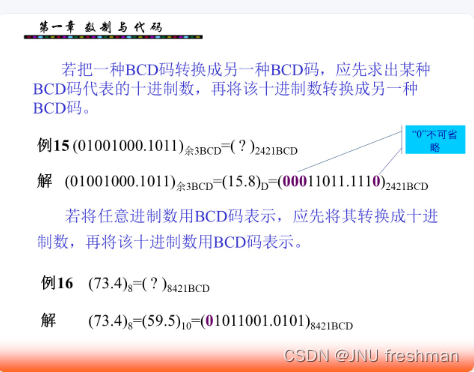

BCD 码与十进制码的转换

那么其他类似二进制,八进制,十六进制与BCD 码的转换,都要先转化为十进制,以十进制为中转站

BCD 码之间的转化

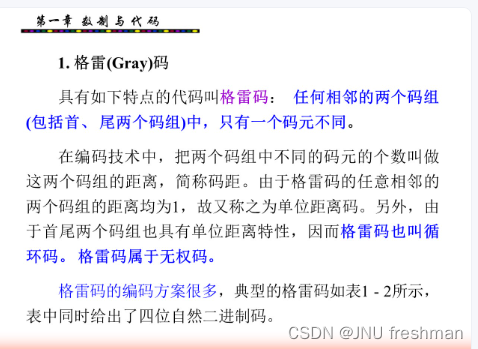

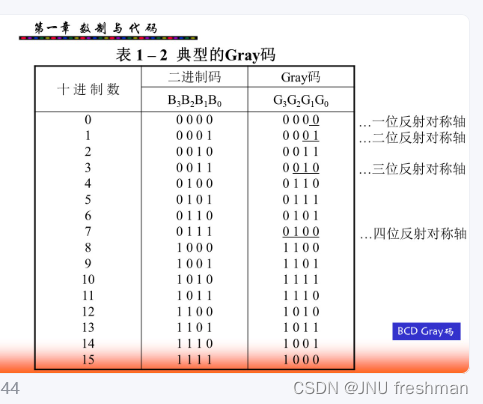

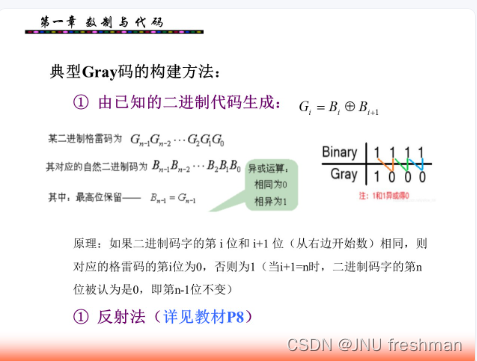

可靠性代码与格雷码

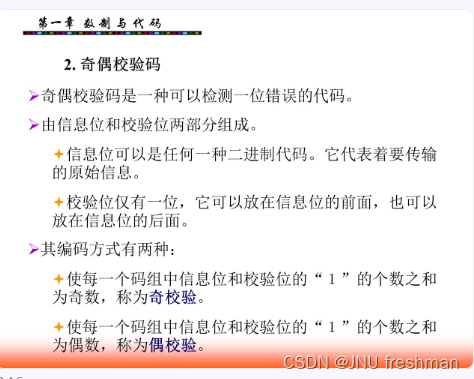

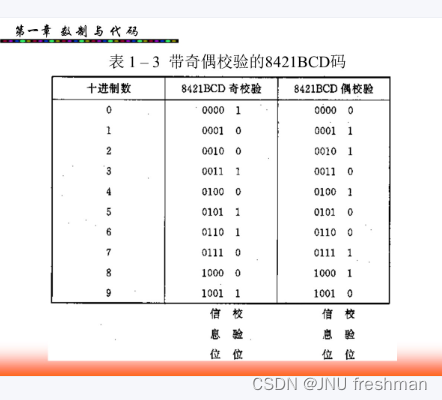

校验码

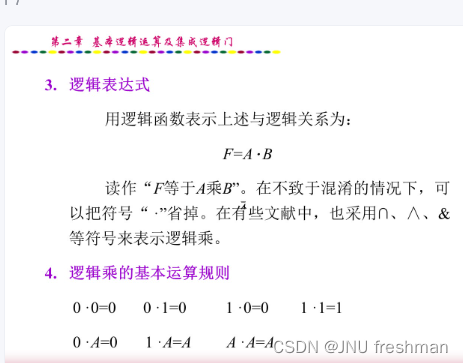

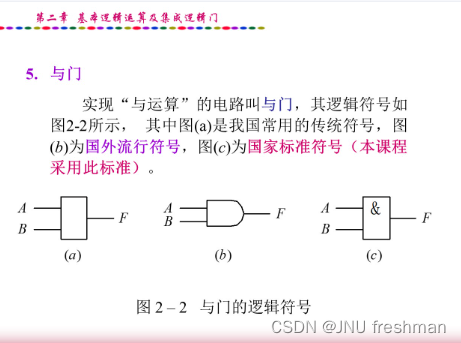

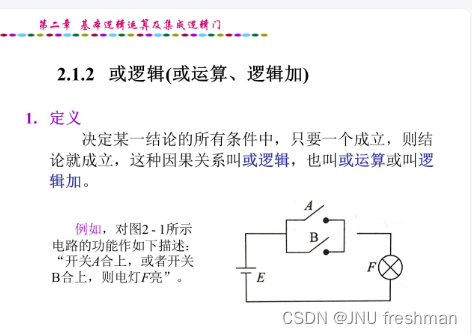

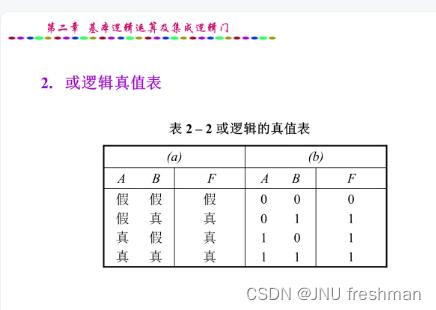

基本逻辑运算以及集成逻辑门

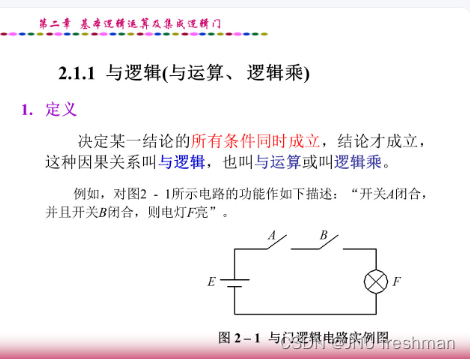

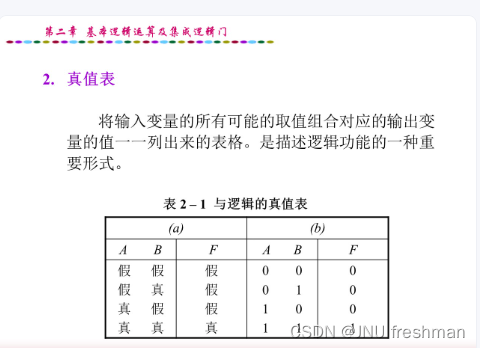

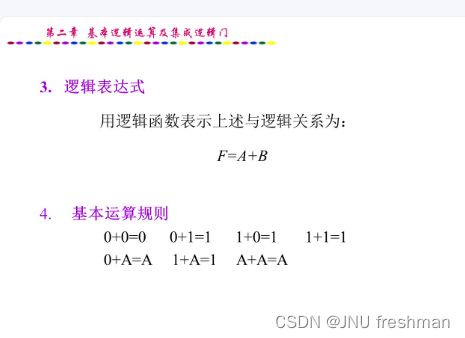

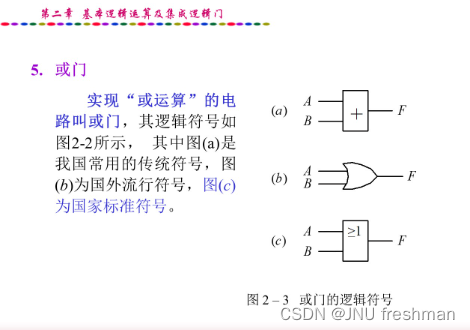

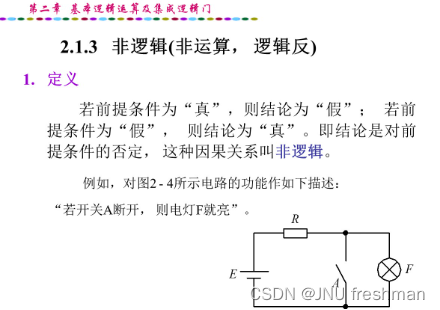

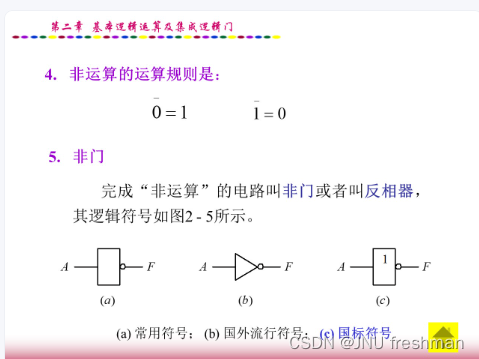

基本逻辑运算

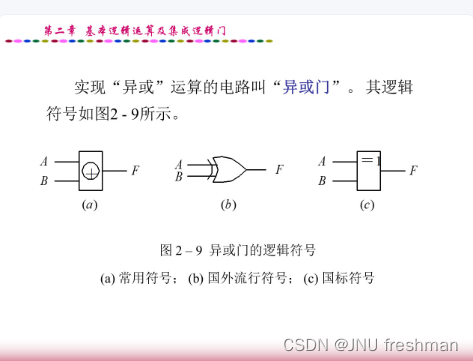

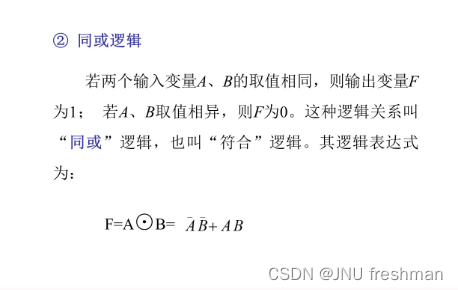

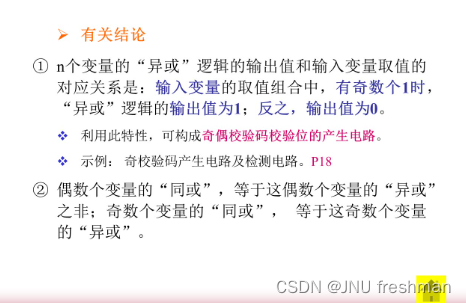

同或逻辑电路的门电路就是异或少一个1

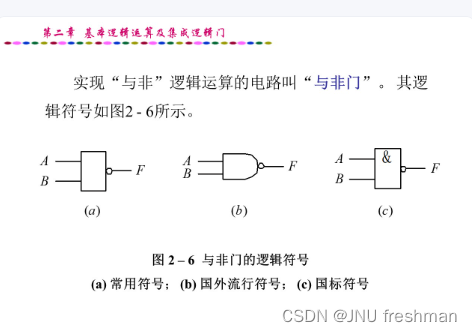

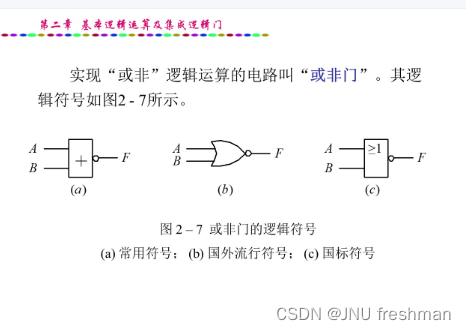

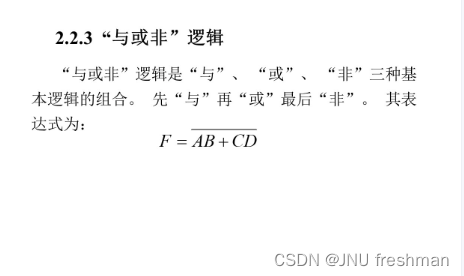

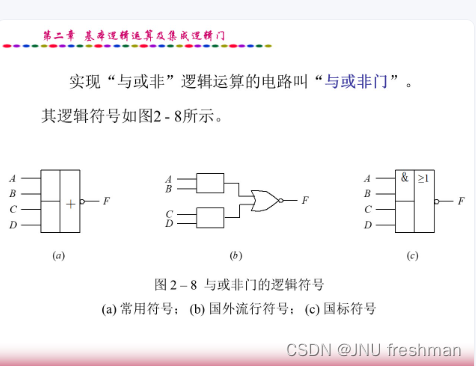

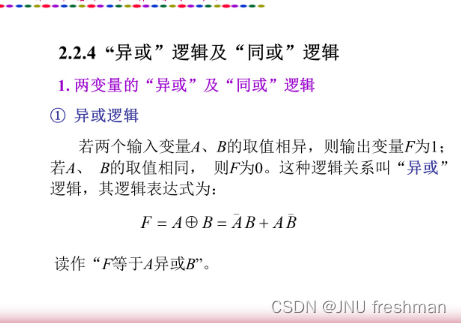

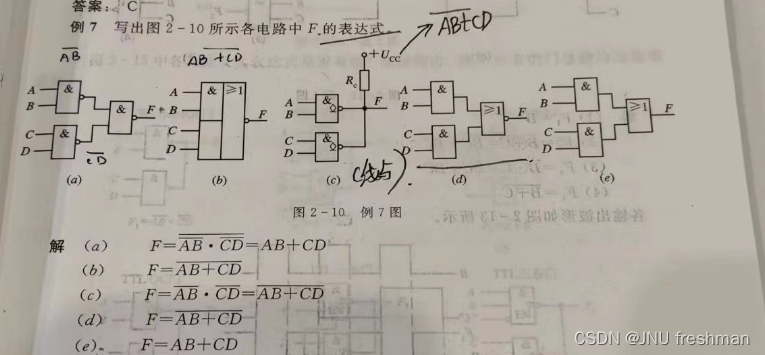

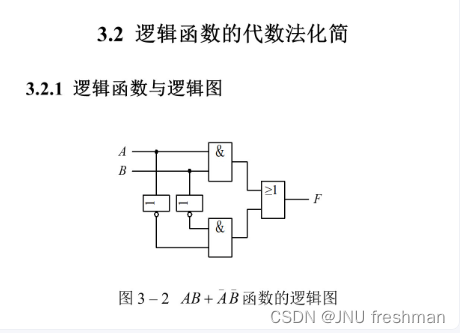

门电路图大总结:与门是& ,或门是>=1 ,非门是 1 o ,与非 是 & o ,或非是 >=1 o , 异或是 = 1 ,同或是 =

应用

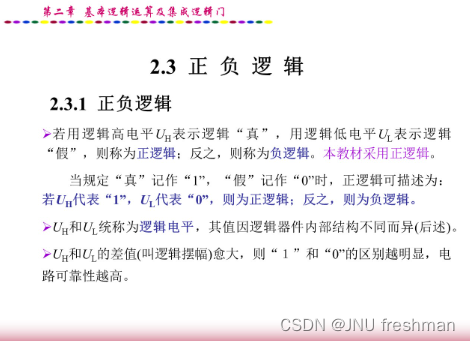

集成逻辑门

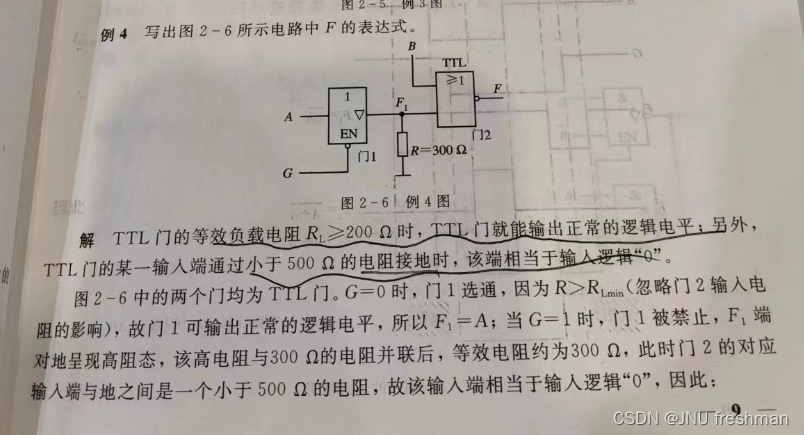

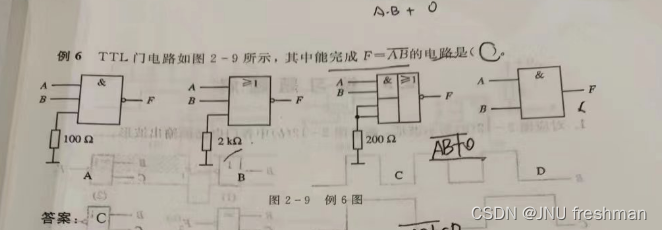

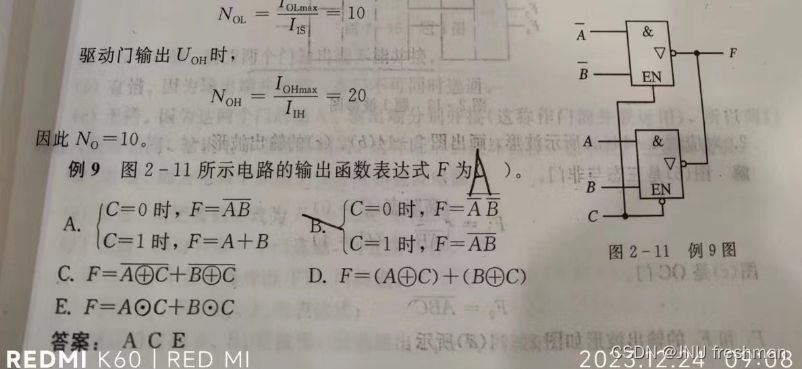

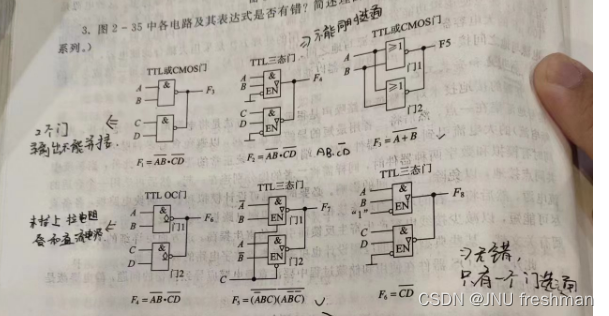

TTL 三态门与CMOS 门

小结一下:

(1)三态门是不允许的多个输出端接通的,但是如果这几个输出一模一样那是可以的

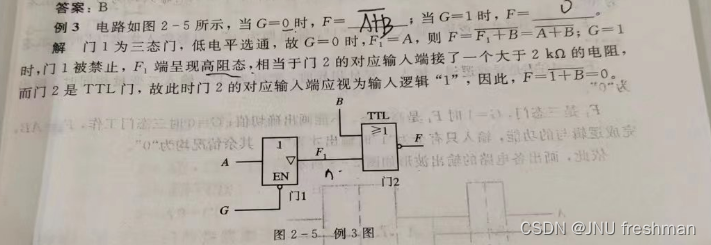

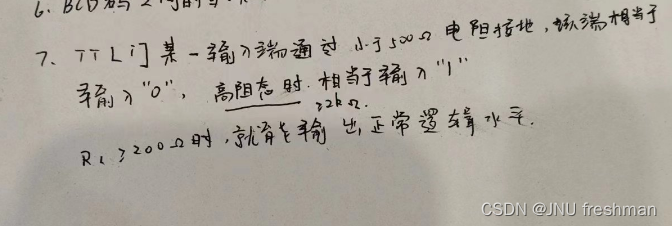

(2)TTL 三态门的具体的工作状态要看 EN端,当EN 端不符合且后面没有电阻,那么就是处于高阻态,(电阻>2千欧),相当于给后面的输入端输入'1',如果后面的电阻是处于200欧 到 500 欧,那么就是可以正常输出的,且输出'0'

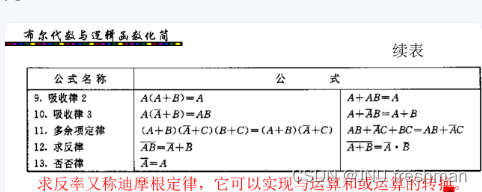

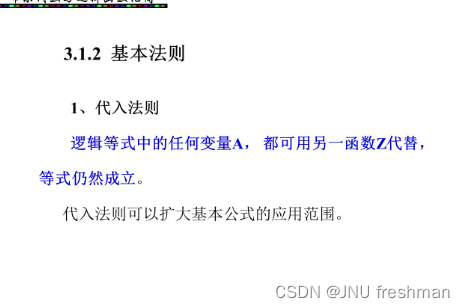

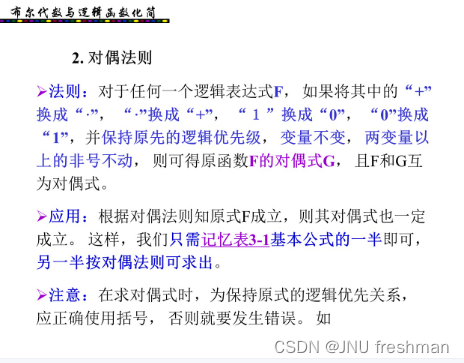

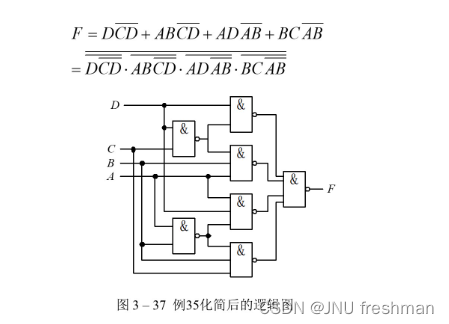

布尔代数与逻辑代数

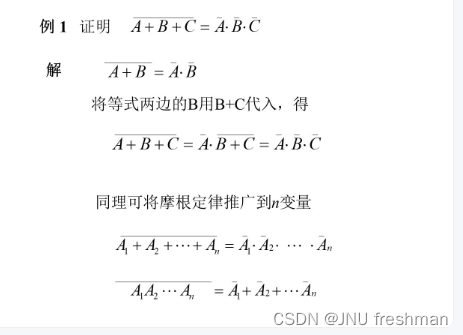

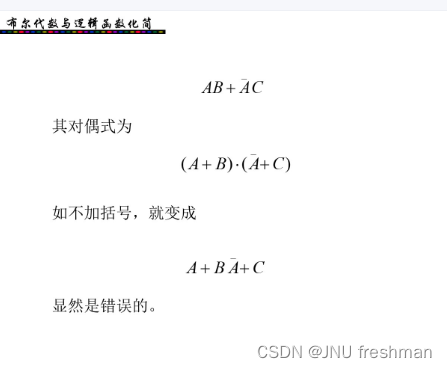

基本公式和法则

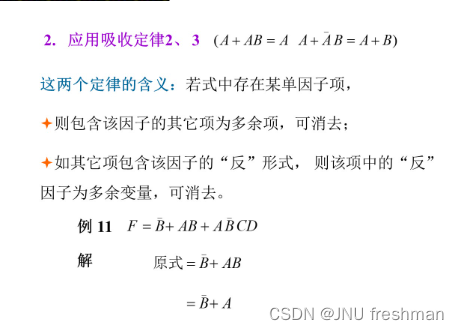

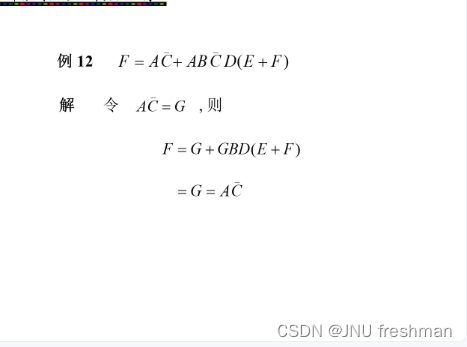

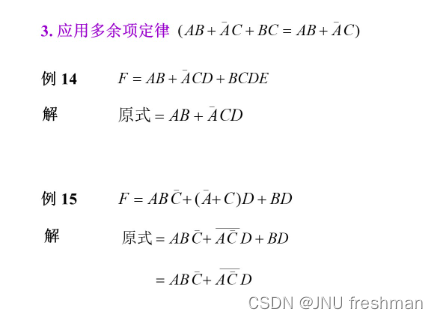

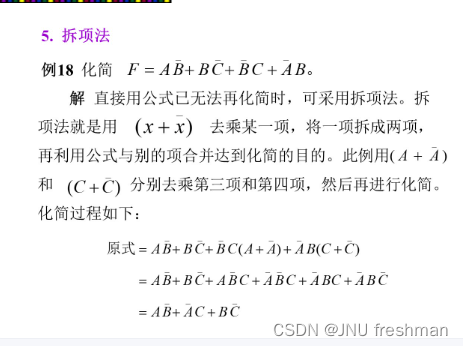

应用

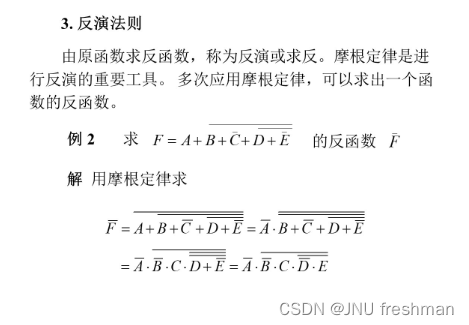

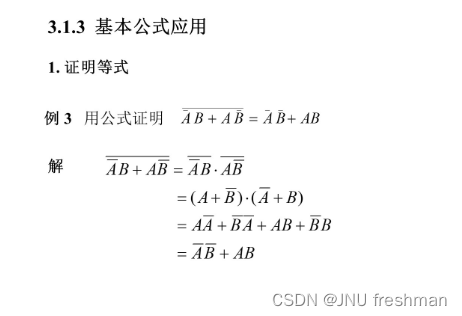

证明

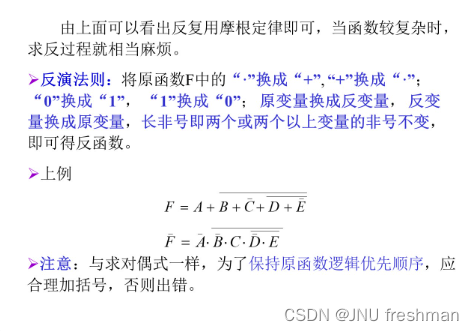

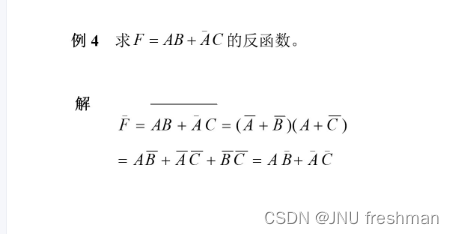

求反

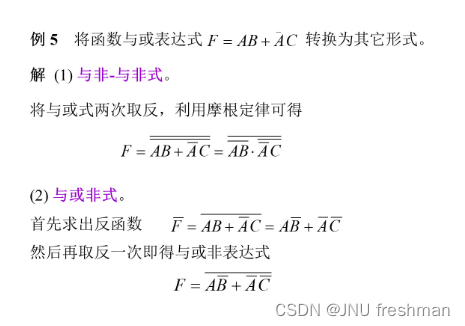

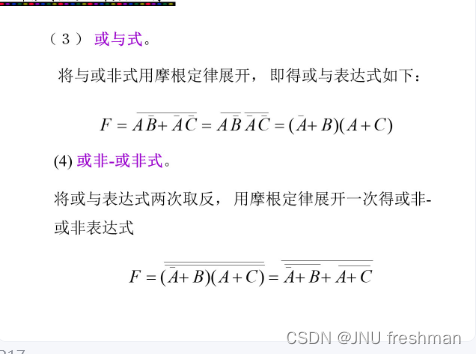

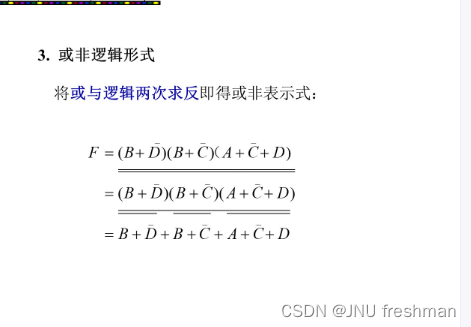

不同表达式的转换

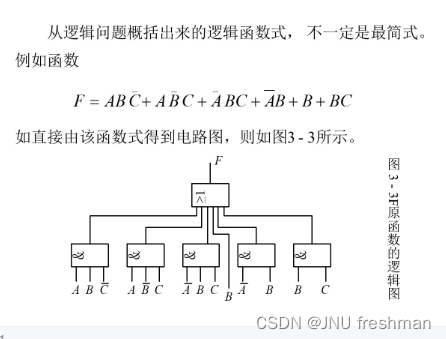

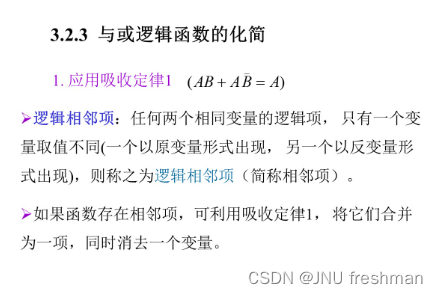

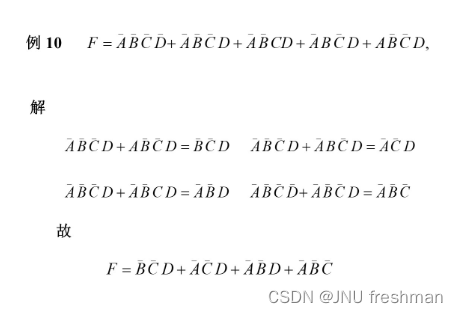

逻辑函数的化简

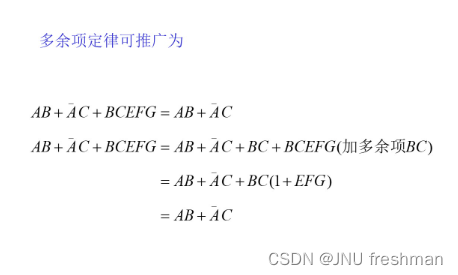

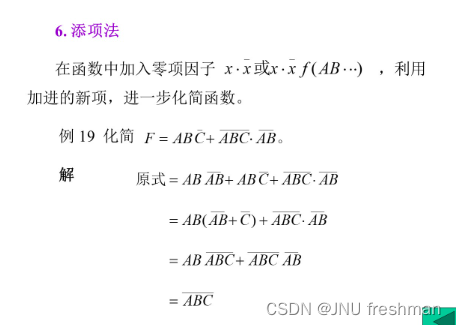

注意:可以通过等幂律将原来的式子的项增加相关的元素

注意化简得顺序也十分重要

观察式子,上题的变形十分巧妙

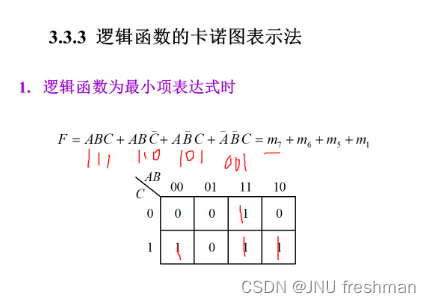

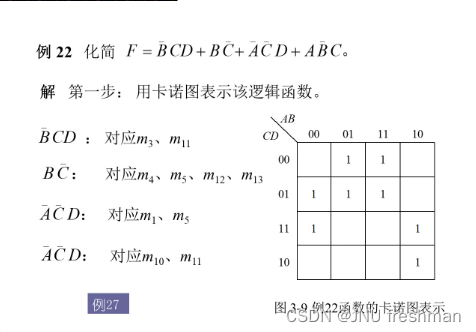

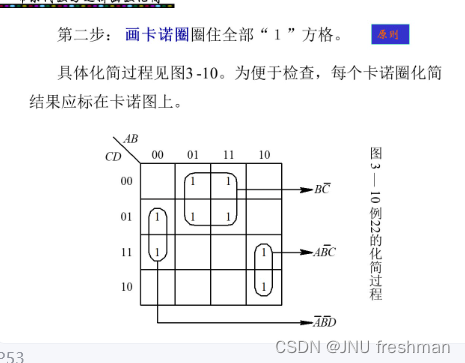

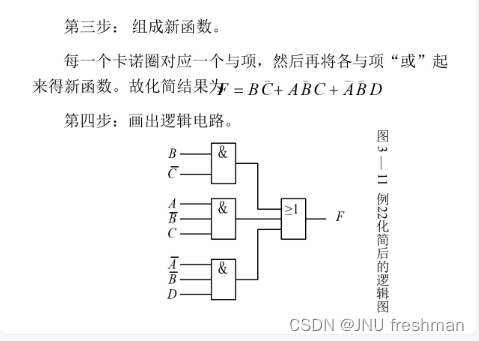

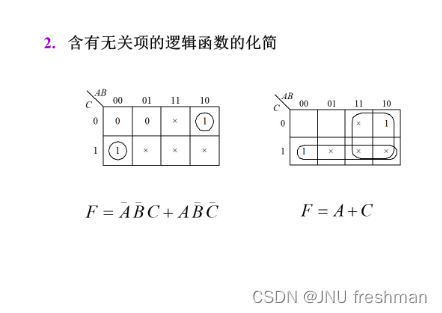

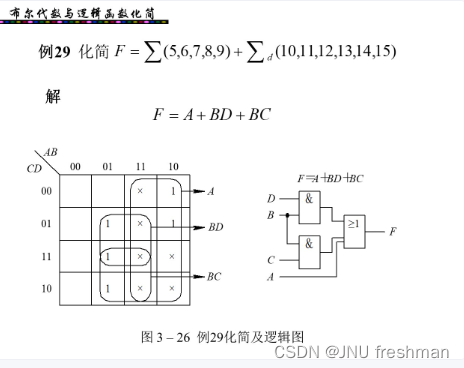

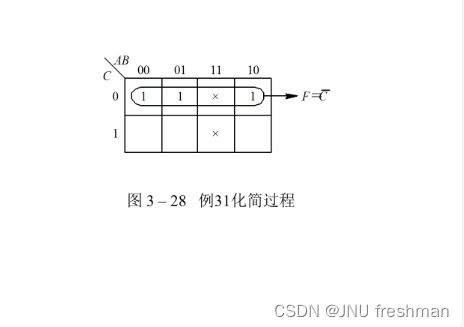

卡诺图的化简

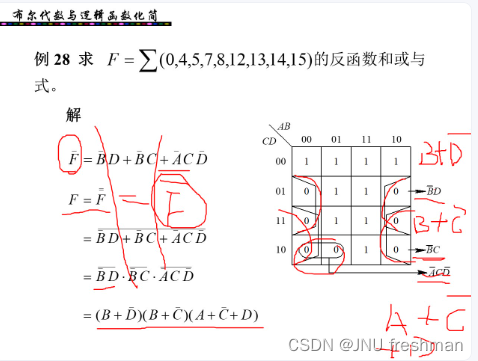

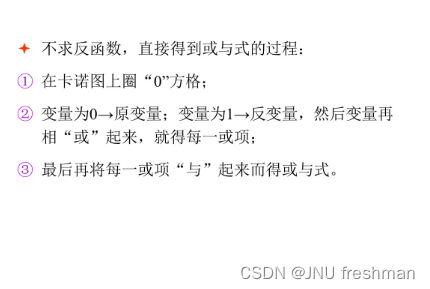

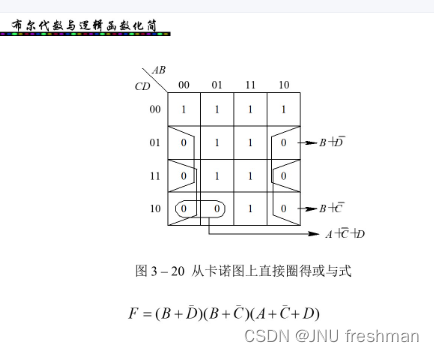

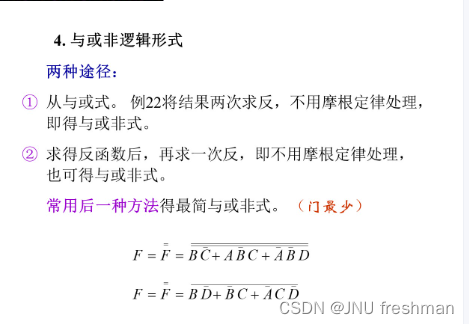

对于与或式以及与非式,通过卡诺图来得到结果的话,都是圈1的部分,直接得到与或式,然后对于与非式的求法,就直接将与或式求两次非即可

或与式,由于从与或式求的话,要先求它的反函数,再取反,那么反函数怎么求解?就是在卡诺图中圈0即可,然后写出反函数的逻辑表达式,对反函数求反就得到或与式

个人觉得该方法没有必要

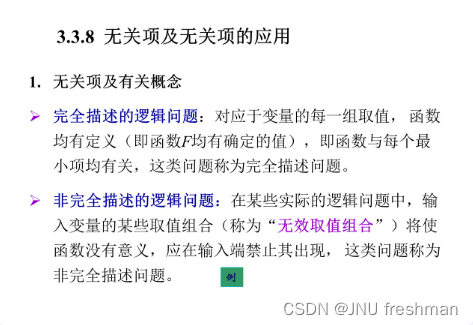

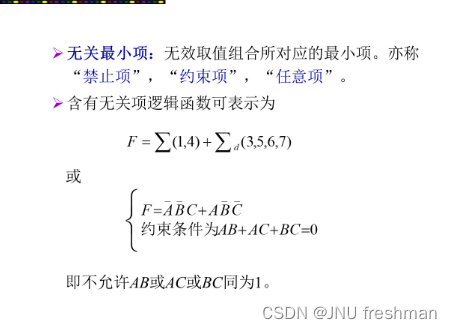

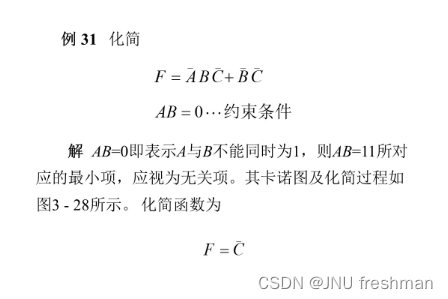

无关项以及相关应用

对于约束条件的第二种表示的理解:由于约束项表示的是当处于这个项的才是安全的,那么反过来就是要不满足约束项的话,就会使得逻辑电路混乱丶,会得到无效组合

总结:对于无关项的给出会有两种形式:一种是求和符号下标带个d ;另外一种是写成一个式子,例如上题,AB=0为其约束条件,就是说说明A,B 必须同时为1

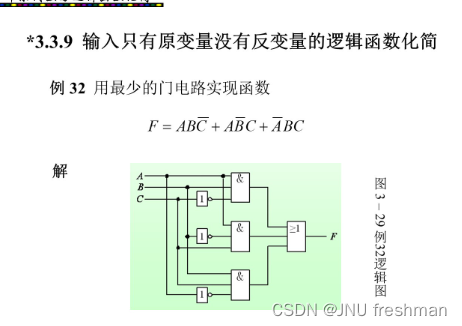

有原变量没有反变量的化简

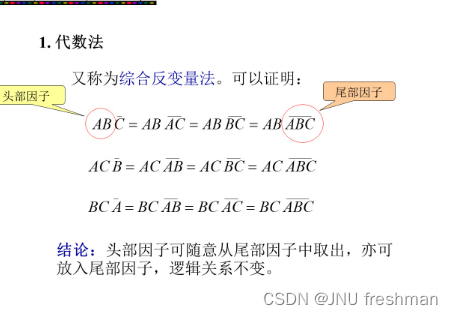

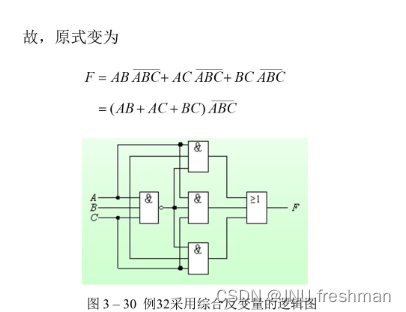

代数法

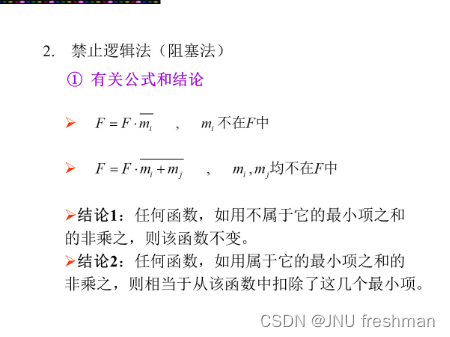

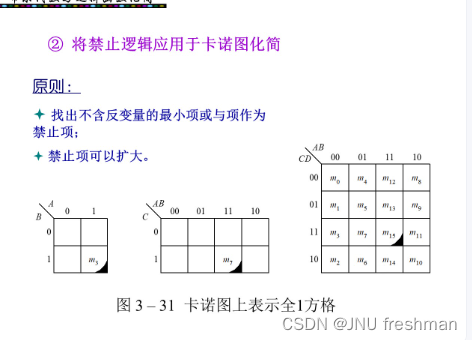

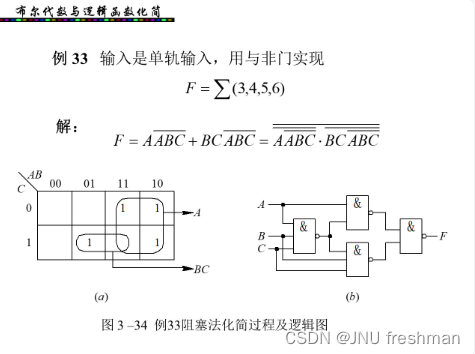

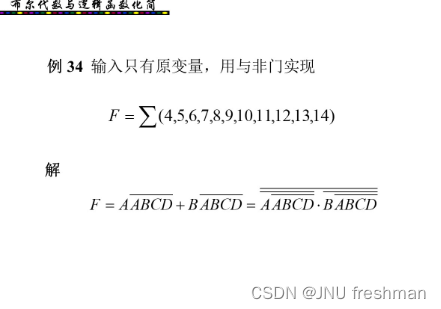

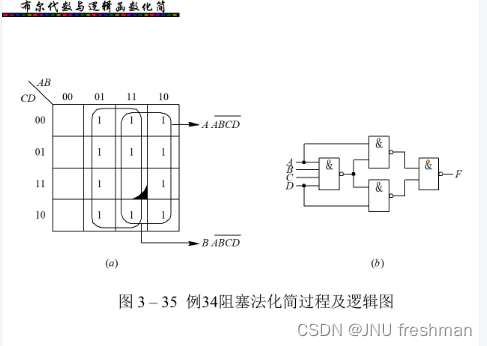

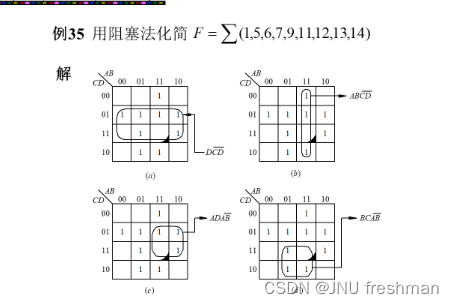

阻塞法

可以结合无关项来进一步简化表达式

以上的两个运用阻塞的电路,阻塞项都虽然形式上属于F 之间,但是原来是没有属于F 的,当删除F 中相对应的元素,就是原来的式子,而且删除的还只是一个最小项,且十分明显,显得简单很多

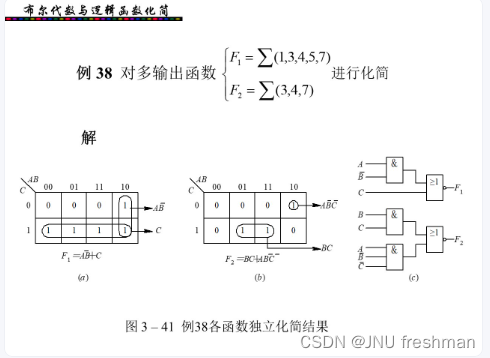

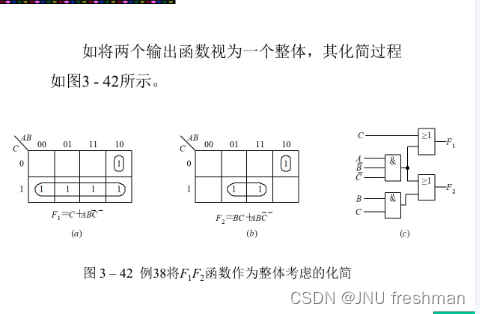

多输出函数的化简

组合逻辑电路

组合逻辑电路的分析

- 组合逻辑电路:当前的输出只和当前的输入有关

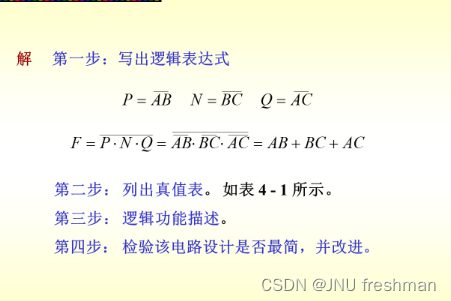

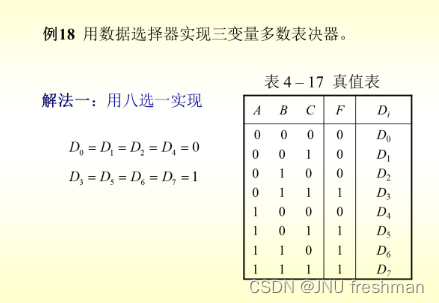

例子1(三变量多数表决器)

- 对于逻辑功能的描述:

我们可以看到,在输入的三变量中,只要有两个以上的变量为1,结果就输出1

---->功能描述为三变量多数表决器

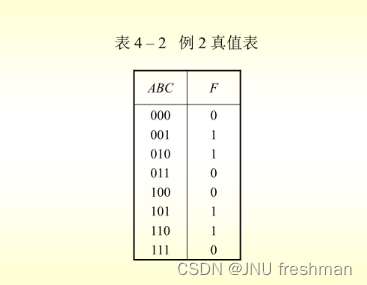

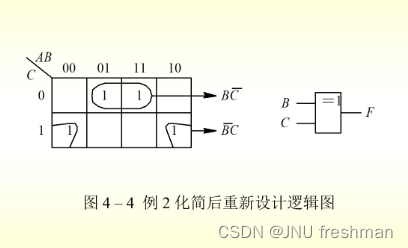

例子2 (两变量的异或电路)改进

- 对于电路的改进的话,就是由于原来的的函数表达式不够简练,导致逻辑电路图过于繁琐,所以在确认电路的功能以及画好卡诺图之后,就可以根据卡诺图来进行进一步的设计电路

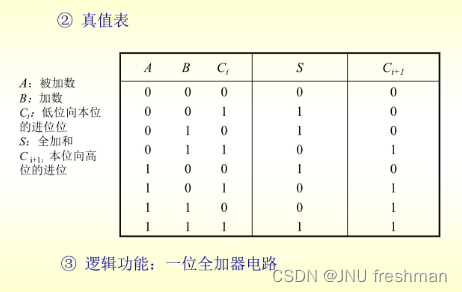

例子3(全加器)

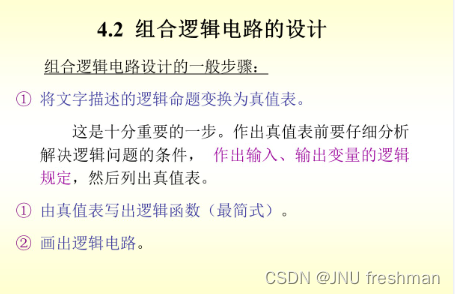

组合逻辑电路的设计

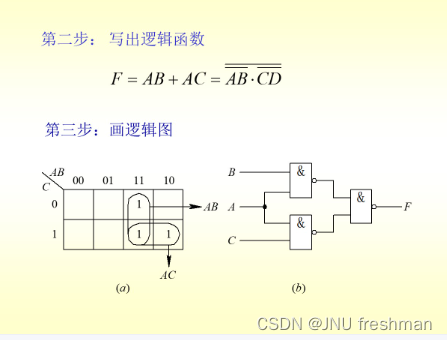

例子1

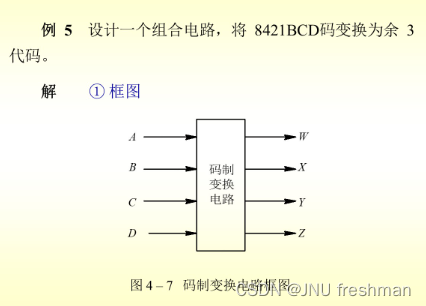

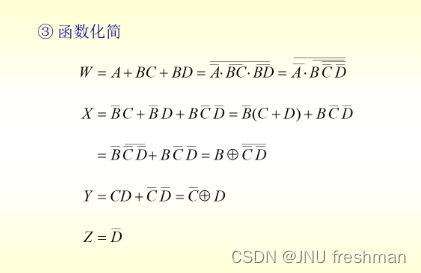

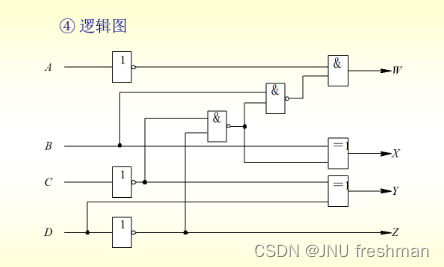

例子2 (编码的转换 8421BCD 转换成 余3 码)

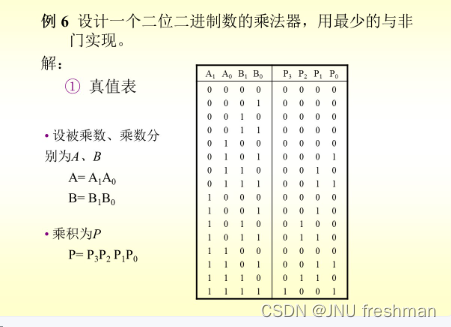

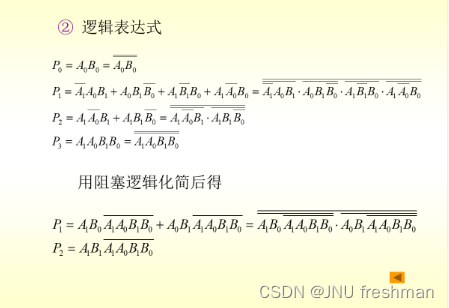

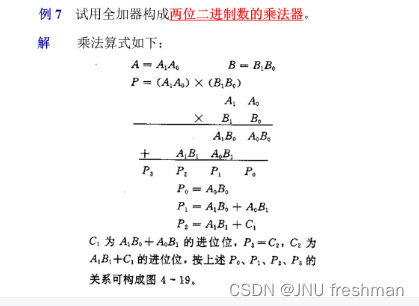

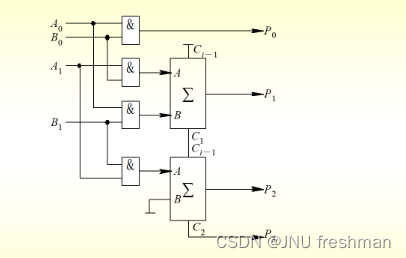

例子3 (二位二进制乘法器)

- 如何理解二位二进制的乘法器:

一位两个二进制相乘并不会带来进位,而是在最后的对应的位数相加的时候才会带来进位,所以最终的结果也要4 位二进制才能存储

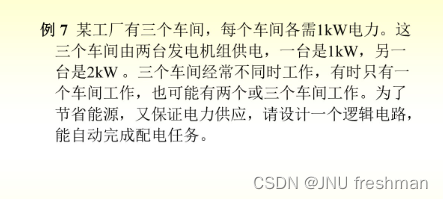

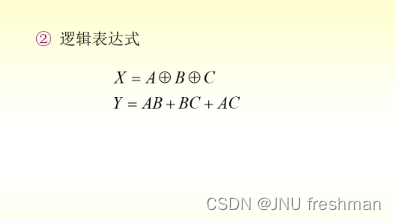

例子四 (结合生活实际)

常用中规模组合逻辑部件的原理和应用

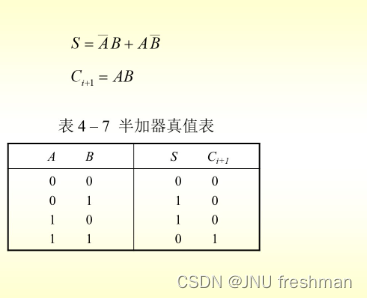

半加器与全加器

简单来说,半加器就是没有考虑从低位的进位

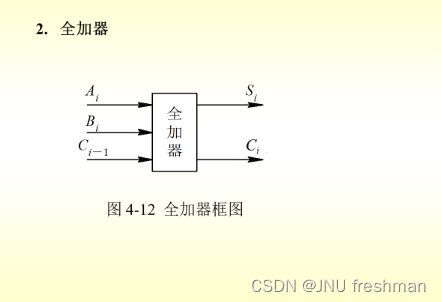

全加器就是在半加器的基础上,增加了考虑低位的进位的作用

该图的第二个1000改成101

多位二进制加法

全加器的应用

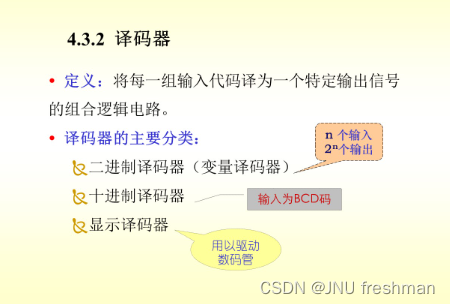

译码器

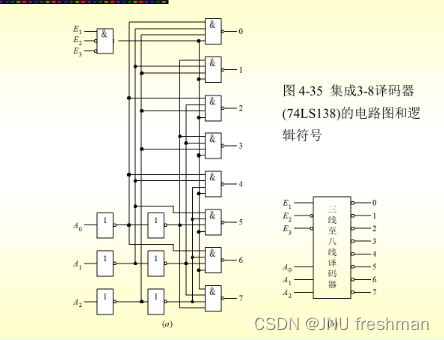

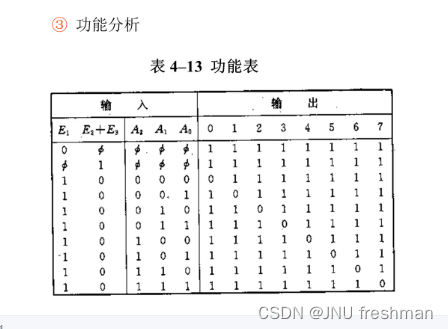

二进制译码器 (将二进制转换为十进制)(74LS138 译码器)

输出是低位有效,假如 输入000,本应该是输出0端为高电平,但是由于输出端口是低位有效(输出的时候取非),现在只有0 是低电平,其他的都是高电平

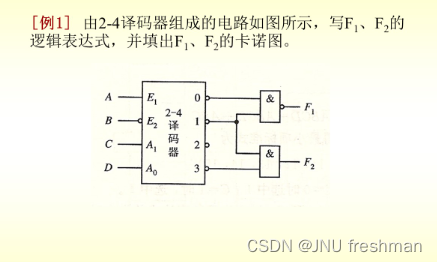

应用1

列出每一个状态之后,要化简,写状态的时候加上使能端,然后最后进行讨论,当译码器正常工作与不正常工作的时候的输出的表达式

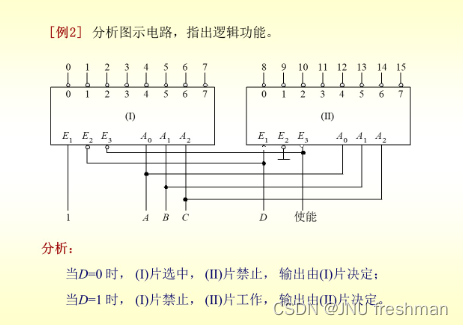

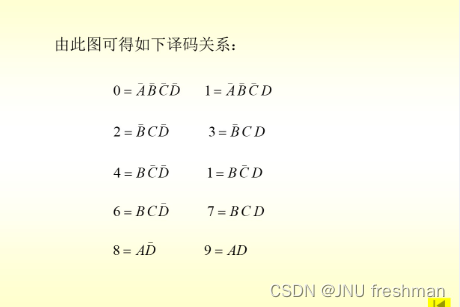

应用2

十进制译码器(将二进制转化为十进制)

并不会直接输入十进制数,然后输出二进制数,而是类似于运用8421BCD 码进行代替十进制输入

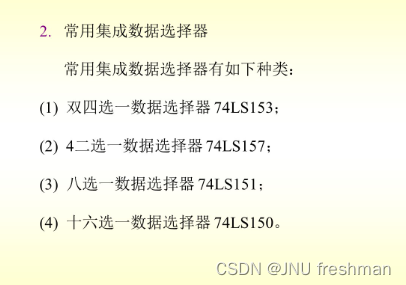

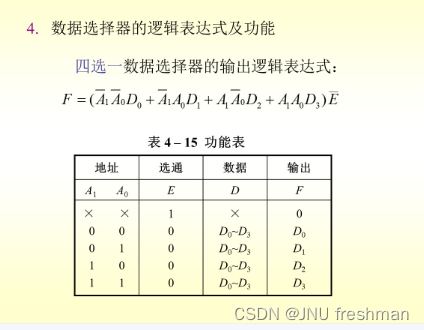

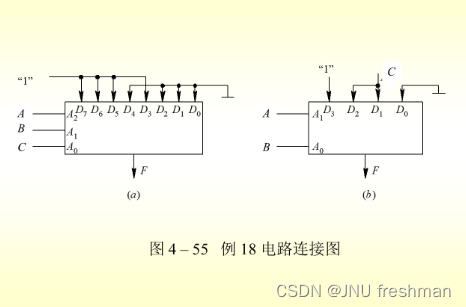

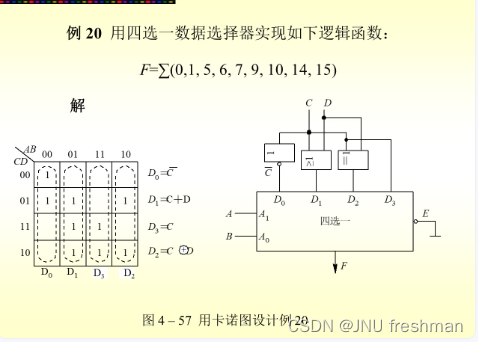

数字选择器

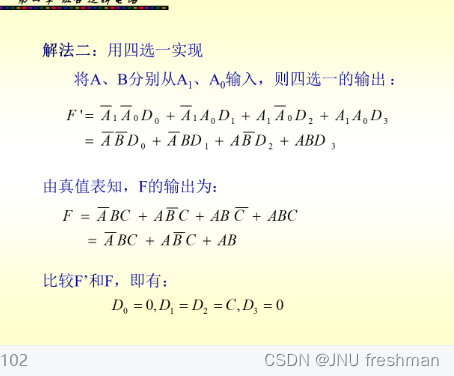

应用1(实现三变量多数表决器)

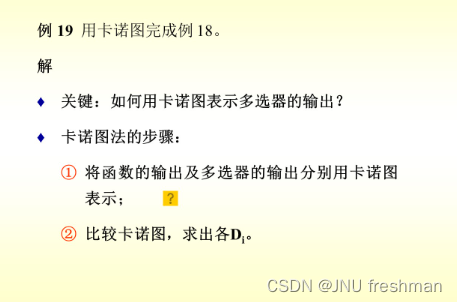

如何运用卡诺图将数字选择器充分利用

数字选择器的本质就是:通过地址变量的值,从数据输入端中选择数据,当与其他电路结合的时候,那么地址端以及输入端的数据就要根据你的卡诺图来分析,你的地址端选择了几个变量,那么输入端口的值要么是0,1,要么是你的变量除开充当地址变量的那几个变量,这样就可以完成控制

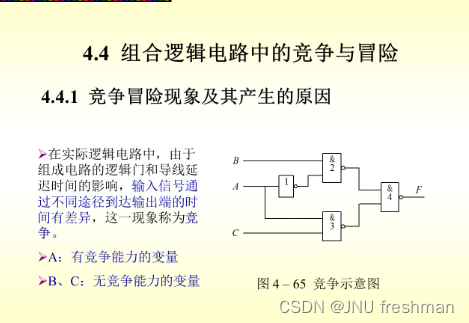

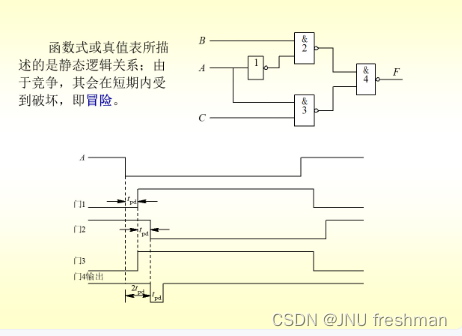

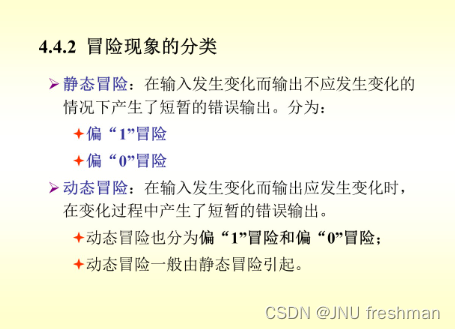

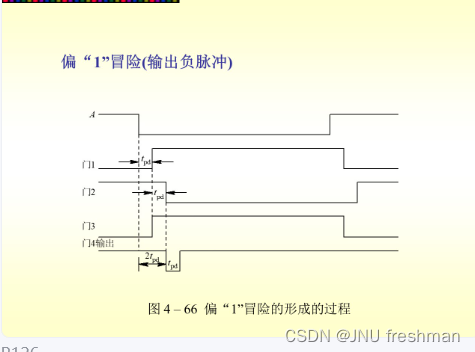

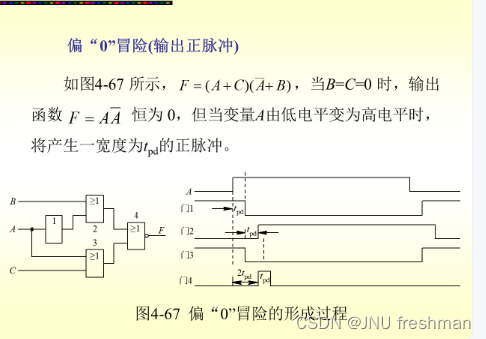

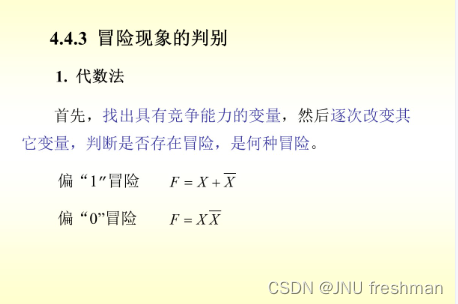

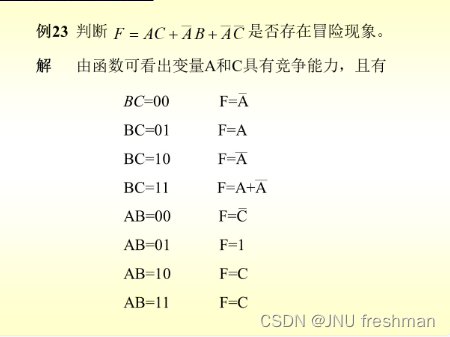

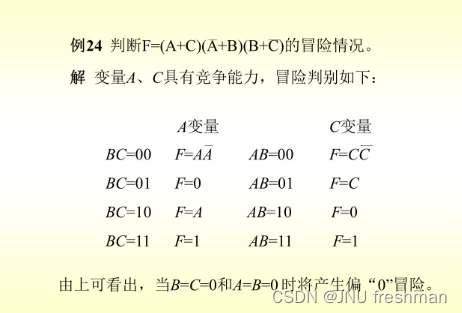

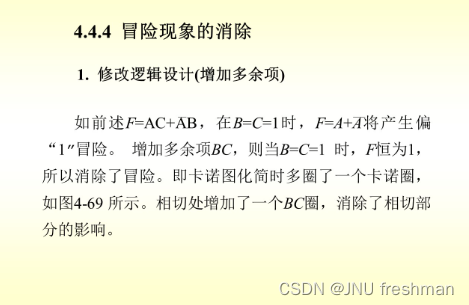

组合逻辑电路中的竞争与冒险

如何理解A 为有竞争能力的变量?A 有多条路径到达输出端,每条路径会有可能由于逻辑门等影响造成最后到达输出端的时间不一致,而 B,C 变量只有一条路径到达输出端,所以就是没有竞争能力的变量

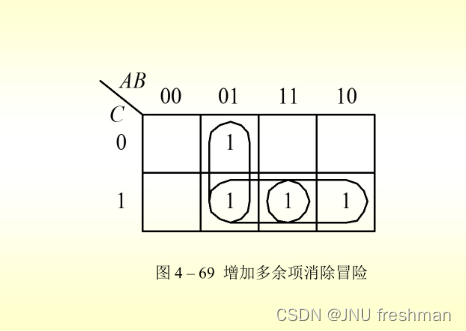

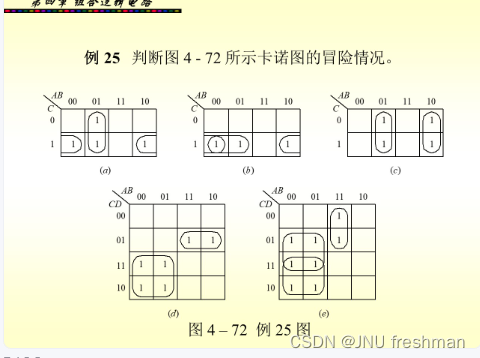

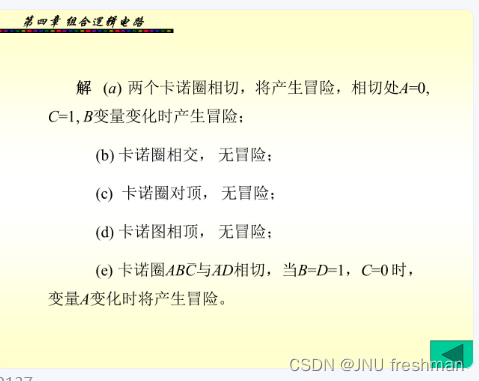

对于代数法进行总结:先看表达式:如果是几个变量的或,那么就要查看是否有偏1 冒险,如果是与运算,那么就要考虑是否为偏 0 运算,其中对于在什么情况下,构成冒险,那么就要看对于某个变量是否存在自身和它的非,然后再枚举所有的可能,找出满足条件的变量的取值对于卡诺图法:对于偏1 的运算还好,就是直接进行在卡诺图上标出1,对于偏0 的运算,要将每一个括号里面的与取非,然后在卡诺图上标出0;标完之后,就找相切的地方除了某个冒险的变量的另外的元素的取值就是满足条件的取值

触发器

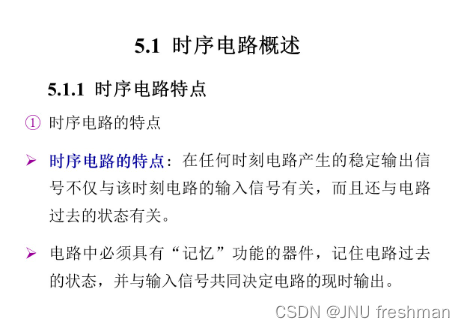

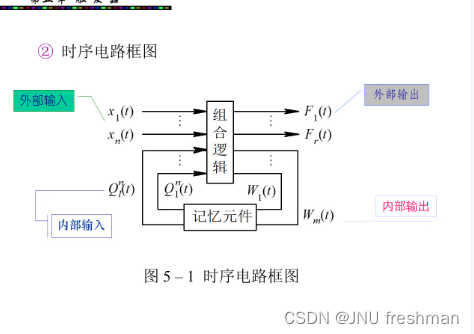

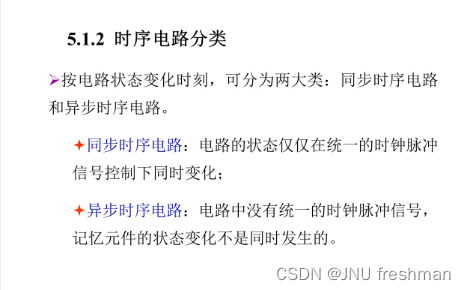

时序电路的概述

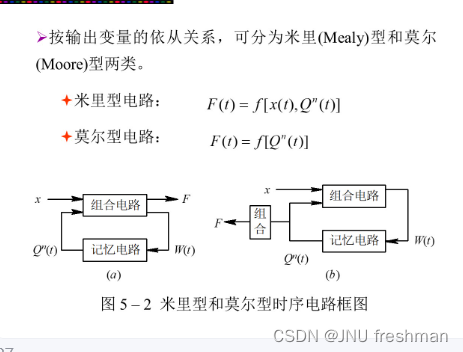

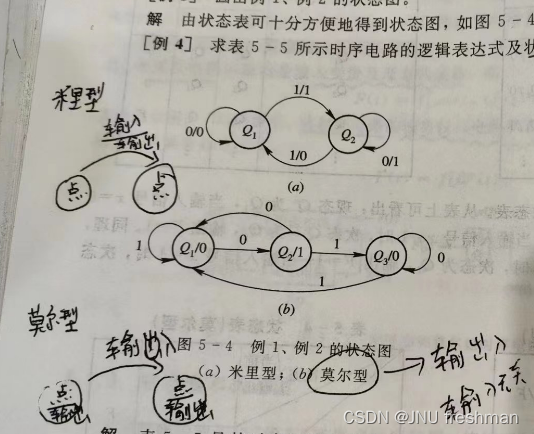

注意米里型 的输出是输入变量以及现态的函数,而莫尔型的输出只和电路的现态有关

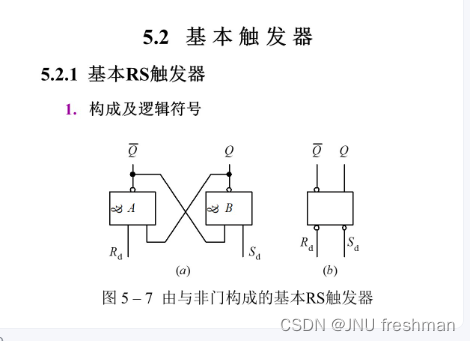

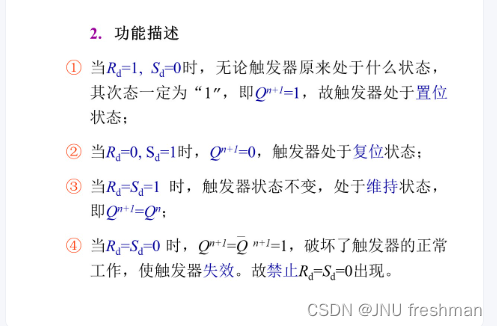

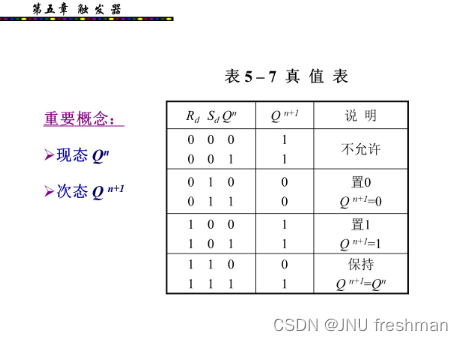

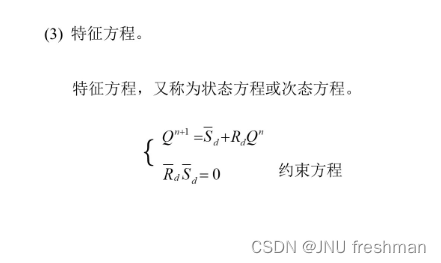

基本触发器

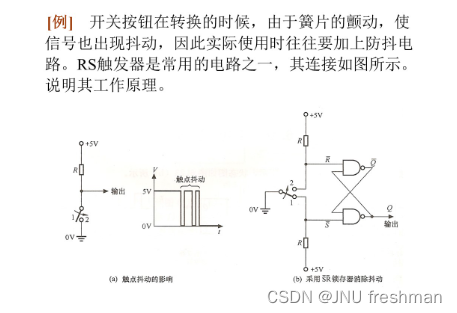

RS 触发器

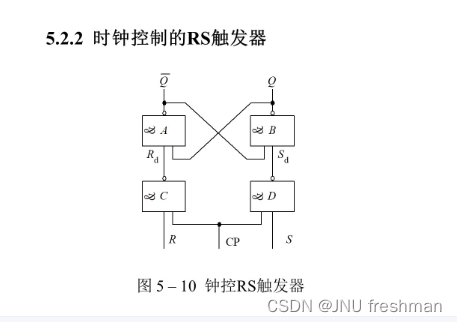

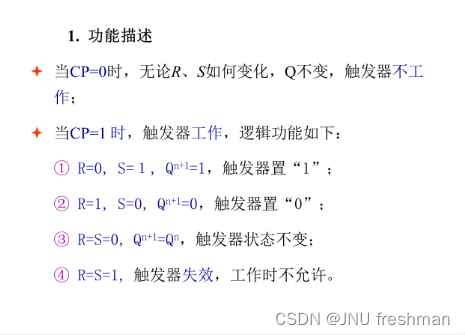

时钟控制的RS触发器

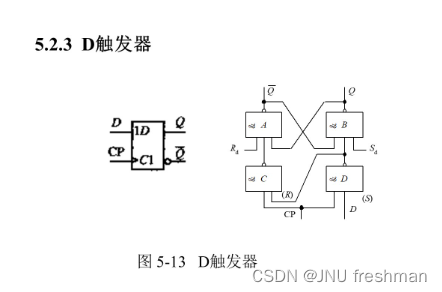

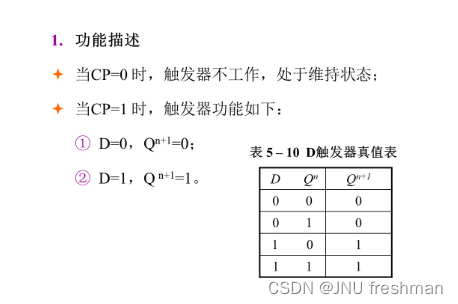

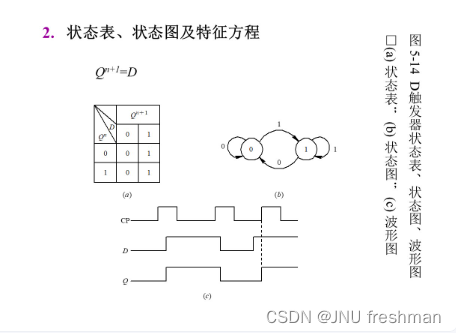

D 触发器

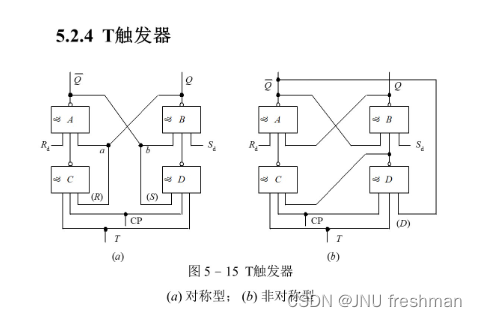

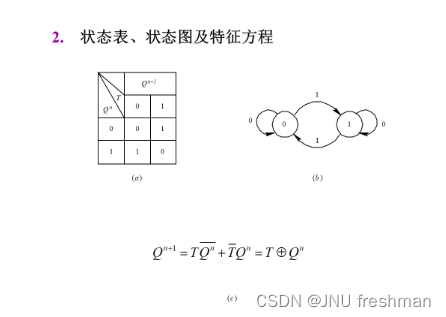

T触发器

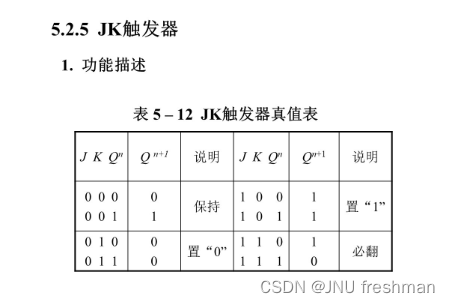

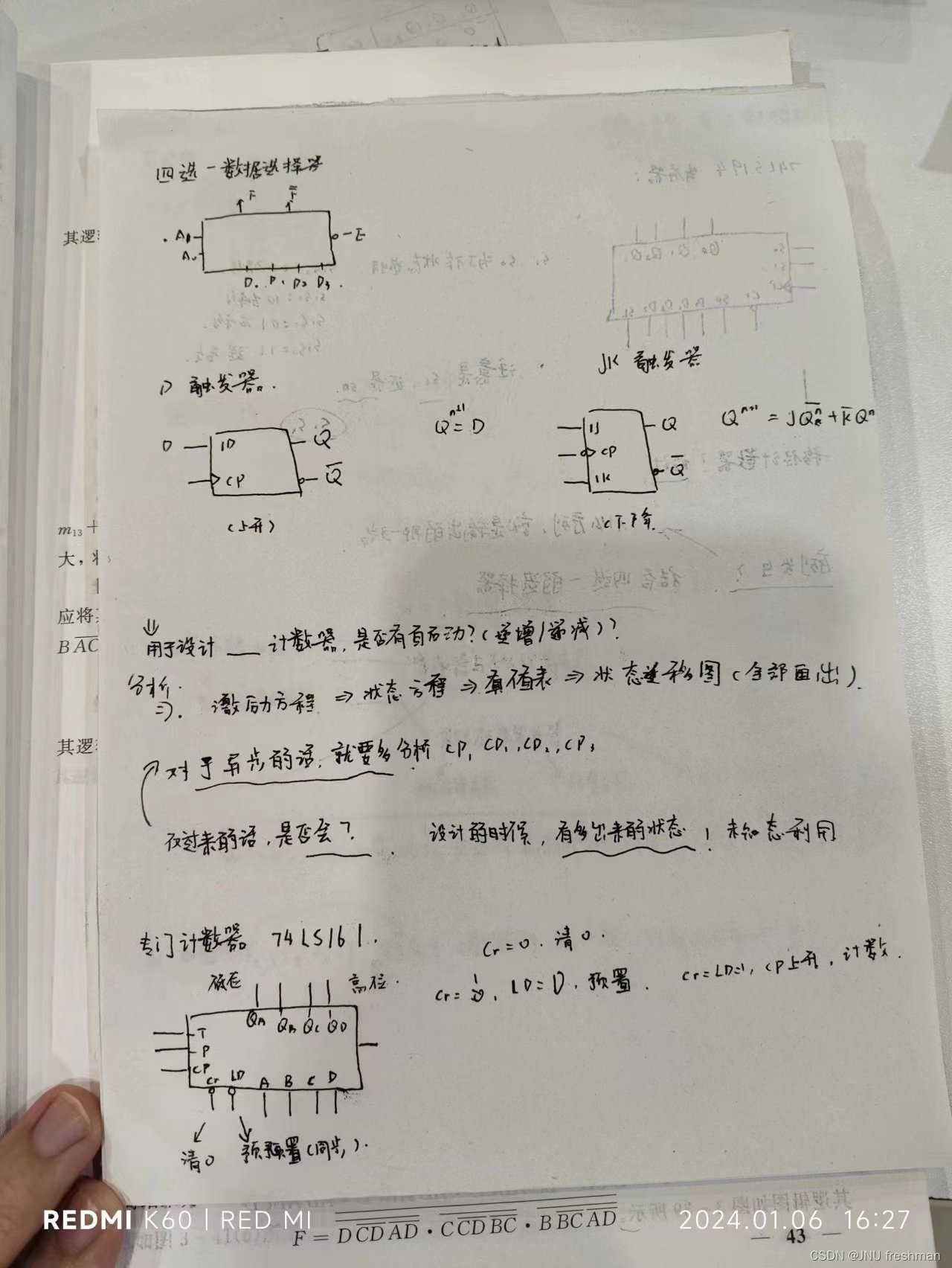

JK 触发器

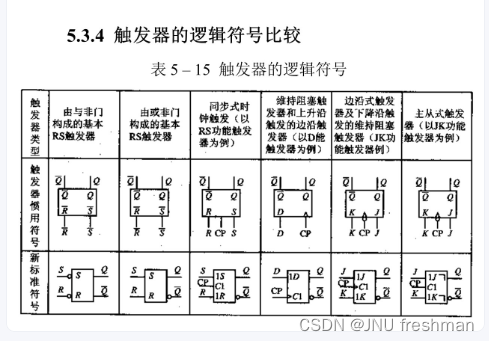

触发器的逻辑图

注意,cp端如果增加了'>',那么就是边沿触发,否则就是水平触发,其中还加上o 那么就是下降沿触发,不加o 就是上升沿触发

时序逻辑电路

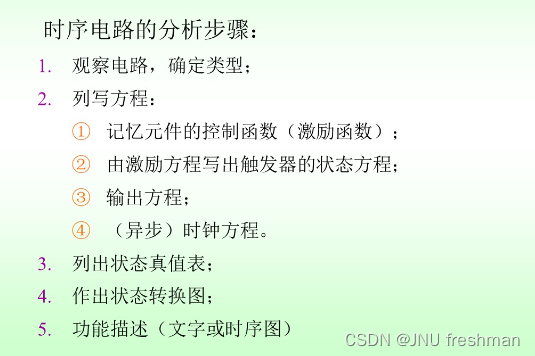

时序电路的分析

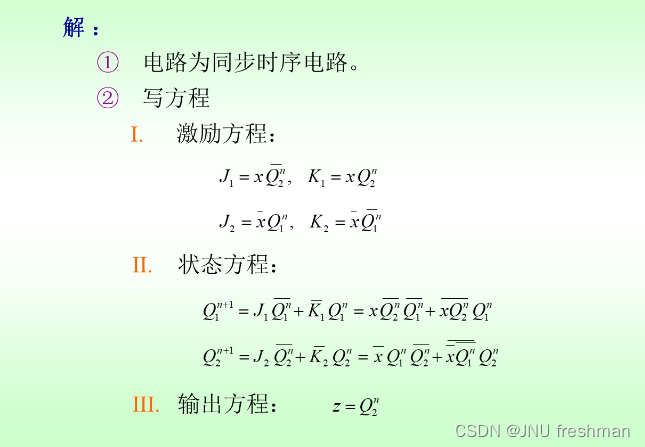

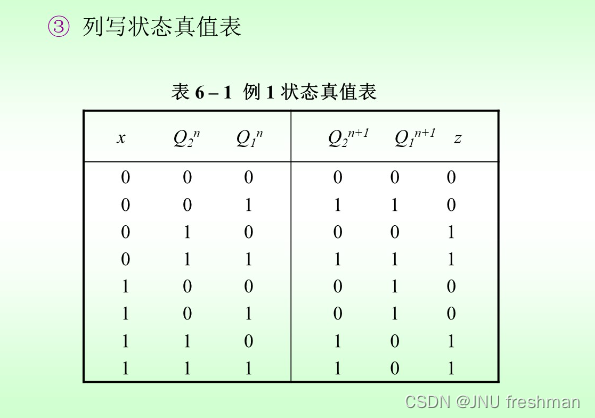

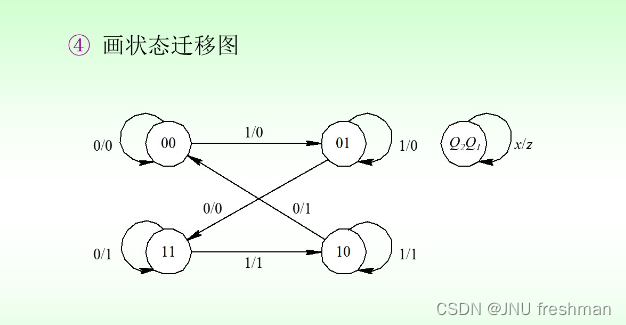

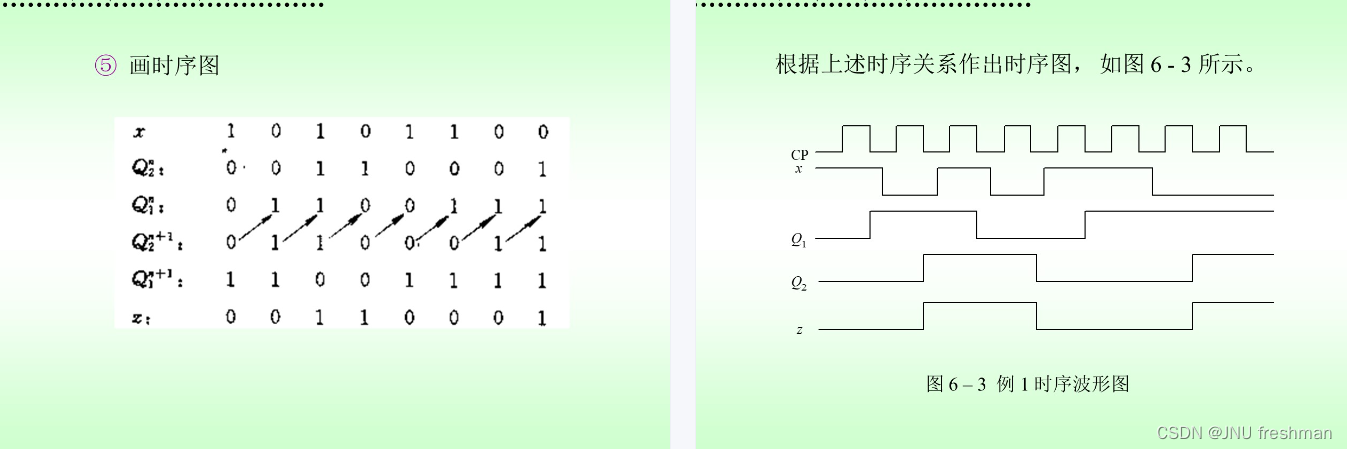

同步时序电路的分析

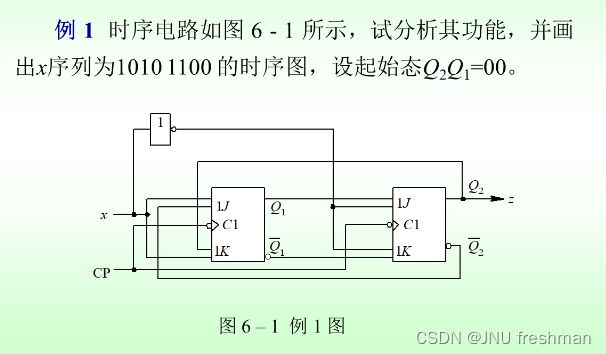

例子1(有输入输出)

例子2 (只有输出)

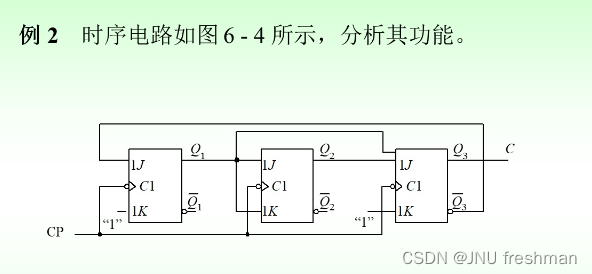

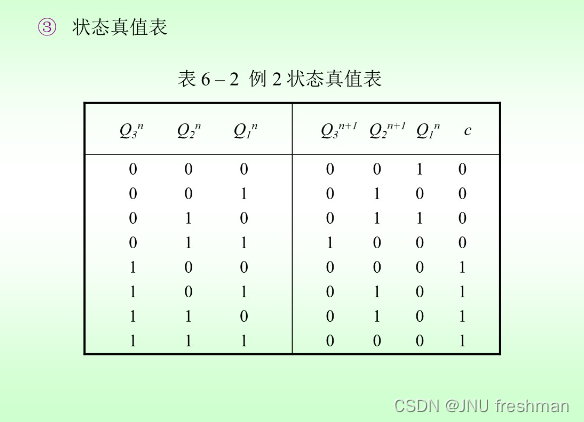

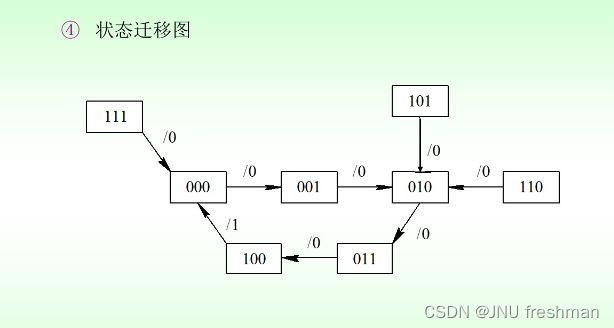

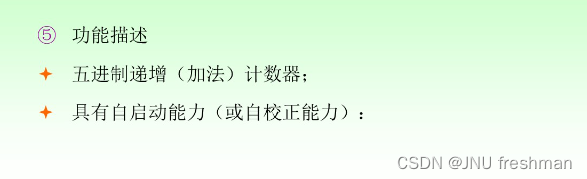

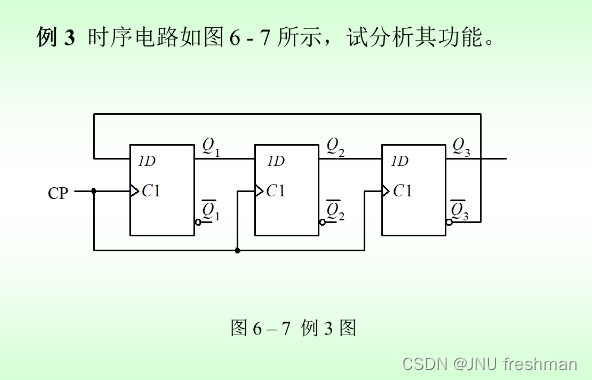

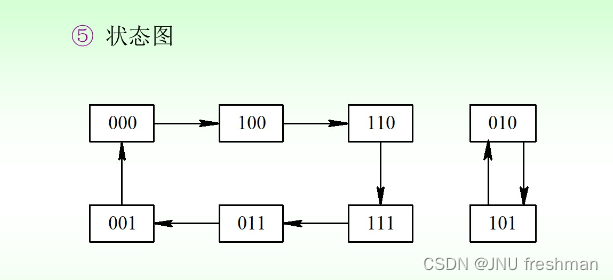

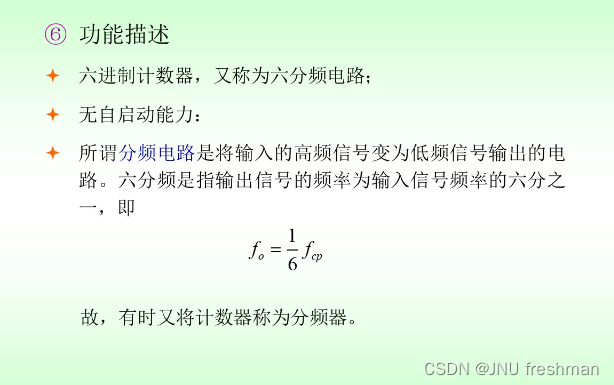

再看一个例子(没有输入,有输出)

分析的步骤和上面的例子一样,唯一不同的就是真值表,状态迁移图

例子3(没有输入、输出)

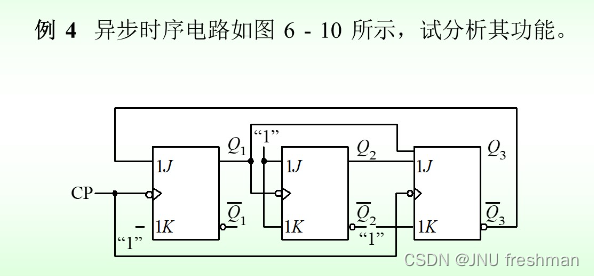

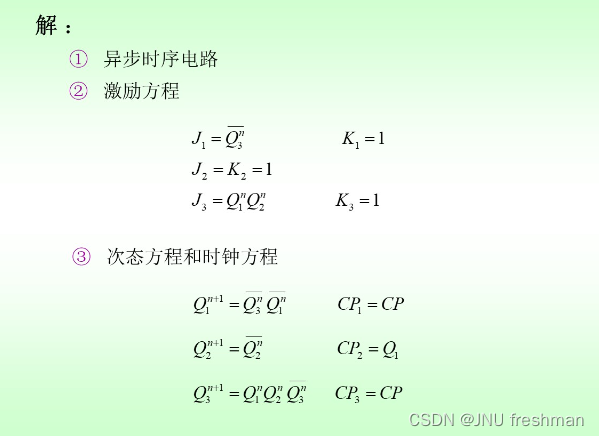

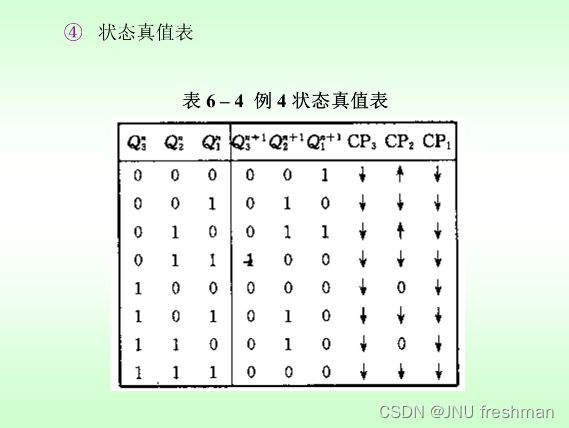

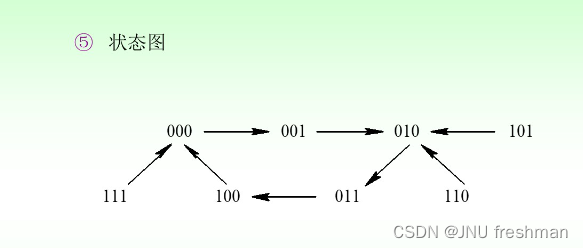

异步时序电路的分析

例子1

小结

- 对于判断是否为同步还是异步,直接看触发器的cp 端,是否受同一个时序信号控制

- 不同的电路,总体都是一样的,除了个别电路有输入,以及输出,那么在写真值表,以及激励方程、特征方程、输出方程的时候要注意

- 对于要画时序波形图的,可以先画一个时序图,或者直接根据真值表来画

- 对于迁移图的画法:

(1)输入输出都存在:状态1————(输入/输出)————状态2

(2)只有输出:状态1————( /输出)————状态2

(3)没有输入输出:状态1————————————状态2- 对于异步时序电路:真值表的状态要根据具体的时序信号来判断,一般接cp 的,一直都会处于启动状态,而不接cp 的,就要判断是否为上升沿还是下降沿还是1还是0

对于异步还是对于同步的分析:最大的差别就是真值表上,同步电路是没有显示cp 端的,可是异步那里是会显示每一个触发器的cp 端口的

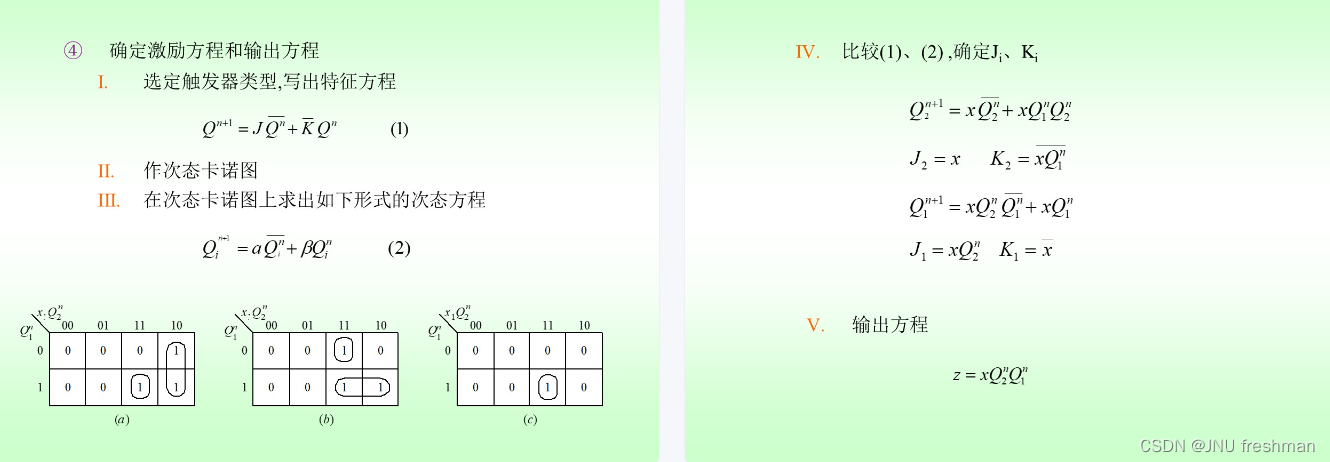

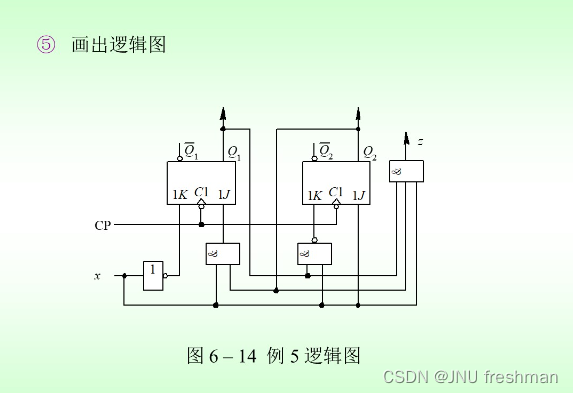

时序电路的设计

同步时序电路的设计

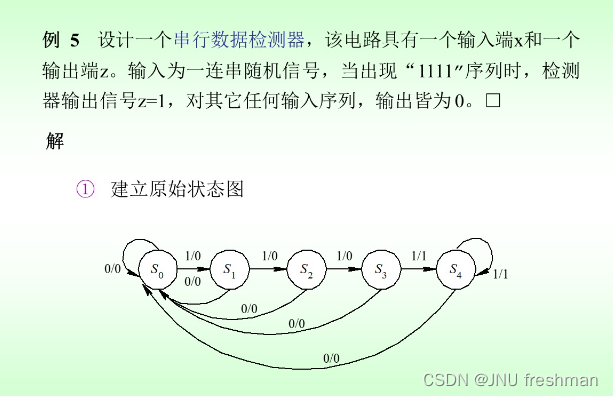

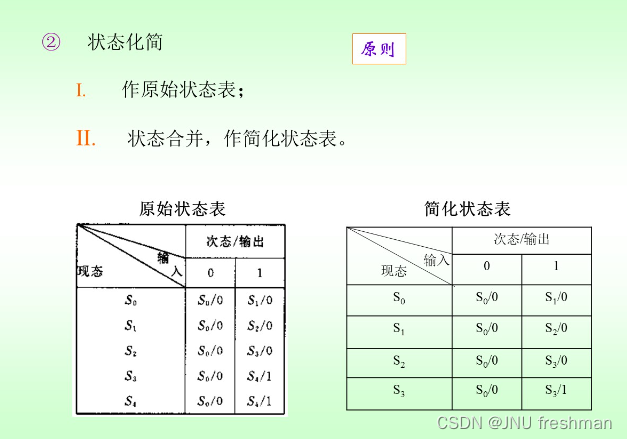

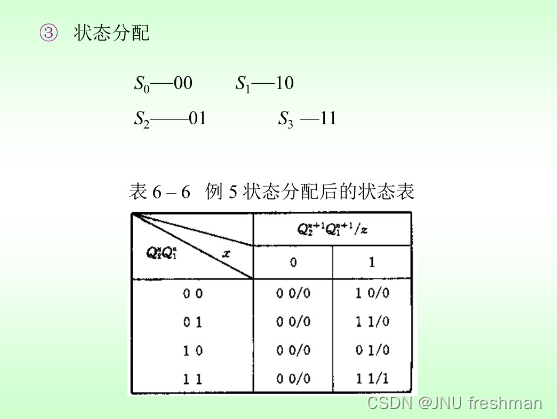

串行数据检测器

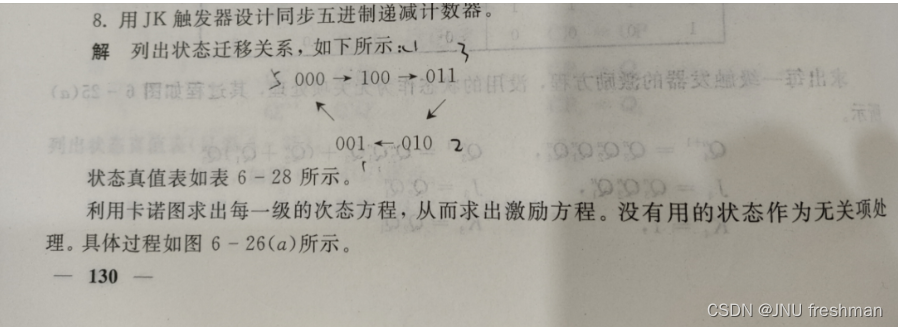

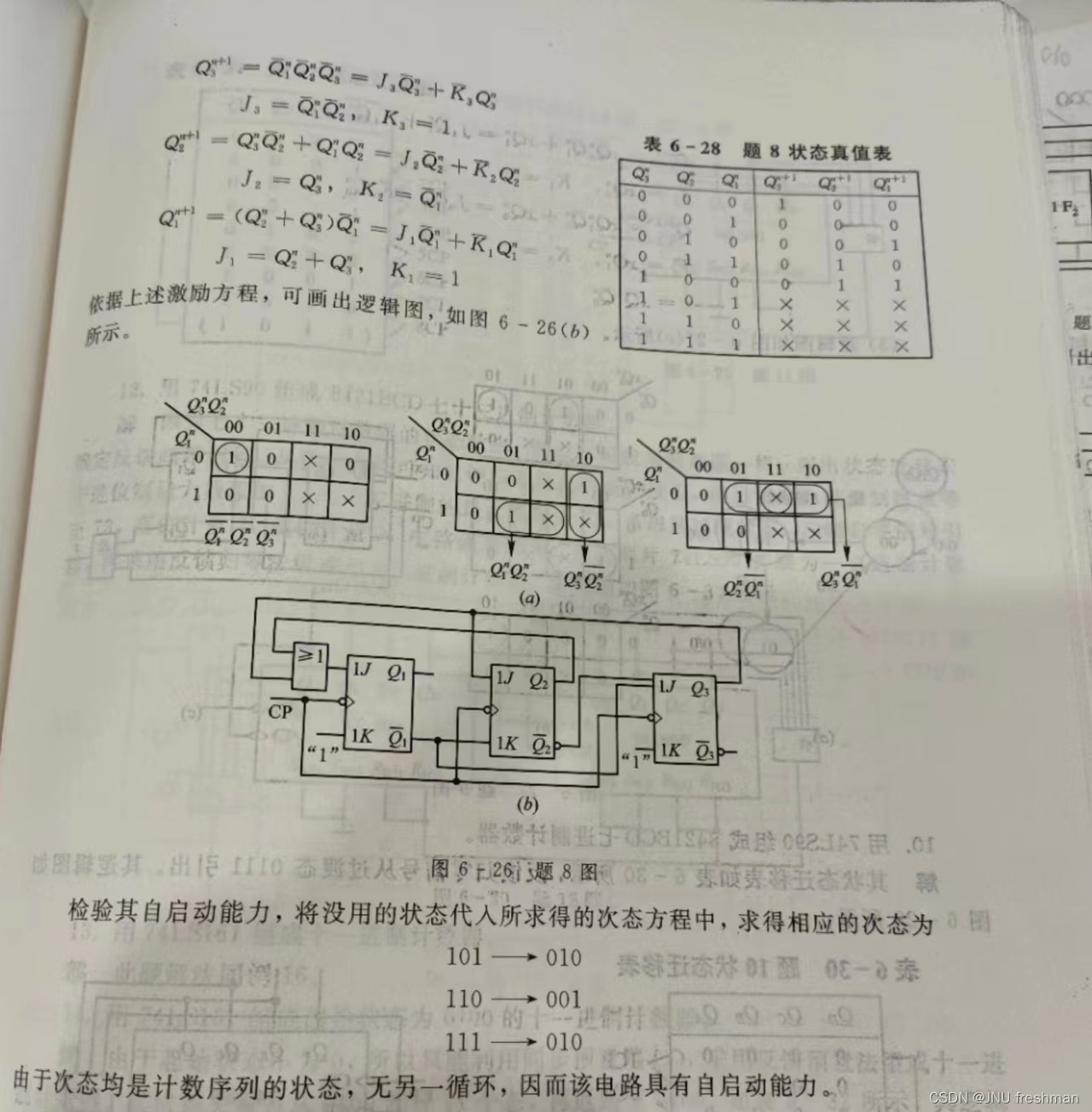

JK 触发器设计计数器

- 对于计数器的设计:

(1)注意要求是用什么触发器(JK 或者 D)

(2)是递减还是递增?举个例子:设计模5计数器:若是递减,那么000就是代表5,000后面的一个状态就是100,最终,001回到000;若是递增,那么000就是0,下面的一个状态就是001,最终100回到000

(3)在根据状态迁移图画真值表的时候,没有使用的状态也要使用,用x来代替状态,这样就是未知态,方便后面画卡诺图,但是后面判断该计数器有没有自启动功能的时候,就要将未使用的状态的后面的状态写出,若是能接到原来的状态迁移图上,则是有自启动能力的,不然就不是

(4)补充第(3):在对时序电路进行分析的时候,由于不知道到底是模几计数器,那么在真值表中就不使用x,而是直接写出下一个状态,这样方便画状态迁移图直接判断是否有自启动能力

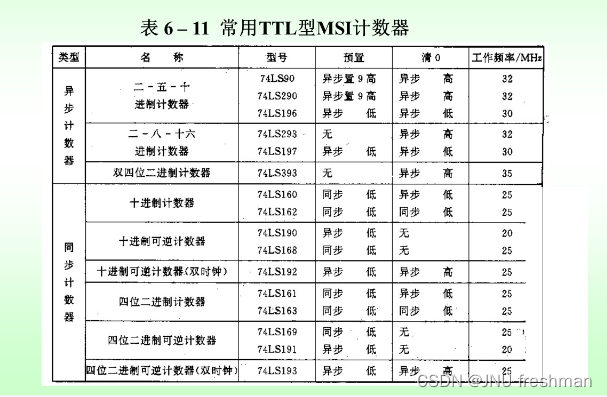

计数器

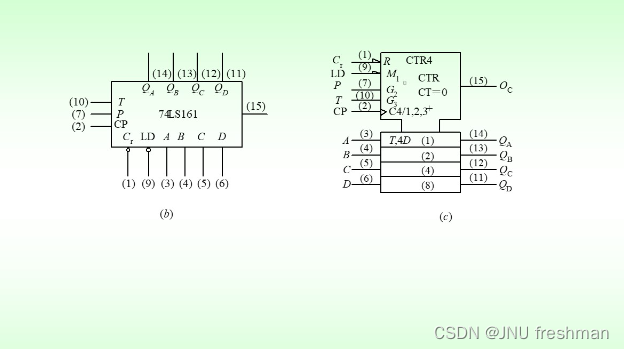

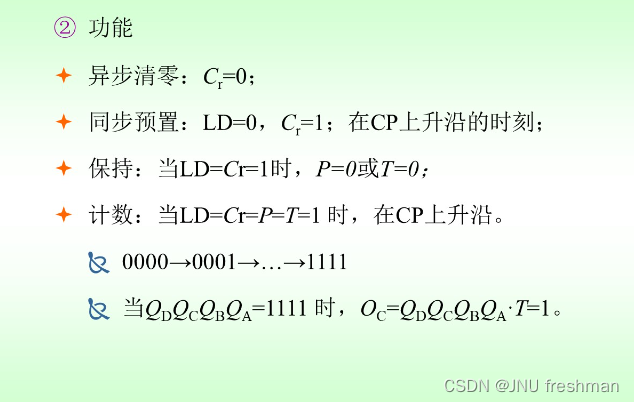

同步式集成计数器 74LS161(可以进行4位二进制的计数)

- 解释:

(1)对于异步清零端Cr:当Cr为0时,立即清零,不受CP 的影响

(2)同步预置:当Cr = 1,LD = 0 时,在CP 上升沿时,将ABCD 的数据进行送入计数器(必须在CP作用下运行)

(3)T、P 端一直设置为 1 即可

(4)Cr 与 LD 都是低电平有效,即在为0时工作

(5)注意在输入端,A端为低位,D 为高位,在输出端也是这样,Qa为低位,Qd为高位

- 对74LS 161 计数器的拓展:

(1)对于异步清零端Cr:可以使用反馈清零法,变成任意进制的计数器

(2)对于同步预置端LD:可以采用反馈预置法来组成任意进制的计数器

(3)在对计数器的状态进行选择的时候,如果采用同步预置端进行反馈控制,那么一切正常,如果采用异步清零端进行反馈的时候,注意,要多加一个过渡态

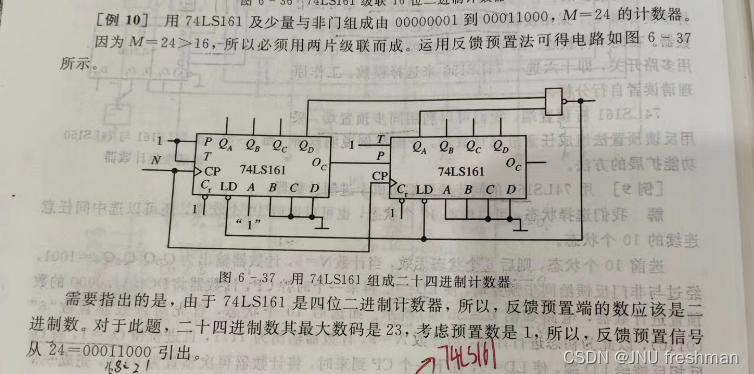

运用多个74LS 161 实现大于16进制的计数

- 注意事项:

(1)左边的A 为最低位,右边的D为最高位,左边的计数器会生成一个Oc 的输出,作为右边计数器的P,反馈信号是控制两个LD 预置端,其余跟一个单独的74LS 161没有区别

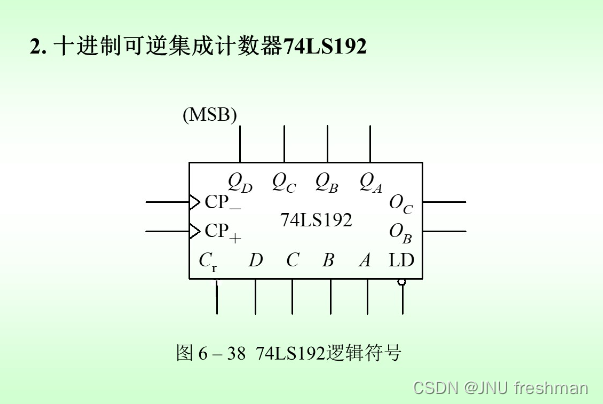

十进制可逆集成计数器 74LS 192

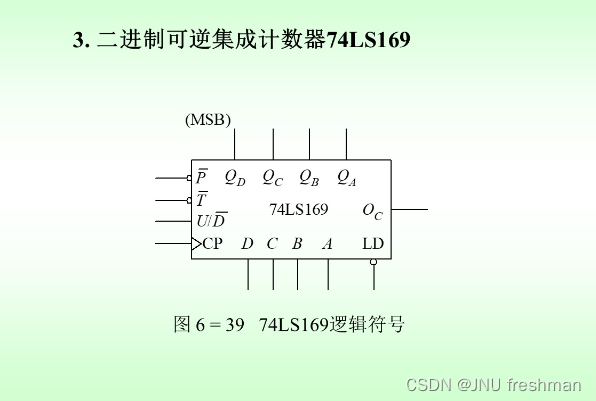

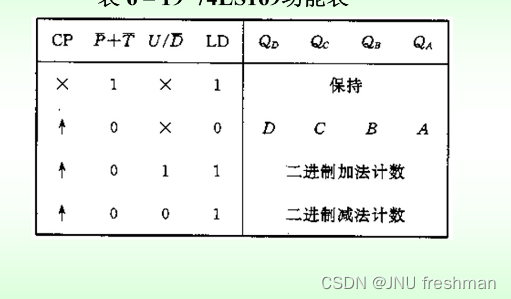

二进制可逆集成计数器74LS169

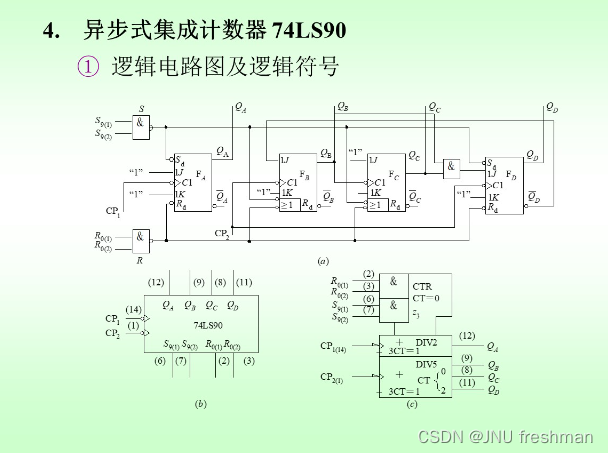

异步集成计数器74LS 90

寄存器与移位寄存器

串行传送与并行传送

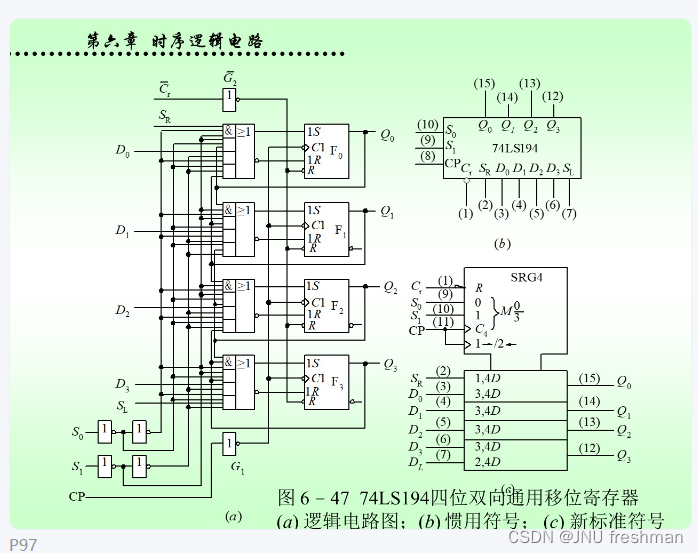

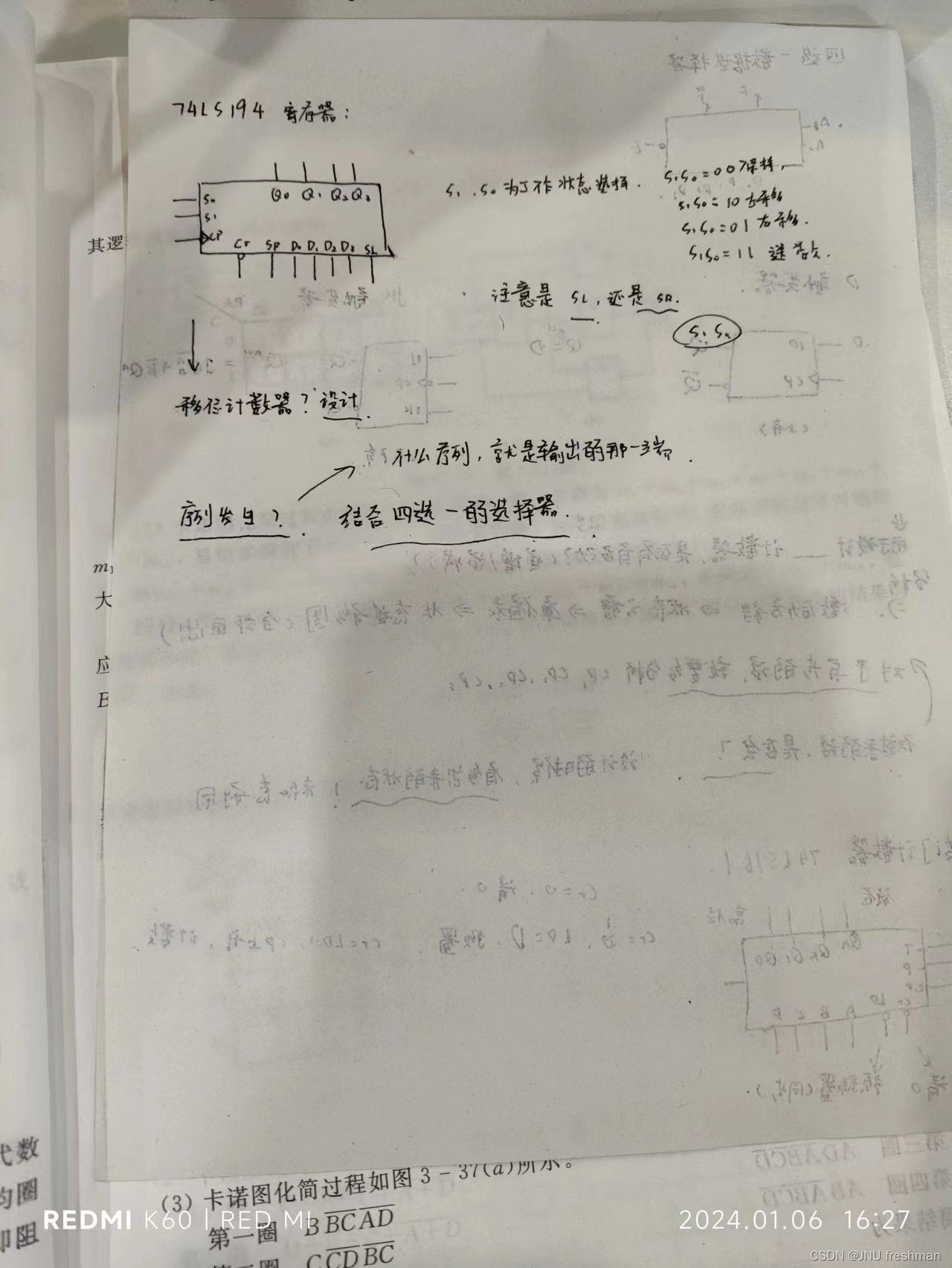

74LS 194 移位寄存器

- 分析:

(1)Cr 为直接清零端,低电平有效

(2)SR为右移串行数据输入端,SL为左移串行数据输入端

(3)CP 为脉冲输入端,上升沿作用

(4)S1,S0为工作状态的选择,S1S0 = 00 为状态的保持,S1S0 = 01 为右移,S1S0 = 10 为左移,S1S0 = 11 为并行送数

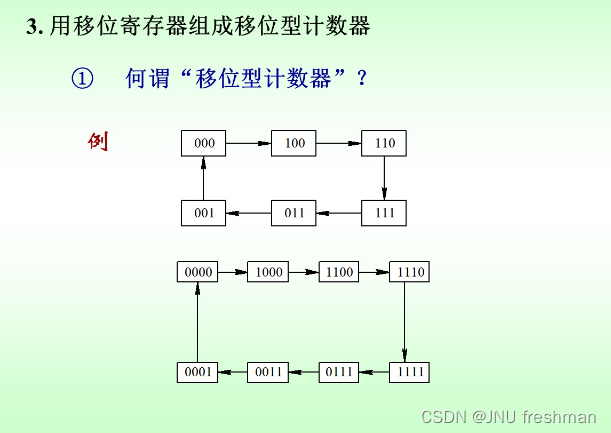

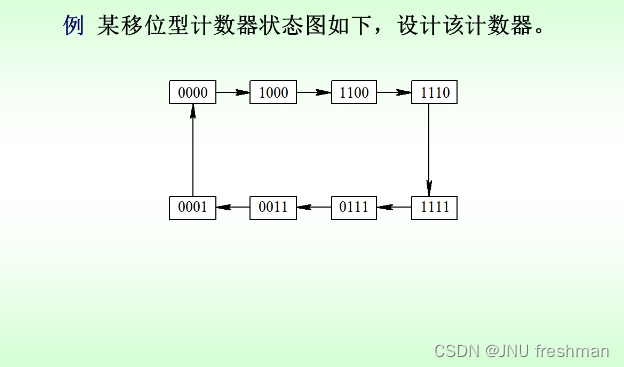

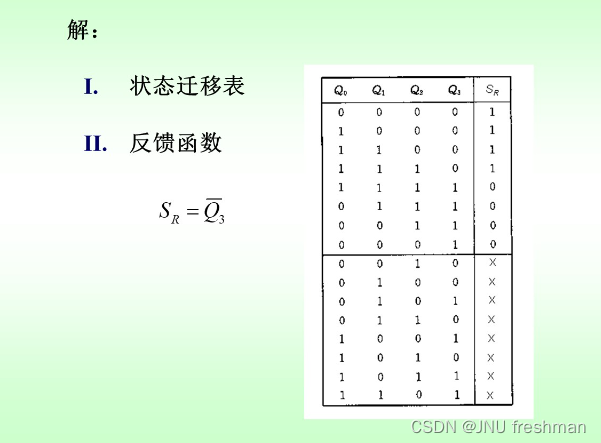

移位寄存器组成移位型计数器

- 设计过程:

(1)从真值表中得到反馈函数(接到SR 还是SL)

f

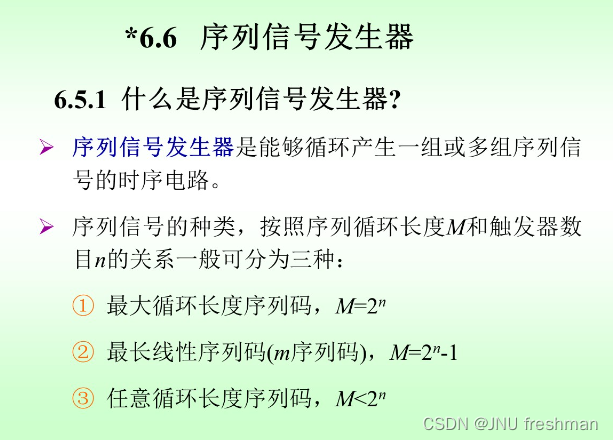

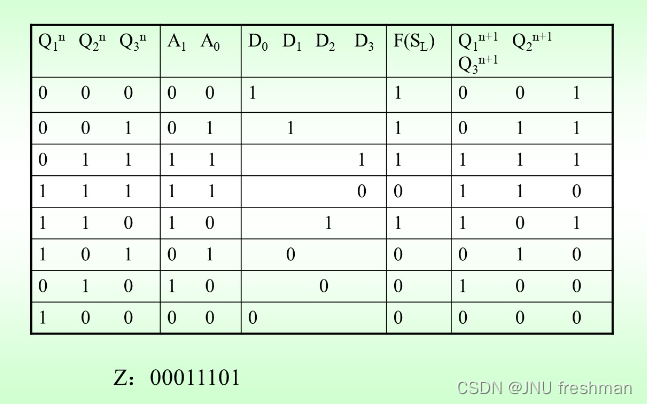

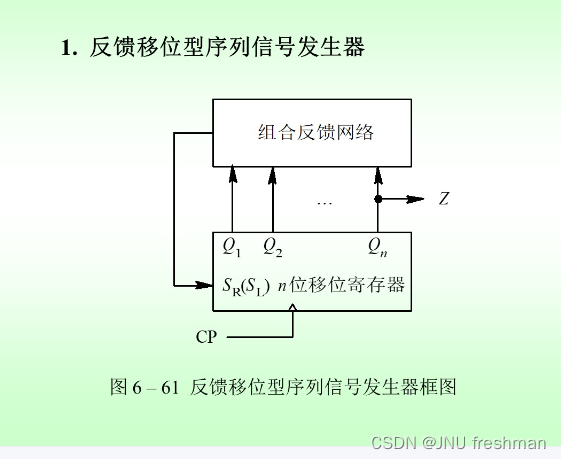

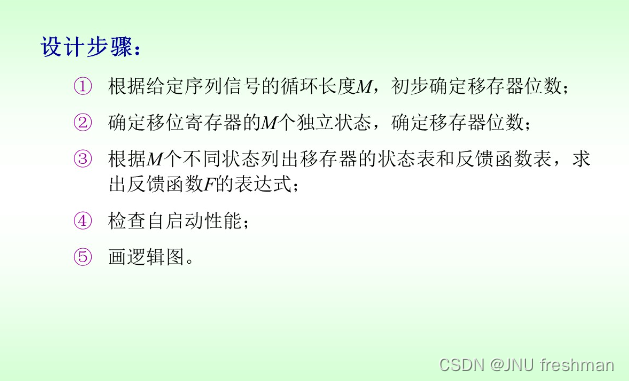

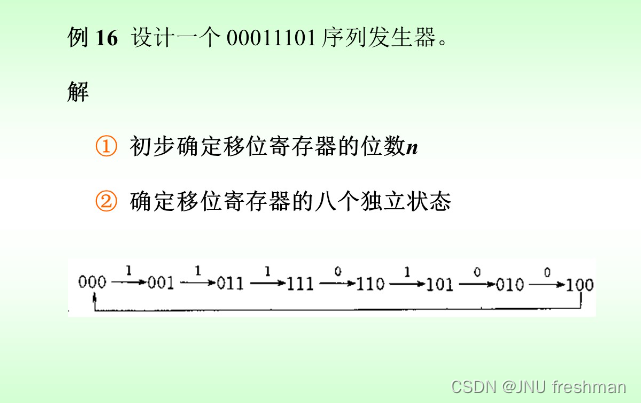

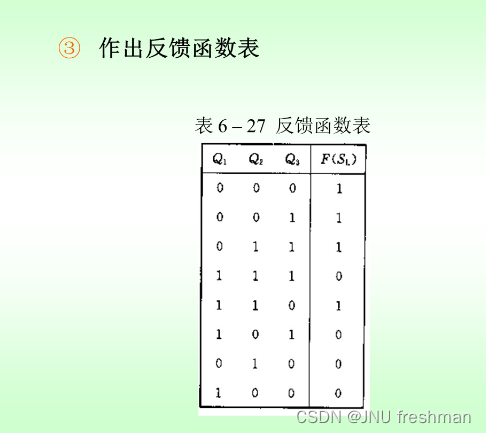

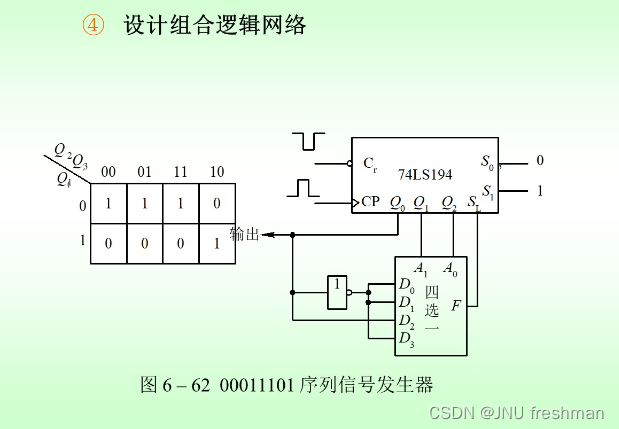

序列信号发生器

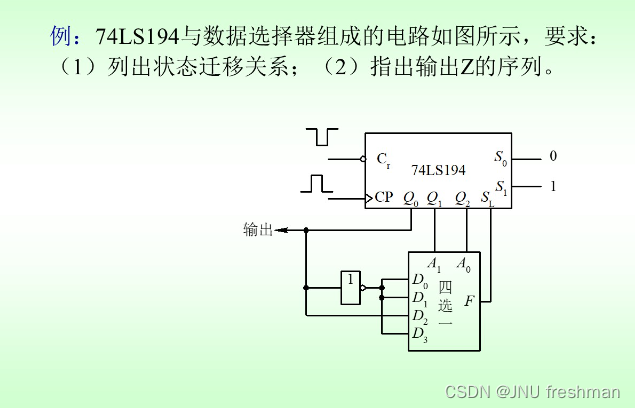

序列信号发生器与选择器的结合

分析状态迁移关系以及输出序列

- 如何理解?

(1)开始的Cr 端有一个下降沿的脉冲信号,也就是74LS 194 的内部的 输出全部为0,由于Q0作为四选一选择器的D0,D1,D2,D3 的赋值,而74LS 194 的Q1,Q2 作为选择器的地址的输入,选择 D0,D1,D2,D3 的一个值作为 输出,也就是作为 寄存器的左移的补充数字

设计

- 对于卡诺图来确定选择器的组合:

(1)先确认了Q1,Q2作为选择器的A1,A0 的地址变量

(2)在卡诺图中,最好将Q2,Q3 放在一起,以上面的为例子,Q2Q3 为00 时选择D0 ,以此类推,然后由于是Q1 进行赋值,结果发现,Q1 = 0时,让D0,D1,D3 都为1 ,为1 时让D2 为1

(3) 按照设计进行画逻辑图

可编程逻辑器件

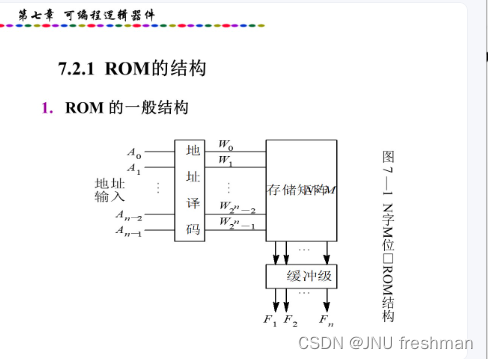

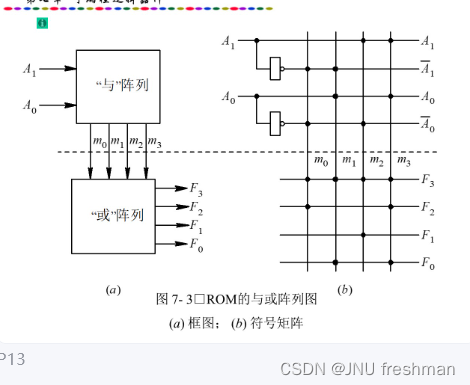

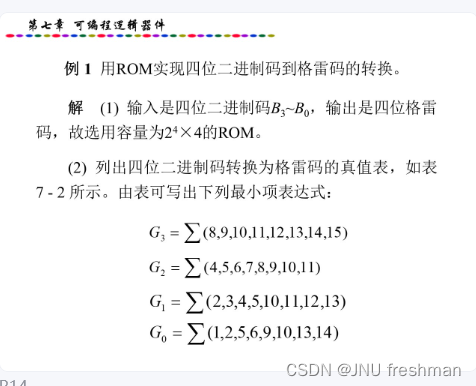

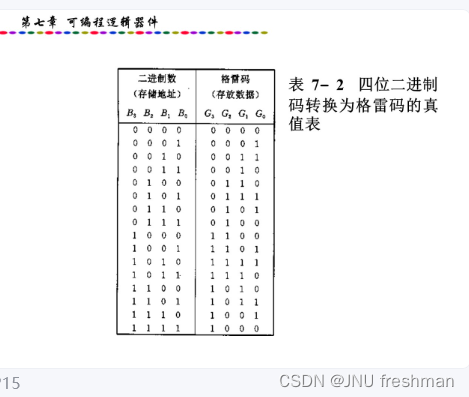

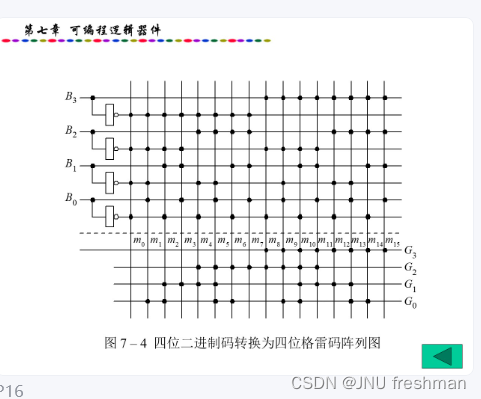

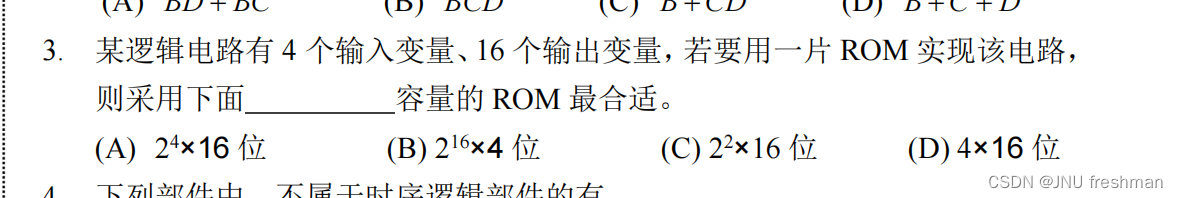

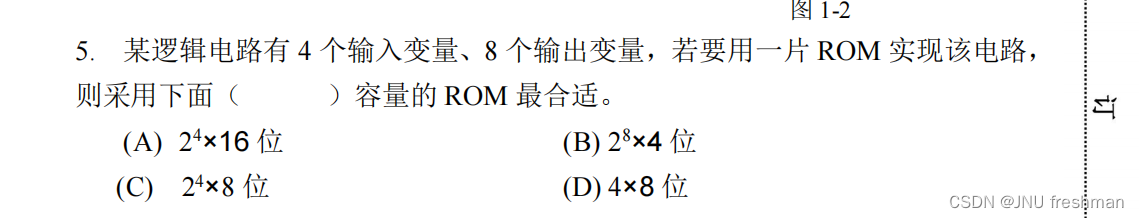

ROM

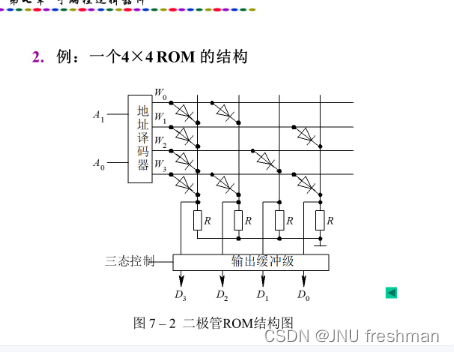

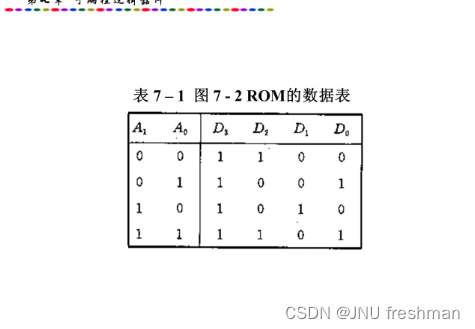

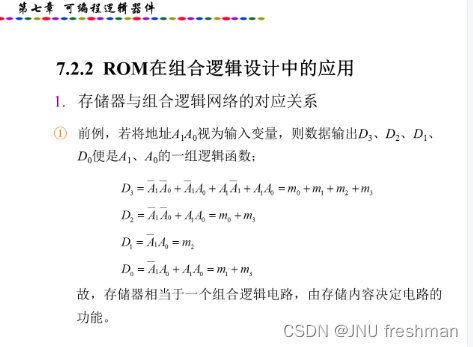

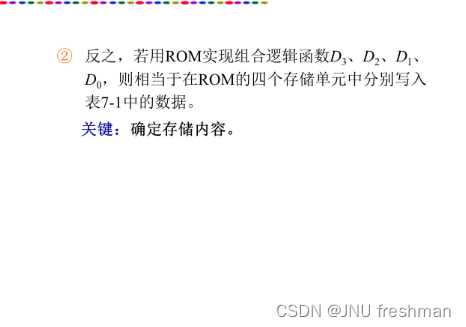

如何理解?输入的变量为地址,会存在该变量以及该变量的一个非,然后每条线竖下来对应m0到m^2n-1 ,相对应的交叉点上画黑点,然后就是下面的表,从上到下就是G3 到 G0 就是输出,按照你的真值表来的,说实话就是横着看,在相对应的最小项上画黑点

选A

总结

7041

7041

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?