概述

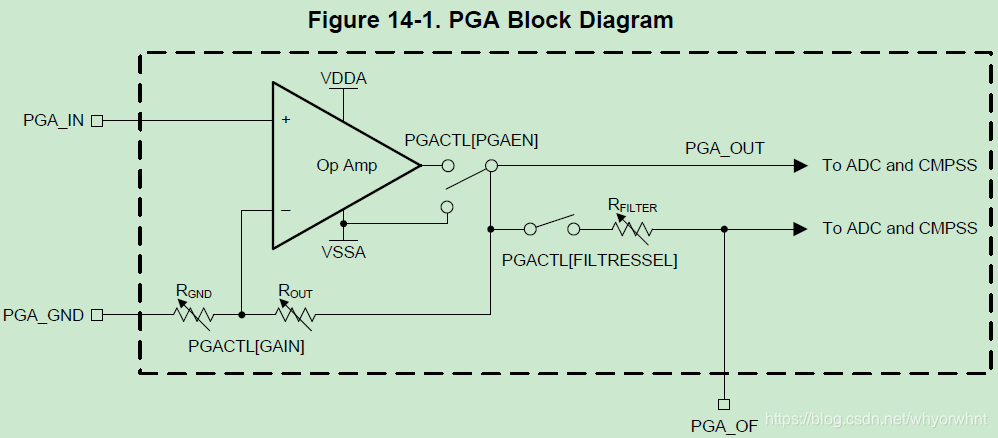

可编程增益放大器(PGA)用于放大输入电压以增加后级ADC和CMPSS模块的动态范围。

集成的PGA有助于降低成本和许多传统上需要外部独立放大器的控制应用的设计工作。片上集成确保PGA与下游ADC和CMPSS模块兼容。软件可选择的增益和滤波器设置使PGA能够适应各种性能需求。

特性:

- 四种可编程增益模式:3x、6x、12x、24x

- 内部由VDDA和VSSA供电

- 基于硬件的微调,以减少偏移和增益误差

- 支持使用PGA_GND接地引脚的开尔文接地连接

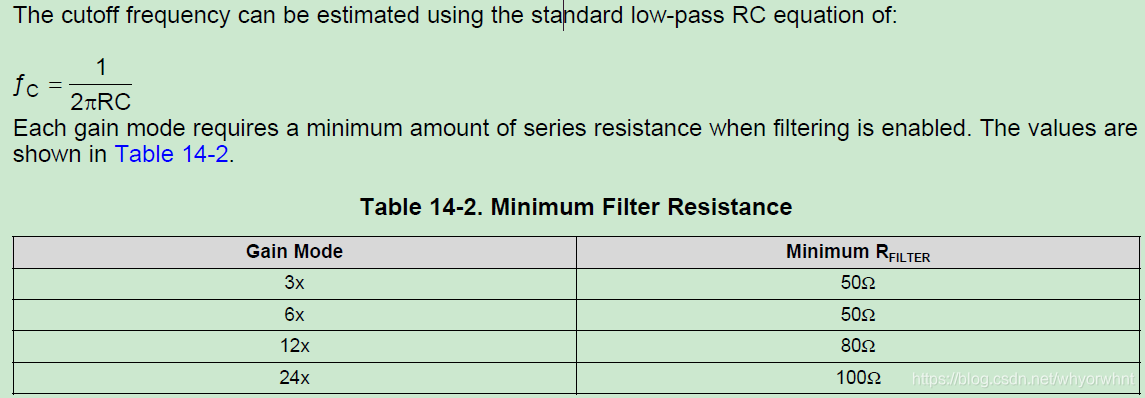

- 嵌入式串联电阻,用于RC滤波

PGA中的有源元件是一个嵌入式运算放大器(运放),它被配置为具有内部反馈电阻的非反相放大器。这些内部反馈电阻值配对以产生软件可选择的电压增益。设备引脚上有三个PGA信号:

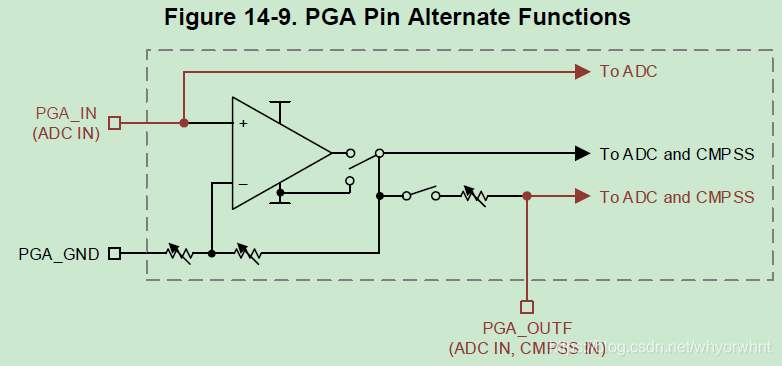

- PGA_IN是PGA运算放大器的正输入,作用在该引脚的信号将被PGA放大。

- PGA_GND是PGA_IN信号的开尔文接地参考。理想情况下,PGA_GND等于VSSA,但是PGA可以容忍来自VSSA的小电压偏移。更多信息请参阅手册。

- PGA_OF支持带RC元件的运算放大器输出滤波。滤波信号可用于通过内部ADC和CMPSS模块进行采样和监控。

PGA_OUT是运放输出的内部信号。可由内部ADC和CMPSS模块采样和监控。

线性增益区的范围需要查看器件手册。

允许在正常运行期间改变增益模式,但在这样做时,应遵守最短的配置调整时间。增益开关设定时间见设备数据手册。

关于外部滤波:

PGA输出可以通过嵌入的串联电阻器路由到引脚,以便对放大的信号进行低通滤波。滤波器电阻可通过PGACTL[filteresel]寄存器字段进行软件选择。PGACTL[filteresel]=0的默认选择将禁用滤波路径。

与其他模拟子系统的配合

PGA与ADC,CMPSS的配合使用,详见手册14.10节。

还可以使用DAC来调整信号的范围,确保PGA运行在最佳线性区。

如果不使用PGA,接地端子应与VSSA相连。

示例 PGA DAC-ADC External Loopback Example

C:\ti\c2000\C2000Ware_3_01_00_00\driverlib\f28004x\examples\pga

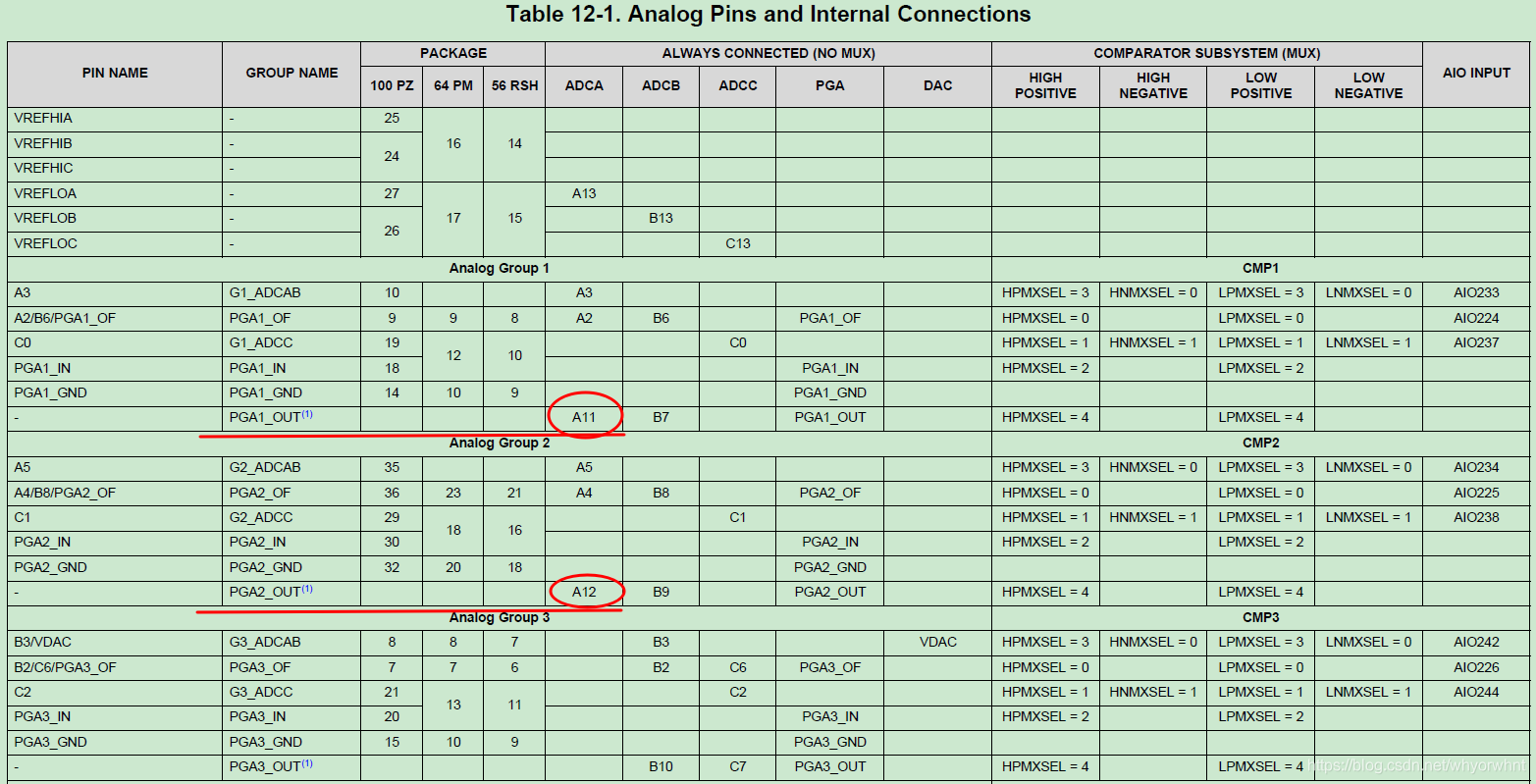

库函数的例程使用DAC输出生成400 mV(它使用内部电压参考)。DAC的输出外部连接到PGA2,用于3x增益放大。使用两个ADC通道分别对来自的DAC输出和PGA2的放大电压输出进行采样。这些信号是ADC从内部连接的。

LaunchPad外部接线:DACA_OUT(A0)连接PGA2_IN(A3)

该例程没有使用RC滤波器。

TI提供的这个例程似乎配置错了,程序描述和代码里使用的是PGA2。但ADC却采样了PGA1……

实验效果:

贴一份改过的代码:

//#############################################################################

//

// FILE: pga_ex1_dac_adc_ext_loopback.c

//

// TITLE: PGA DAC-ADC External Loopback Example.

//

//! \addtogroup driver_example_list

//! <h1>PGA DAC-ADC External Loopback Example</h1>

//!

//! This example generates 400 mV using the DAC output (it uses an internal

//! voltage reference). The output of the DAC is externally connected to PGA2

//! for a 3x gain amplification. It uses two ADC channels to sample the

//! DAC output and the amplified voltage output from PGA2. The ADC is connected

//! to these signals internally.

//!

//! \b External \b Connections on Control Card\n

//! - Connect DACA_OUT (Analog Pin A0) to PGA2_IN.

//!

//! \b External \b Connections on Launchpad\n

//! - Connect DACA_OUT (Analog Pin A0) to PGA2_IN (Analog Pin A3).

//!

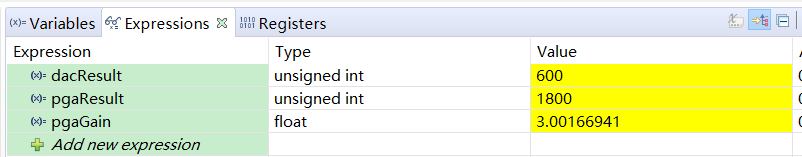

//! \b Watch \b Variables \n

//! - \b dacResult - The DAC output voltage.

//! - \b pgaResult - The amplified DAC voltage.

//! - \b pgaGain - The ratio of the amplified DAC voltage to the original

//! DAC output. This should always read a value of ~3.0.

//!

//

//#############################################################################

// $TI Release:

// $Release Date:

// $Copyright:

//#############################################################################

//

// Included Files

//

#include "driverlib.h"

#include "device.h"

//

// Globals

//

volatile uint16_t dacResult;

volatile uint16_t pgaResult;

float pgaGain;

//

// Function Prototypes

//

void initPGA(void);

void initDAC(void);

void initADC(void);

void initADCSOC(void);

//

// Main

//

void main(void)

{

//

// Initialize device clock and peripherals

//

Device_init();

//

// Disable pin locks and enable internal pull ups.

//

Device_initGPIO();

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Initialize PGA, DAC, and ADC

//

initPGA();

initDAC();

DAC_setShadowValue(DACA_BASE, 600U);

initADC();

initADCSOC();

DEVICE_DELAY_US(3000U);

//

// Enable Global Interrupt (INTM) and real time interrupt (DBGM)

//

EINT;

ERTM;

//

// Force ADC conversion

//

ADC_forceSOC(ADCA_BASE, ADC_SOC_NUMBER0);

ADC_forceSOC(ADCA_BASE, ADC_SOC_NUMBER1);

//

// Loop indefinitely

//

while(1)

{

//

// Check if conversion is complete

//

if(ADC_getInterruptStatus(ADCA_BASE, ADC_INT_NUMBER1))

{

//

// Acknowledge flag

//

ADC_clearInterruptStatus(ADCA_BASE, ADC_INT_NUMBER1);

dacResult = ADC_readResult(ADCARESULT_BASE, ADC_SOC_NUMBER0);

pgaResult = ADC_readResult(ADCARESULT_BASE, ADC_SOC_NUMBER1);

pgaGain = (float)pgaResult / (float)dacResult;

//

// Force ADC conversion

//

ADC_forceSOC(ADCA_BASE, ADC_SOC_NUMBER0);

ADC_forceSOC(ADCA_BASE, ADC_SOC_NUMBER1);

}

}

}

//

// initADC - Configure ADC

//

void initADC(void)

{

//

// Set the voltage reference

//

// NOTE:

// VREFHI pin must not be driven by an external reference

// voltage. Disconnect any external reference before proceeding

//

ESTOP0;

ADC_setVREF(ADCA_BASE, ADC_REFERENCE_INTERNAL, ADC_REFERENCE_3_3V);

//

// Set ADCCLK divider to /4

//

ADC_setPrescaler(ADCA_BASE, ADC_CLK_DIV_4_0);

//

// Flag is raised at the end of conversion

//

ADC_setInterruptPulseMode(ADCA_BASE, ADC_PULSE_END_OF_CONV);

//

// Enable ADC

//

ADC_enableConverter(ADCA_BASE);

DEVICE_DELAY_US(1000U);

}

//

// initADCSOC - Configure ADC SOCs

//

void initADCSOC(void)

{

//

// Convert DACA output

//

ADC_setupSOC(ADCA_BASE, ADC_SOC_NUMBER0,

ADC_TRIGGER_SW_ONLY, ADC_CH_ADCIN0, 10U);

//

// Convert PGA2 output 这里由11改为12

//

ADC_setupSOC(ADCA_BASE, ADC_SOC_NUMBER1,

ADC_TRIGGER_SW_ONLY, ADC_CH_ADCIN12, 10U);

//

// Configure ADC interrupt status flags

//

ADC_setInterruptSource(ADCA_BASE, ADC_INT_NUMBER1, ADC_SOC_NUMBER1);

ADC_enableInterrupt(ADCA_BASE, ADC_INT_NUMBER1);

ADC_clearInterruptStatus(ADCA_BASE, ADC_INT_NUMBER1);

}

//

// initDAC - Configure DAC

//

void initDAC(void)

{

//

// Set the DAC gain to 2

//

DAC_setGainMode(DACA_BASE, DAC_GAIN_TWO);

//

// Use ADC voltage reference

//

DAC_setReferenceVoltage(DACA_BASE, DAC_REF_ADC_VREFHI);

//

// Load count value for DAC on next SYSCLK

//

DAC_setLoadMode(DACA_BASE, DAC_LOAD_SYSCLK);

//

// Enable DAC output

//

DAC_enableOutput(DACA_BASE);

}

//

// initPGA - Configure PGA2 gain

//

void initPGA(void)

{

//

// Set a gain of 3 to PGA2

//

PGA_setGain(PGA2_BASE, PGA_GAIN_3);

//

// No filter resistor for output

//

PGA_setFilterResistor(PGA2_BASE, PGA_LOW_PASS_FILTER_DISABLED);

//

// Enable PGA2

//

PGA_enable(PGA2_BASE);

}

2323

2323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?