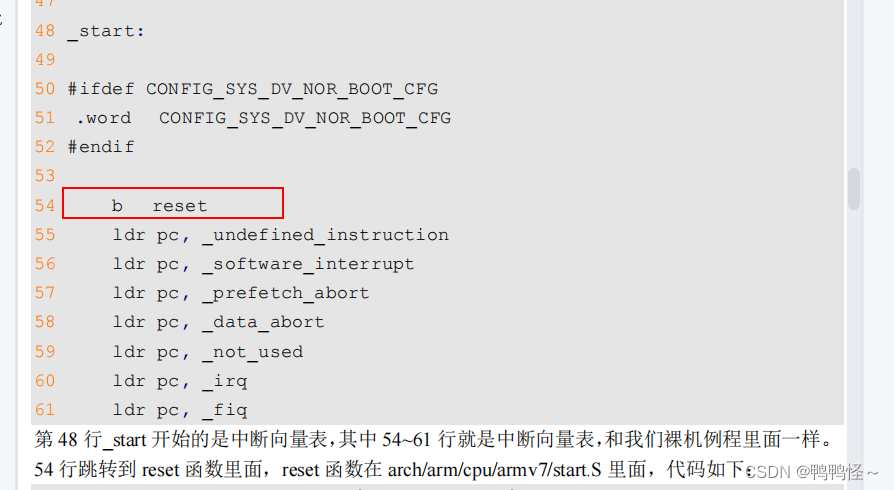

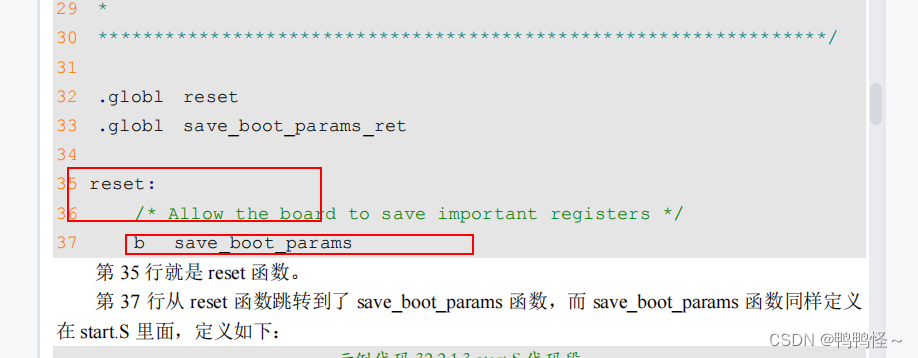

1.从 u-boot.lds 中已经知道了入口点是 arch/arm/lib/vectors.S 文件中的_start,

然后从_start开始分析:

38 save_boot_params_ret:

39 /*

40 * disable interrupts (FIQ and IRQ), also set the cpu to SVC32

41 * mode, except if in HYP mode already

42 */

43 mrs r0, cpsr /*读取寄存器 cpsr 中的值,并保存到 r0 寄存器中*/

44 and r1, r0, #0x1f @ mask mode bits

45 teq r1, #0x1a @ test for HYP mode

46 bicne r0, r0, #0x1f @ clear all mode bits

47 orrne r0, r0, #0x13 @ set SVC mode

48 orr r0, r0, #0xc0 @ disable FIQ and IRQ

49 msr cpsr,r0

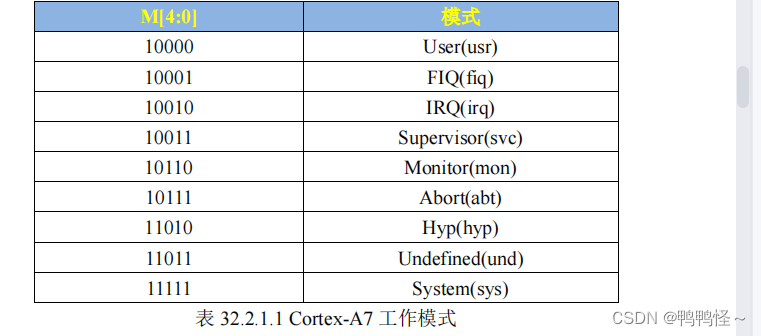

第 44 行,将寄存器 r0 中的值与 0X1F 进行与运算,结果保存到 r1 寄存器中,目的就是提

取 cpsr 的 bit0~bit4 这 5 位,这 5 位为 M4 M3 M2 M1 M0,M[4:0]这五位用来设置处理器的工作

模式。

第 45 行,判断 r1 寄存器的值是否等于 0X1A(0b11010),也就是判断当前处理器模式是否

处于 Hyp 模式。

第 46 行,如果 r1 和 0X1A 不相等,也就是 CPU 不处于 Hyp 模式的话就将 r0 寄存器的

bit0~5 进行清零,其实就是清除模式位

第 47 行,如果处理器不处于 Hyp 模式的话就将 r0 的寄存器的值与 0x13 进行或运算,

0x13=0b10011,也就是设置处理器进入 SVC 模式。

第 48 行,r0 寄存器的值再与 0xC0 进行或运算,那么 r0 寄存器此时的值就是 0xD3,cpsr

的 I 为和 F 位分别控制 IRQ 和 FIQ 这两个中断的开关,设置为 1 就关闭了 FIQ 和 IRQ! 第 49 行,将 r0 寄存器写回到 cpsr 寄存器中。完成设置 CPU 处于 SVC32 模式,并且关闭FIQ 和 IRQ 这两个中断。

代码段从u-boot.lds的_start入口点开始,通过读取并操作cpsr寄存器来切换CPU模式。首先,检查是否处于HYP模式,如果不是,则清除模式位并设置为SVC模式,同时禁用FIQ和IRQ中断。这一过程确保系统在安全模式下运行。

代码段从u-boot.lds的_start入口点开始,通过读取并操作cpsr寄存器来切换CPU模式。首先,检查是否处于HYP模式,如果不是,则清除模式位并设置为SVC模式,同时禁用FIQ和IRQ中断。这一过程确保系统在安全模式下运行。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?