缘由我有电路原理图,想用proteus仿真,但是数码管不亮-嵌入式-CSDN问答

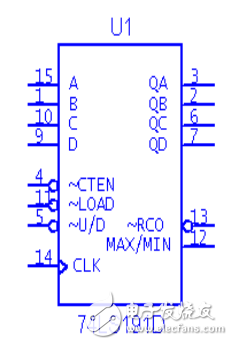

74LS191为可预置的四位二进制加/减法计数器

74ls191引脚功用

RCO进位/借位输出端

MAX/MIN进位/借位输出端

CTEN计数操控端

QA-QD计数输出端

U/D计数操控端

CLK时钟输入端

LOAD异步并行置入端(低电平有用)。

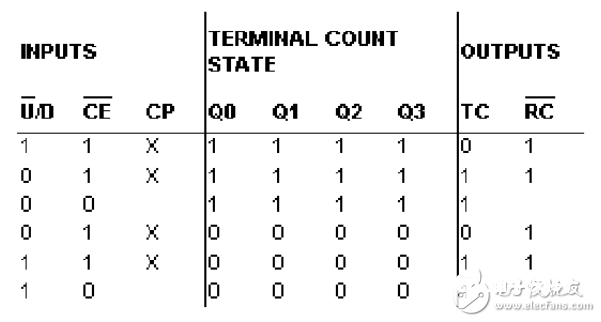

74LS191逻辑功用

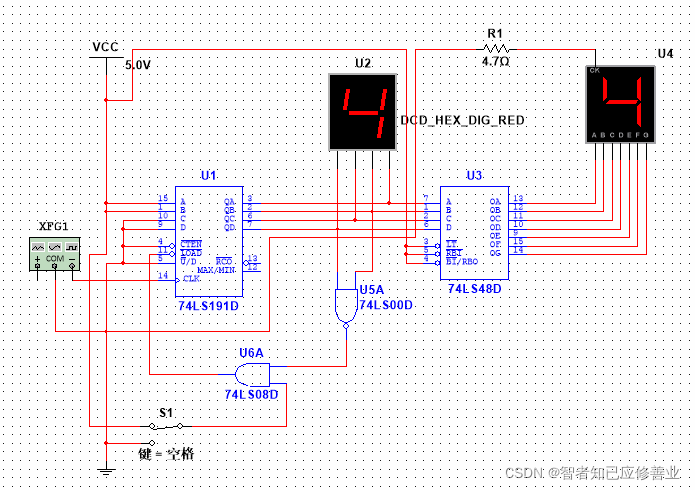

后一个数码管选型看顶上一端CK另一种是CA。下图显示3-9循环。

下图预置3从3-9循环显示

下图预置3从3-9再从9-3循环显示,必需使用4端全信号,否则可能与其它字段信号混淆.

只有3与7的信号有重复因此需要全信号做区别9信号就不用全信号即可.

文章讲述了作者想要用Proteus软件对74LS191进行仿真,探讨了74LS191各个引脚的功能,如计数控制、时钟输入和数码管选择,以及如何设置3-9循环和全信号以避免混淆。

文章讲述了作者想要用Proteus软件对74LS191进行仿真,探讨了74LS191各个引脚的功能,如计数控制、时钟输入和数码管选择,以及如何设置3-9循环和全信号以避免混淆。

3708

3708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?