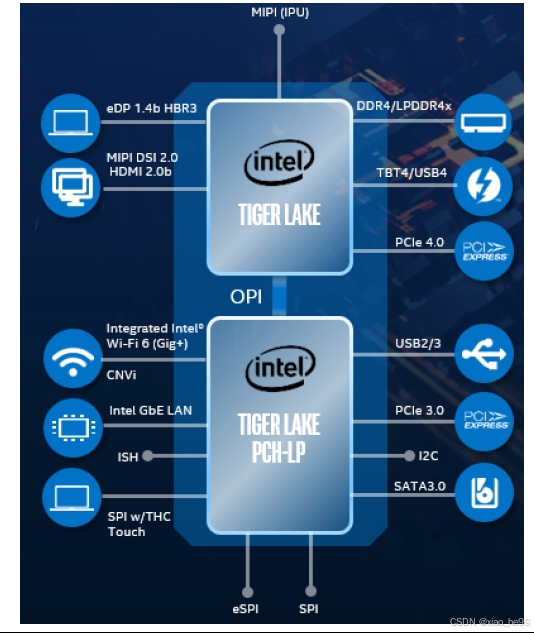

Intel Tiger lake芯片架构和Lunar lake芯片架构 如下所示:

| Tiger lake UP3 | Lunar lake | 备注 | ||

| Display | eDP | 1.4b HBR3 | 1.5 HBR3 | 1.4b:支持 4K 分辨率(3840×2160) 1.5:支持 8K 分辨率(7680×4320) |

| interface | HDMI | 2.0b | 2.1 | 2.0b:4K 2.1:8K |

| DP | 1.4a | 2.1 | 1.4a:支持 8K 60Hz\30Hz、4K 120Hz\240Hz、2K(2560×1440) 240Hz等显示规格 2.1:支持 8K 120Hz\60Hz 的显示外,还能支持 10K(10240X4320)、16K(15360x8640) 等超高分辨率显示 | |

| TBT4 | 4个 | 3个 | ||

| WLAN | wifi | Wifi 6/6E | Wifi 7 6E | wifi6/6e:ax模 wifi7:be模 |

| BT | BT5.2 | BT5.4 | ||

| Gbe LAN | I219-LM | I219-LM | ||

| Camera | MIPI CSI | CSI-2 IPU6se | CSI-2 IPU7 | IPU(Image Processing Unit)即图像处理器 |

| memory | DDR | DDR4/LPDDR4 | LPDDR5 (Mop) | Lunar Lake 芯片将 16/32GB 的 LPDDR5X RAM 直接集成在封装内(即Mop技术,内存封装),根据英特尔的说法,这一变化使得数据传输的负载(信号衰减,延迟增加,功耗增加等)降低了大约 40%,即Mop技术使得性能,能效,稳定性增强 |

| PCIE | PCIE4.0X4 PCIE3.0X12 | PCIE5.0X4 PCIE4.0X4 | 3.0:有3组只用于PCIE信号,其他9组都是复用其他信号如USB,sata,LAN等 PCIE3.0:8GT/s PCIE4.0:16GT/s PCIE5.0:32GT/s | |

| USB | USB3 | 4个 | 2个 | |

| USB2.0 | 10个 | 6个 | ||

| NPU | 无 | 第四代 | Tiger lake:处理复杂AI图形任务相对有限 Lunar lake: GPU 的 AI 算力可达 67TOPS(每秒执行67 万亿次基本运算),XPU 总 AI 算力 120TOPS (NPU:Neural Processing Unit 神经处理单元) | |

| GPU | Xe架构 | 8个Xe2核心 | Xe2架构图形性能相比前代 Xe 架构提高了 1.5 倍 | |

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?