一 内存接口概念

- 关于CPU内存类设备

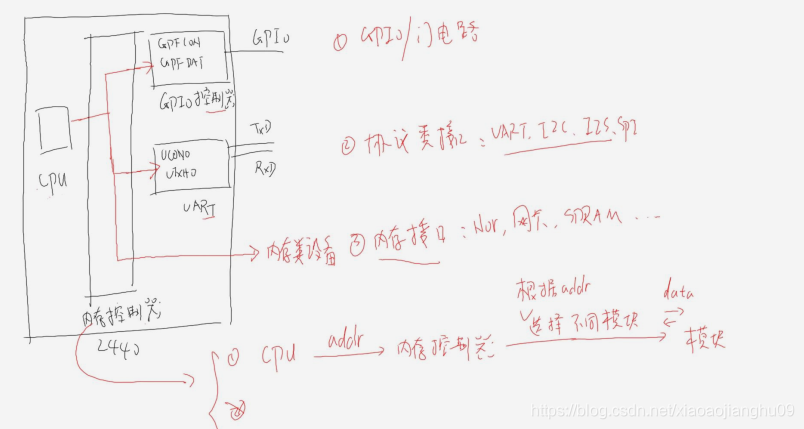

①CPU访问SOC芯片内部各个IP分为三类:

GPIO/门电路,

协议类接口(UART I2C I2S SPI NAND),

内存类接口(NOR 网卡 SDRAM EMIF…)。

②CPU访问SOC芯片内部各个IP的方式(GPIO/门电路 协议类接口):

CPU发送address -> 内存控制器 -> 内存控制器根据address选择不同外围IP -> 内存控制器发送数据 -> 对应的IP controller

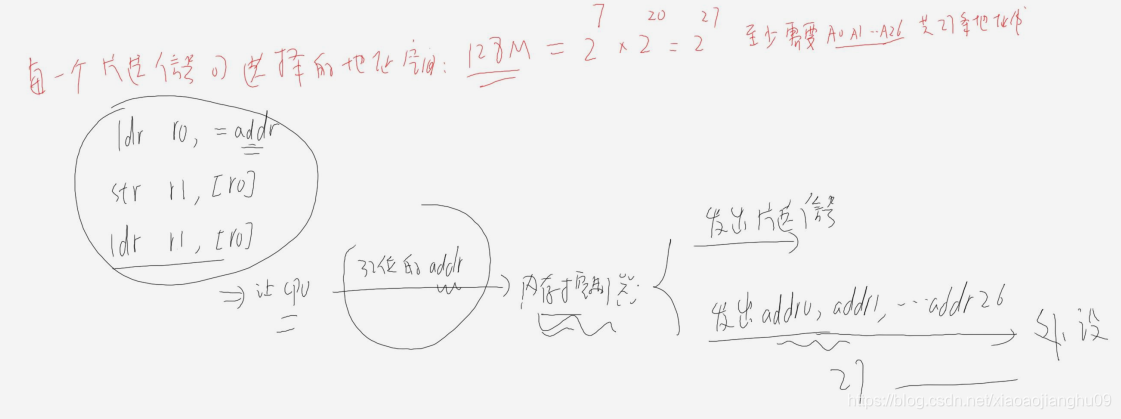

③CPU访问内存类接口设备

CPU把地址和数据直接放到外围设备的地址总线/数据总线。

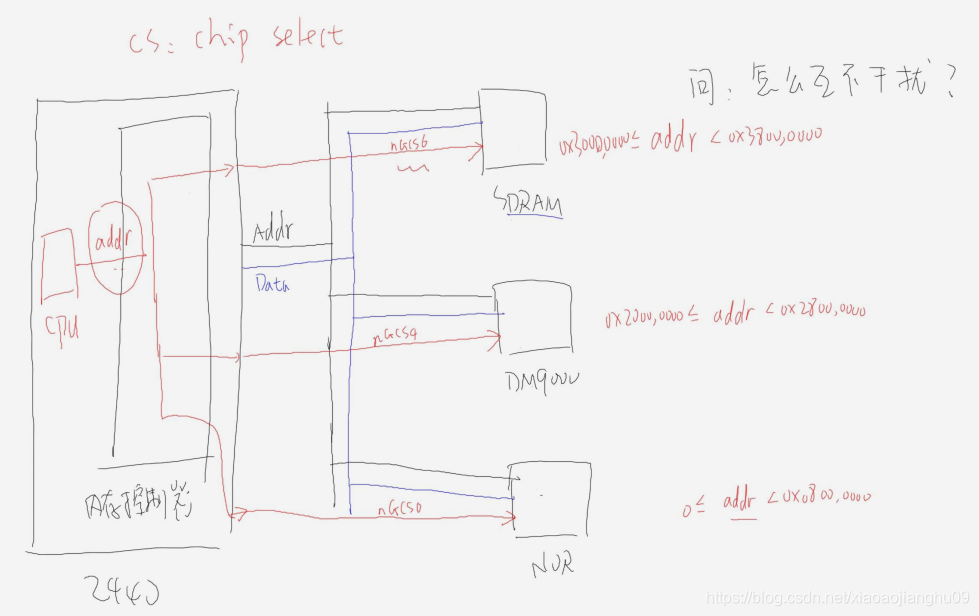

多个外围设备共用地址总线和数据总线,如何互不干扰?

每个外围设备都有私有的CS信号,SOC芯片内部不同的CS信号对应不同的bank;

不同的地址区域(bank)对应不同的CS由SOC芯片的内存控制器控制;

由于CPU是32bit,所以发出的地址也为32bit

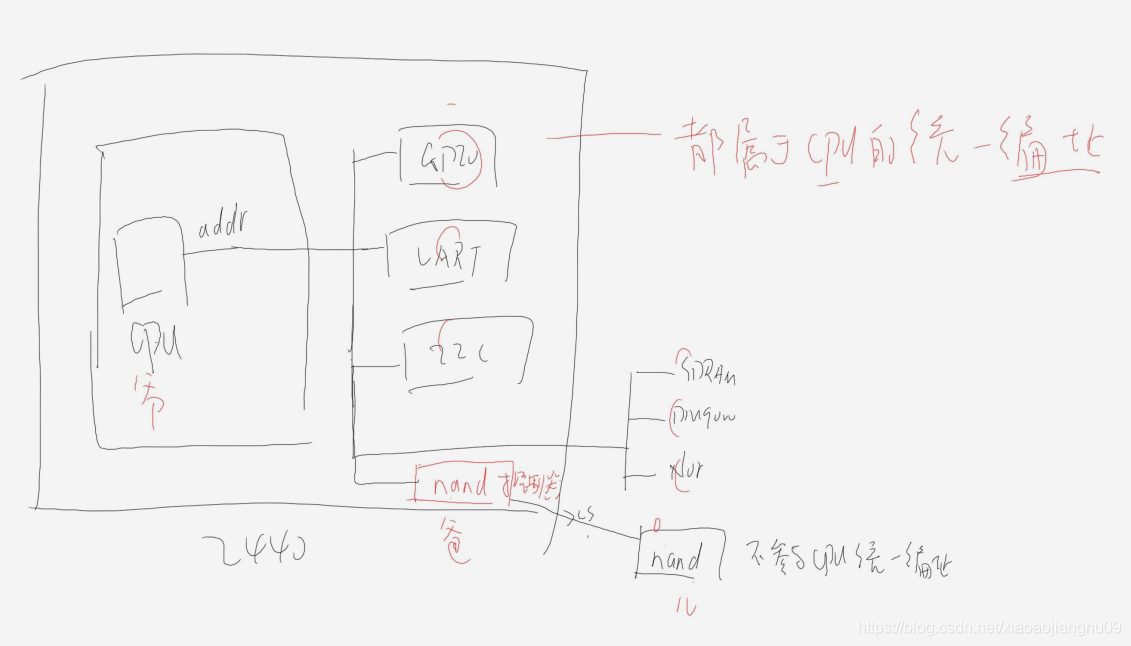

④CPU访问nand芯片的特殊性

外围的nand设备的address是由nand控制器发出的,不是CPU直接发出的。所以nand不属于CPU统一编址。

二 内存接口不同位宽概念

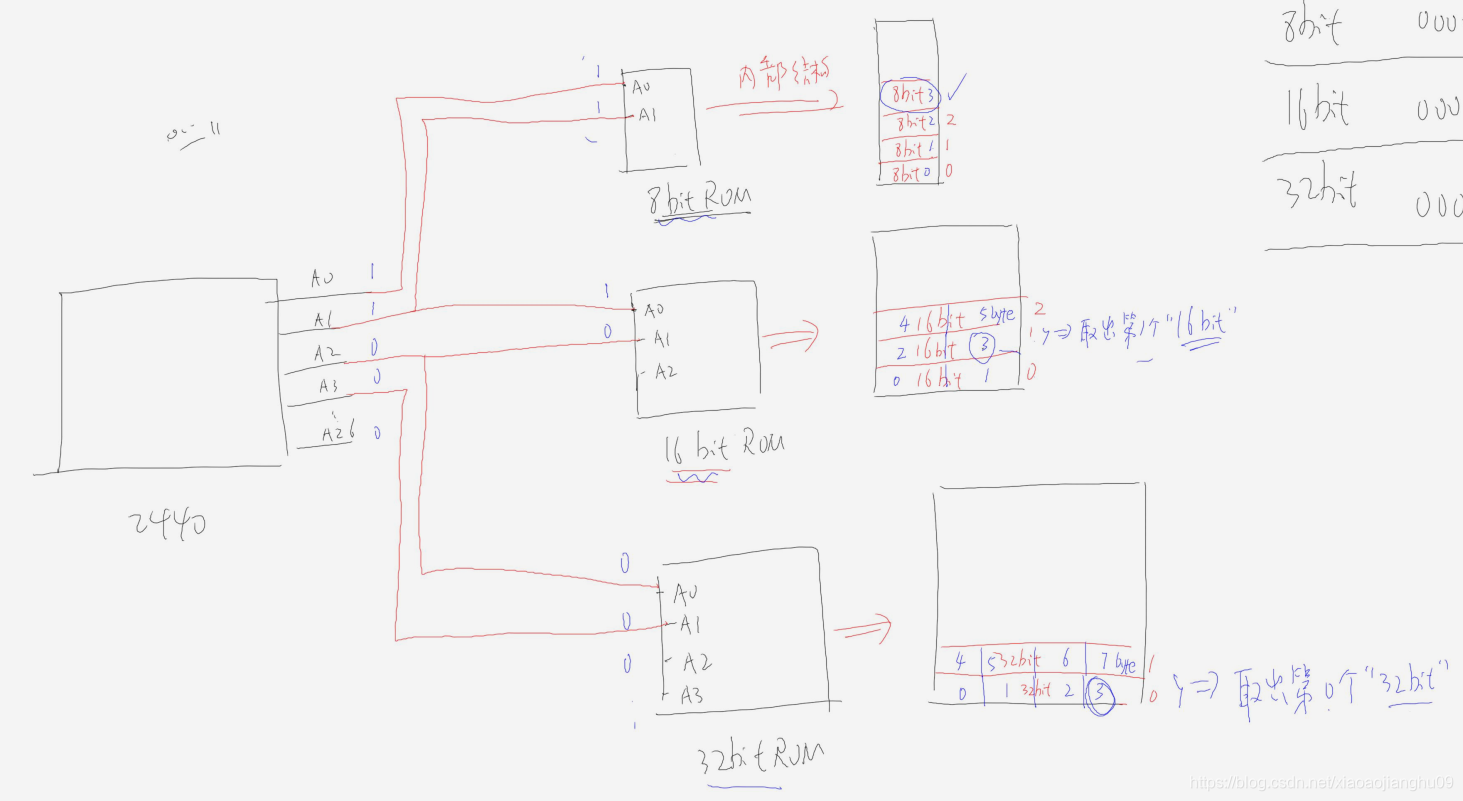

- 不同数据线宽度对应的地址线接法不同,具体如下:

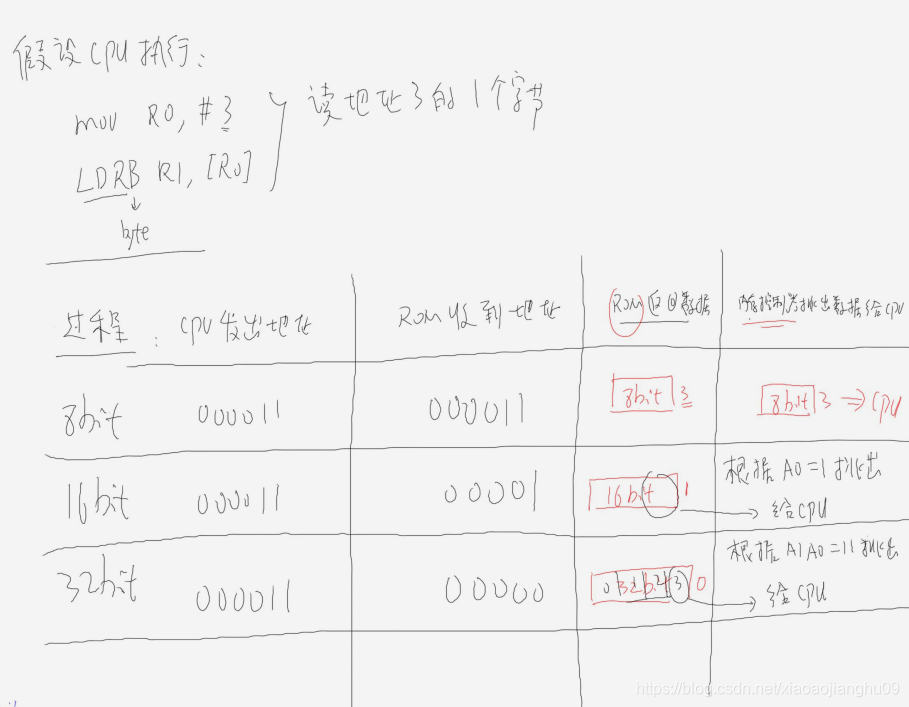

- 如下图:假设CPU执行读取地址3的1byte指令?

CPU发出地址:

A26 A25~A3=0X00

A2 A1 A0=0 1 1

按照上面的接法:不同位宽ROM接收到的地址

8bit ROM addr=0x3;//取出第3个的数据

16bit ROM addr=0x1;//取出第1个数据

32bit ROM addr=0x0;//取出第0个数据

得到上述数据之后,由内存控制器把CPU所需要的数据挑出!

如何挑出呢?根据未连接的地址线挑出

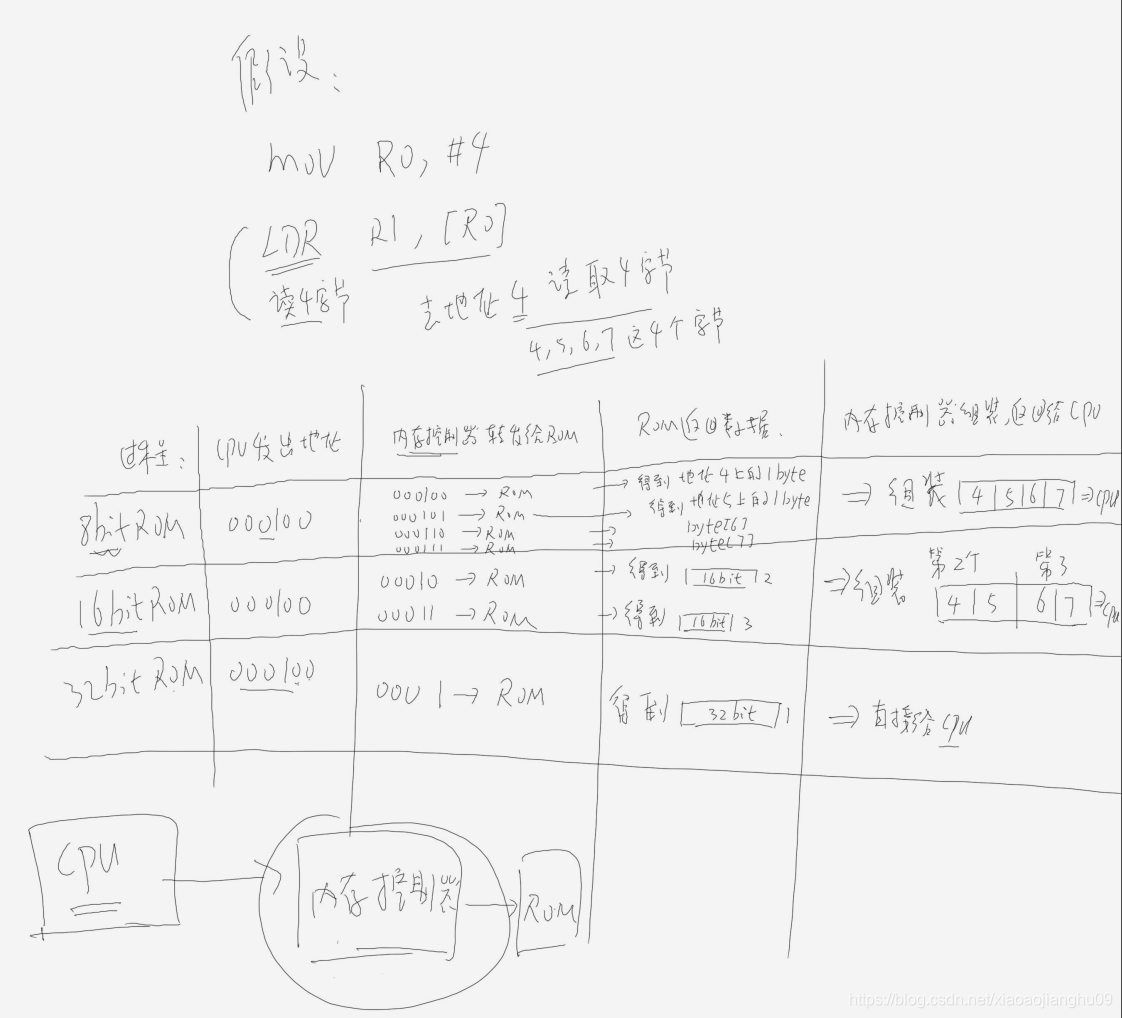

- 如下图:假设需要读取地址4的4bytes数据?

由于CPU需要获取4bytes数据,所以对于不同的位宽的ROM,内存控制器发送地址和数据拼接操作是不同的。

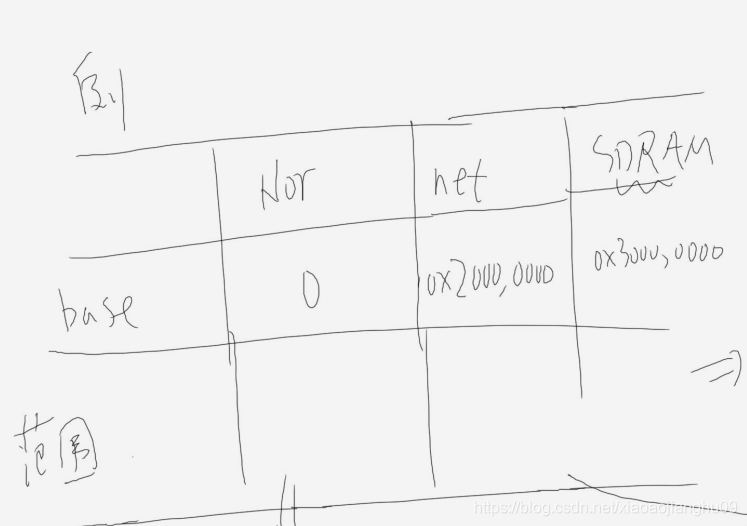

三 芯片访问地址确定

- 根据芯片所接的片选信号确定基地址:

如下图:NOR NET SDRAM就连接不同的CS信号,根据芯片手册得到不同的地址范围。

- 根据芯片所接地址线确定范围:

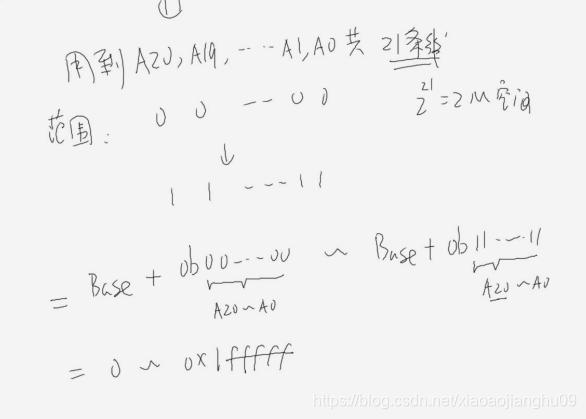

①NOR:使用A20~A0共21根地址线

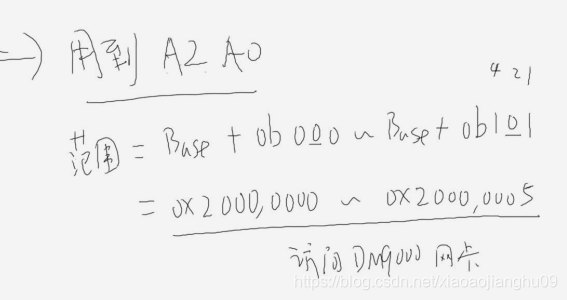

②net:使用A2和A0两根地址线

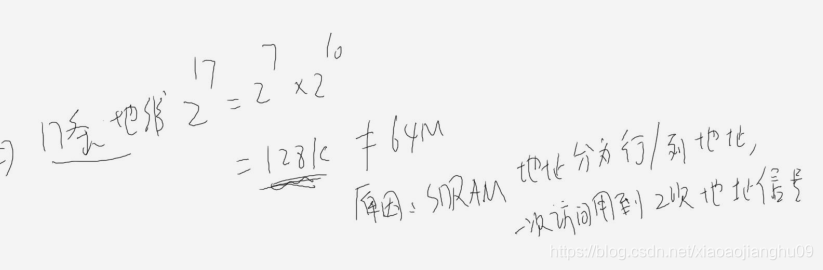

③SDRAM:使用17根地址线

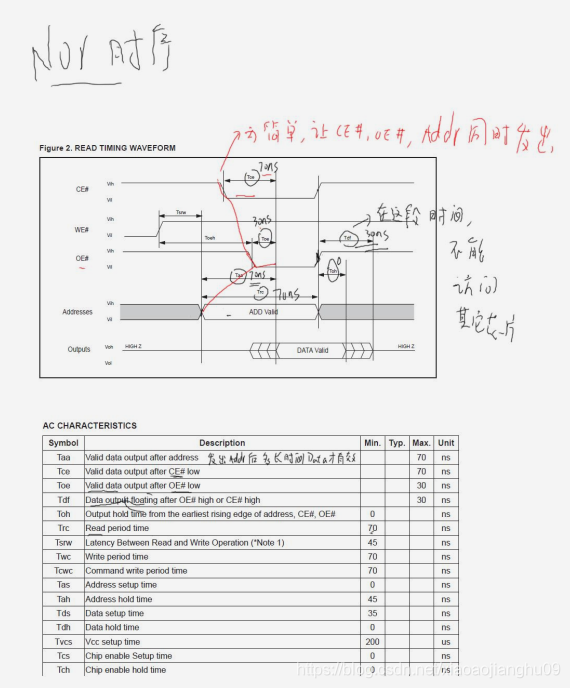

四 芯片访问时序图

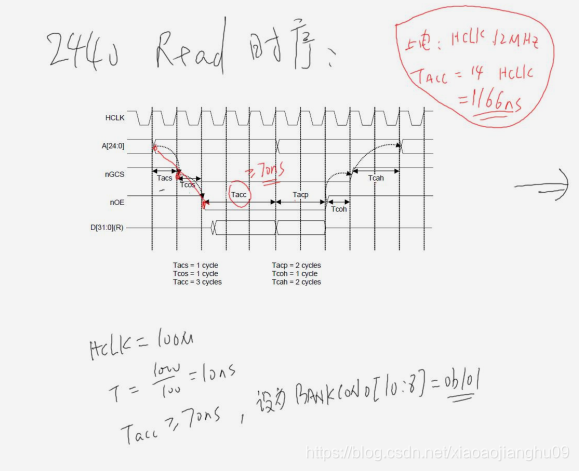

- 2440的读时序图

- 某个NOR flash的时序图

Taa:addr信号发出后多长时间数据有效

Tce:CE信号有效后多长时间数据有效

Toe:OE信号有效后多长时间数据有效

Tdf:OE信号或者CE信号无效后,数据线无法回到高阻状态的时间

Toh:OE信号或者CE信号无效后,数据保持时间

Trc:读周期最短时间

384

384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?