概述

状态寄存器又称cpsr,是cpu运算器的一部分。主要存放两类信息:

1、存放当前指令执行结果的各种状态或条件码,结果是否为负、是否为

0、是否进位、是否溢出;

2、存放控制信息,有终端标志位、跟踪标志位。

cpsr寄存器为32位寄存器,低8位为控制位,高4位为条件标志位。具体功能如下:

| 位数 | 标识 | 描述 |

|---|---|---|

| 31 | N | 符号标志位 当两个有符号整数运算时,结果为负N=1,结果为正N=0 |

| 30 | Z | 零标志位 表示运算结果是否为零,如果为零 Z=1,不为零Z=0 |

| 29 | C | 进位标志位 ①加法运算中,产生进位C=1,否则C=0; ②减法运算中,产生借位C=0,否则C=1 |

| 28 | V | 溢出标志位 有符号数据运算中,超出机器所能识别的范围,称为溢出。 正+正=负 溢出、负+负=正 溢出、正+负=正/负(不可能溢出) |

| 27~8 | 保留位 | |

| 7 | I | 中断禁止标志位 I=1时禁止IRQ中断 |

| 6 | F | 快速中断禁止标志位 F=1时禁止FIQ中断 |

| 5 | T | 控制标志位 T=0表示执行ARM指令 T=1表示执行Thumb指令 |

| 4~0 | M4~M0 | M控制位 可访问的寄存器,处理器模式 |

以上标志位,在逆向中我们只关注NZCV标志位即可,其他标志位相对底层,在单片机开发中比较常见,如51单片机中NZCV位都有,只是位置不一样,M位确定定时器模式(13位、16位计数器)。

标志位验证

上面是CPU相关文档中对寄存器的描述,下面验证一下寄存器值是否和描述一致。

创建一个iOS的App工程,在主函数main()中增加一个判断条件并输出打印,在条件判断出下断点。代码如下:

int main(int argc, char * argv[]) {

int arg1 = 1.0;

int arg2 = 2.0;

if (arg1 == arg2) {

NSLog(@"相等");

} else {

NSLog(@"不相等");

}

}

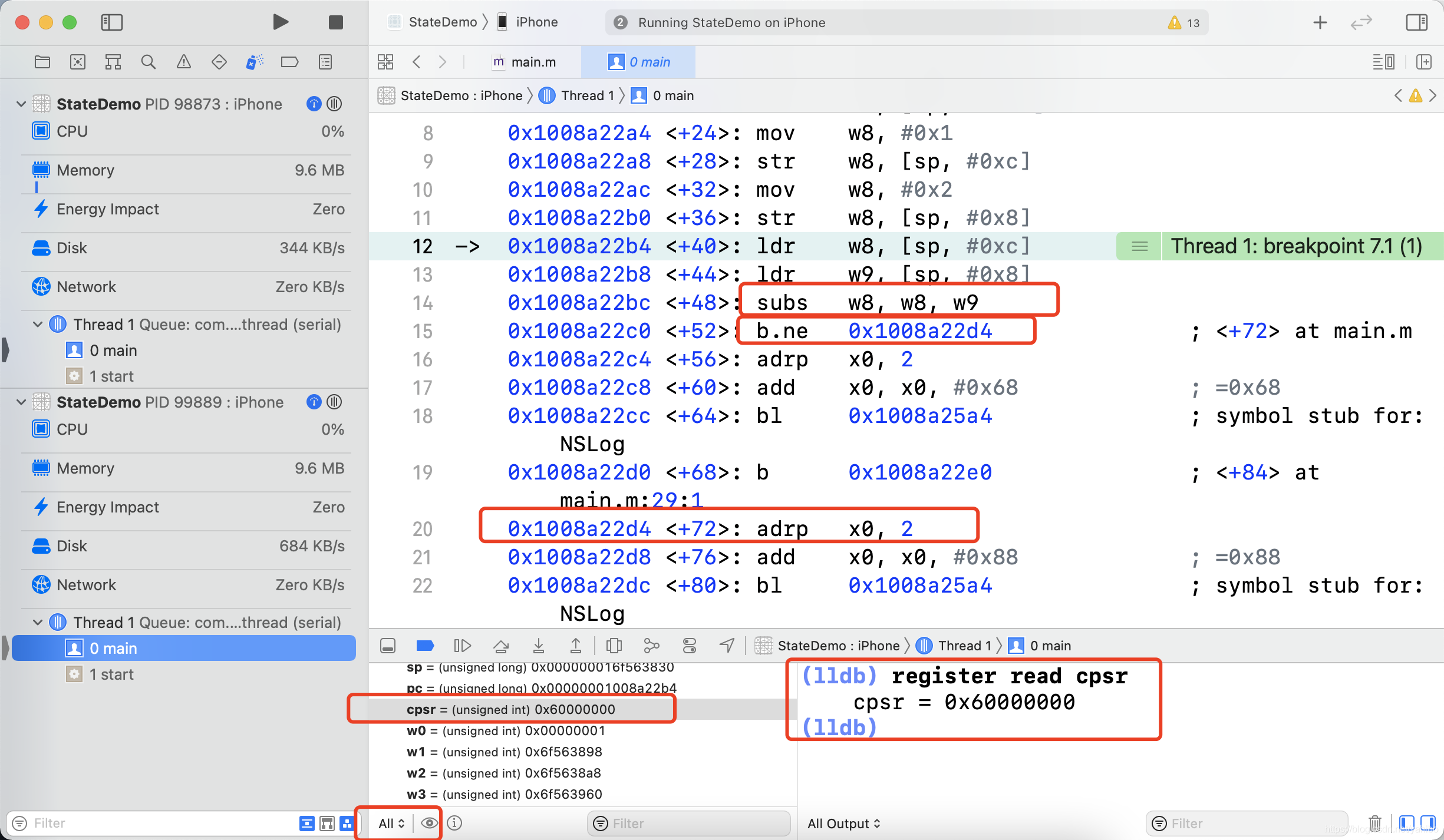

使用真机运行,因为真机和模拟器使用的不是一套指令集,不便于我们验证。断点后查看标志位(General Purpose Registers):

- 可以在

Xcode上查看寄存器值,也可以使用register read cpsr指令来读取cpsr寄存器的值 - 上图断点停留在

ldr指令处,还没有到判断指令,此时查看到cpsr的高位为6即0110,N标志位为0 subs w8, w8, w9指令进行减运算,从上面指令可知w8=1,w9=2相减得-1,结果赋值到w8寄存器,此时,出现一个减法运算,结果为负出现借位,并且不为零,不存在溢出,所有可以提前判断高位NZCV为1000b.ne为判断跳转指令,判断w8和w9是否不相等,如果不相等跳转至0x1008a22d4地址指令处执行(实际上是判断Z(零标志位)是否为零,为零相等,不为零不相等。两个相同整数相减结果为零)

相关b指令:

| 指令 | 描述 |

|---|---|

| bl | 跳转到指定地址处执行,函数调用 |

| b.lt | 比较结果是小于(less than),跳转指定地址执行,否则不跳转 |

| b.le | 比较结果是小于等于(less than or equal to),跳转指定地址执行,否则不跳转 |

| b.gt | 比较结果是大于(greater than),跳转指定地址执行,否则不跳转 |

| b.ge | 比较结果是大于等于(greater than or equal to),跳转指定地址执行,否则不跳转 |

| b.eq | 比较结果是等于(equal to),跳转指定地址执行,否则不跳转 |

| b.ne | 不叫结果是不等于(not equal to),跳转指定地址执行,否则不跳转 |

| b.hi | 比较结果是无符号大于,跳转指定地址执行,否则不跳转 |

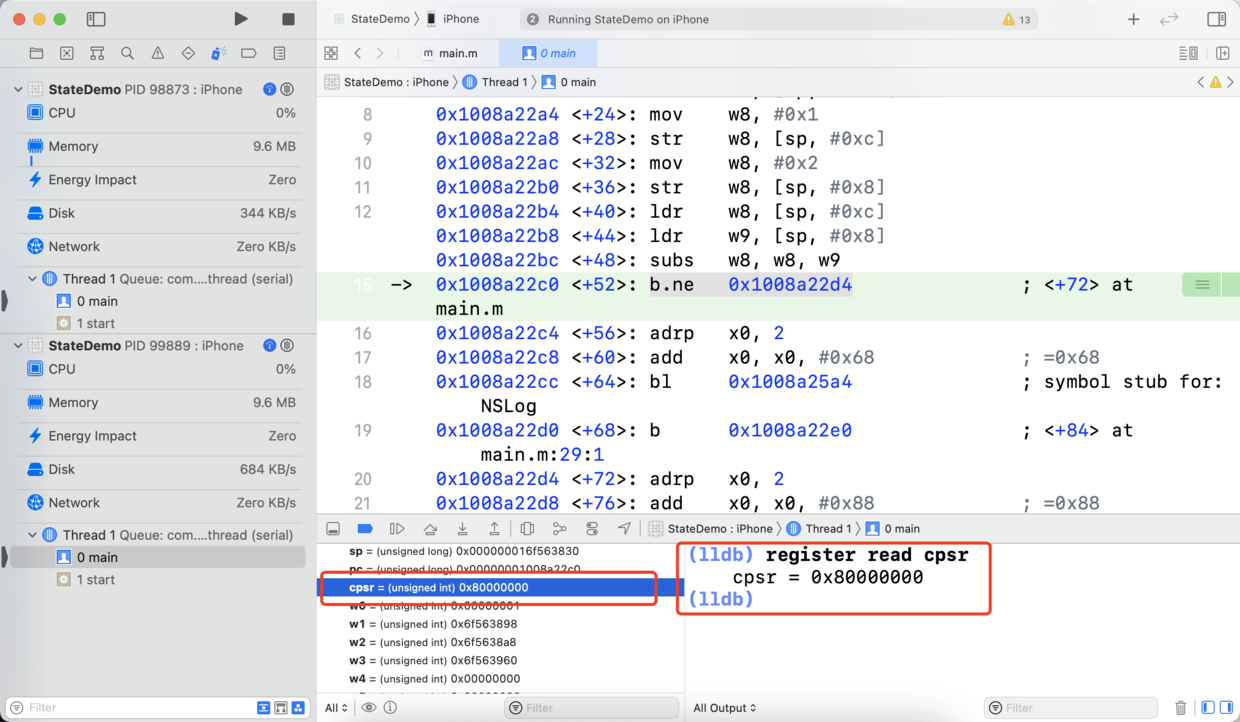

单步向下执行到b.ne 0x1008a22d4指令处,查看寄存器值如下:

- 结果为

0x80000000即高位为1000符合预期,此时指令将跳转到0x1008a22d4处,也就是输出“不相等”

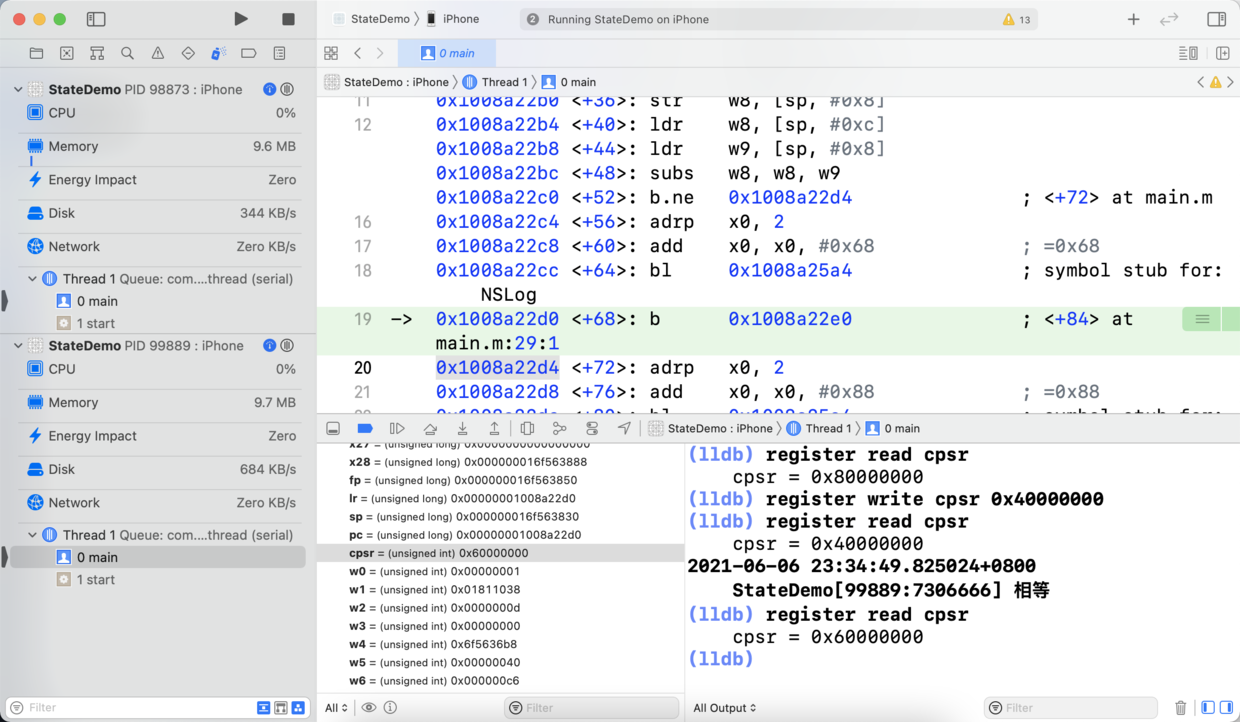

上面到了判断是否不相等的位置,还没有执行该判断指令,理论上是会打印“不相等”。这里可以尝试修改该寄存器的值让其相等,看看打印结果是否为“相等”。也就是Z标志位为1,其他标志位为0,即高位为0100也就是0x40000000,下面看下修改结果是否符合预期。结果如下:

- 打印相等符合预期,通过修改状态寄存器值,改变了程序的正常执行流程

- 最后

cpsr寄存器为0x60000000,对应高位0110,C位变为1,主要原因执行了add x0, x0, #0x68指令,加法指令出现进位C=1

总结

状态寄存器控制着程序的执行流程,那么在逆向中我们可以通过修改状态寄存器的值,使一些关键判断条件无效,来绕过程序中对外的限制。如:破解反逆向、给自己开一个超级会员。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?