Intel有一个超过100页的文档,专门介绍cpuid这条指令,可见这条指令涉及内容的丰富。

记得去年的时候,曾经有个“英布之剑”问过我这条指令,当时并没有给出一个满意的回答,现在放假,想起来,把资料整理了一下。很久以前确实用过这条指令,其实指令本身并没有什么难的,关键是看你有没有耐心研读完繁琐的资料,当然还得对CPU有一定的了解,如果“英布之剑”看到这篇文章,而且仍然需要更详细的资料,可以给我一个联系方式,或者相互之间可以交流一下。

cpuid就是一条读取CPU各种信息的一条指令,大概是从80486的某个版本开始就存在了。似乎是从80386开始,当CPU被RESET以后,CPU会在EDX寄存器中返回一个32bits的CPU签名(Processor Identification Signature),但这时候CPU还没有CPUID这条指令,后来出现了这条指令后,软件无需以来CPU复位就可以读出这个CPU签名,同时还可以读出很多CPU的相关信息。

CPUID这条指令,除了用于识别CPU(CPU的型号、家族、类型等),还可以读出CPU支持的功能(比如是否支持MMX,是否支持4MB的页等等),内容的确是十分丰富。CPUID指令有两组功能,一组返回的是基本信息,另一组返回的是扩展信息,本文介绍基本信息部分,扩展信息部分下篇中介绍。本文所在程序或程序片段,均使用MASM 6.11编译连接,可以在DOS(包括虚拟机的DOS下)运行。

1、如何判断CPU是否支持CPUID指令

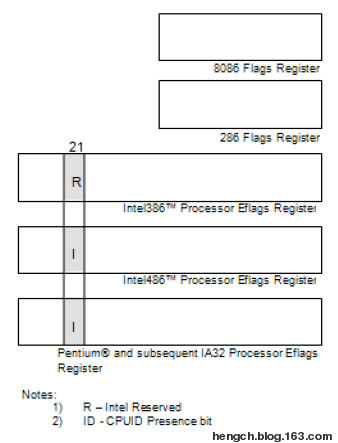

前面说过,大概是从80486开始才有的cpuid这个指令,是不是所有的80486家族CPU都有这个指令我也不是很清楚,但在EFLAGS中的bit 21可以识别CPU是否支持CPUID指令,如下图:

图1

在8086和8088CPU中,FLAGS只有16位长,在80386CPU中,bit 21被保留未用,在支持CPUID指令的CPU中,这一位将为1。

2、CPUID指令的执行方法

把功能代码放在EAX寄存器中,执行CPUID指令即可。例如:

mov eax, 1

cpuid

前面说过CPUID指令分为两组,一组返回基本信息,一组返回扩展信息,当执行返回基本信息的CPUID指令时,EAX中功能代码的bit 31为0,当执行返回扩展信息的CPUID指令时,EAX中的功能代码的bit 31为1。那么不管是那组功能,如何知道EAX中的功能代码最大可以是多少呢?根据Intel的说明,可以用如下方法:

mov eax, 0

cpuid

执行完CPUID指令后,EAX中返回的值就是返回基本信息时,功能代码的最大值,在执行CPUID指令要求返回基本信息时,EAX中的值必须小于或等于该值。

mov eax, 80000000h

cpuid

执行完CPUID指令后,EAX中返回的值就是返回扩展信息时,功能代码的最大值,在执行CPUID指令要求返回扩展信息时,EAX中的值必须小于或等于该值。

由于很多编译器都不能编译CPUID指令,所以了解CPUID指令的操作码是必要的,CPUID指令的操作码是:

0FA2h

3、返回基本信息的功能全貌

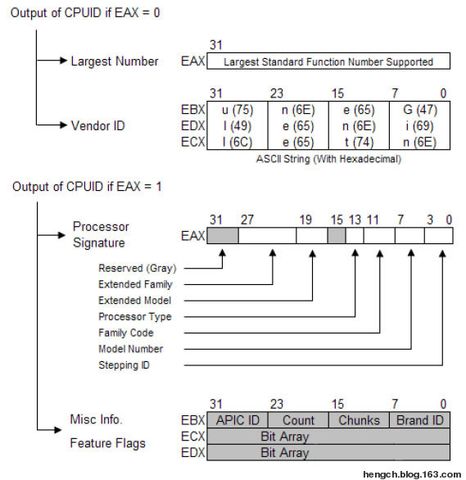

在实际介绍每一个功能之前,我们先通过一张图了解一下返回基本信息的功能全貌。

图2

4、EAX=0:获取CPU的Vendor ID

Vendor ID这个东西,在以前介绍PCI的文章中应该介绍过,实际上就是制造商的标识,用下面的方法执行该功能:

mov eax, 0

cpuid

执行CPUID指令后,AX中返回的内容前面已经说过了,返回的Vendor ID固定为12个ASCII字符依次存放在EBX、EDX、ECX中,对于Intel的CPU,返回的字符串永远是:GenuineIntel。对应在三个寄存器中的值如下:

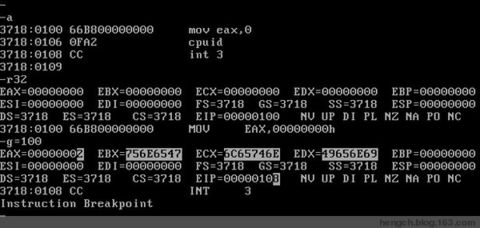

EBX=756E6547h,EDX=49656E69h,ECX=6C65746Eh

大家可以参考图2。

尽管本文是介绍Intel的CPUID指令,但下面还是尽我所知,列出其它厂家生产的IA-32架构CPU的Vendor ID,希望能对需要这些资料的人有所帮助。

- AMDisbetter! ---- 早期AMD K5芯片的工程样品芯片

- AuthenticAMD ---- AMD

- CentourHauls ---- Centour

- CyrixInstead ---- Cyrix

- GenuineTMx86 或 TransmetaCPU ---- Transmeta

- Geode by NSC ---- National Semiconductor

- NexGenDriven ---- NexGen

- SiS SiS SiS ---- SiS

- RiseRiseRise ---- Rise

- UMC UMC UMC ---- UMC

- VIA VIA VIA ---- VIA

5、EAX=1:处理器签名(Processor Signiture)和功能(Feature)位

mov eax, 1

cpuid

执行完成后,处理器签名放在EAX中,功能位及其它杂七杂八的内容分别放在EBX、ECX和EDX中。

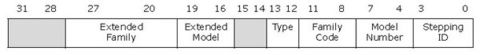

- 处理器签名(Processor Signiture):

返回在EAX中,定义如下:

图中的灰色区域表示没有定义。前面说过,当CPU复位时,会在EDX中返回处理器签名,从80486以后,这个签名和上面的定义完全一样,只是放在不同的寄存器中而已。前面还提到过,80386在复位时也返回处理器签名,但80386返回的签名格式是和上面不同的,后面可能会提到。

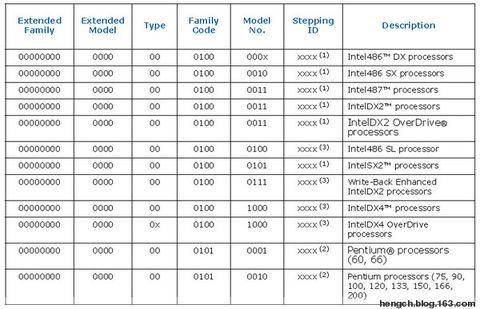

通过处理器签名,可以确定CPU的具体型号,以下是部分Intel CPU的处理器签名数据(资料来自Intel):

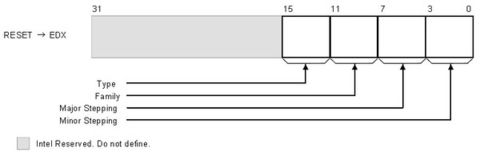

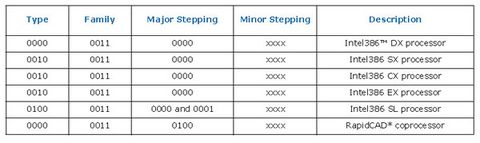

前面说过,80386尽管没有CPUID指令,但在复位时也是可以返回处理器签名的,下面是80386返回的处理器签名的格式:

下面是80386处理器签名的识别方法(资料来自Intel):

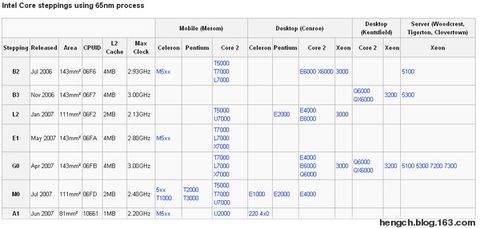

- 关于Stepping的说明:

Intel和AMD都有Stepping的概念,用来标识一款同样规模的微处理器从一开始到你用的这款处理器经历的设计过程,用一个字母和一个数字表示。一般来说,一款同样规模的微处理器的第一个版本是A0,如果改进了设计,则可以通过改变字母或者数字进行标识,如果仅仅改变数字(比如改成A3),说明进行了一些辅助的改进,如果字母和数字都改变,说明改动较大,Stepping可以使用户可以识别微处理器的版本。下面是一个Stepping的例子(不知道为什么穿上来后图这么小)。

- 当处理器签名一样时的处理

有时候,从处理器签名上仍然不能识别CPU,比如根据Intel提供的资料,Pentium II, Model 5、Pentium II Xeon, Model 5和Celeron®, Model 5的处理器签名完全一样,要区别他们只能通过检查他们的高速缓存(Cache)的大小,后面将介绍使用CPUID指令获得CPU高速缓存信息的方法,如果没有高速缓存,则是Celeron®处理器;如果L2高速缓存为1MB或者2MB,则应该是Pentium II Xeon处理器,其它情况则应该是Pentium II处理器或者是只有512KB高速缓存的Pentium II Xeon处理器。

有些情况下,如果从处理器签名上不能区分CPU,也可以使用Brand ID(在EBX的bit7:0返回)来区分CPU,比如Pentium III, Model 8、Pentium III Xeon, Model 8和Celeron®, Model 8三种处理器的处理器签名也是一样的,但它们的Brand ID是不同的。

- 关于处理器类型的定义

在处理器签名中的bit12:13返回的是处理器类型,其定义如下

Value Descriptor

---------------------------------------------

00 以前的OEM处理器

01 OverDrive®处理器

10 多处理器(指可用于多处理器系统)

- 功能标志(Feature Flag)

在EDX和ECX中返回的功能标志表明着该CPU都支持那些功能,EDX定义如下(资料来源与Intel):

bit Name Description

--------------------------------------------------------------------------------

00 FPU FPU On-chip

01 VME Virtual Mode Extended

02 DE Debugging Extension

03 PSE Page Size Extension

04 TSC Time Stamp Counter

05 MSR Model Specific Registers

06 PAE Physical Address Extension

07 MCE Machine-Check Exception

08 CX8 CMPXCHG8 Instruction

09 APIC On-chip APIC Hardware

10 Reserved

11 SEP Fast System Call

12 MTRR Memory Type Range Registers

13 PGE Page Global Enable

14 MCA Machine-Check Architecture

15 CMOV Conditional Move Instruction

16 PAT Page Attribute Table

17 PSE-36 36-bit Page Size Extension

18 PSN Processor serial number is present and enabled

19 CLFSH CLFLUSH Instruction

20 Reserved

21 DS Debug Store

22 ACPI Thermal Monitor and Software Controlled Clock Facilities

23 MMX MMX technology

24 FXSR FXSAVE and FXSTOR Instructions

25 SSE Streaming SIMD Extensions

26 SSE2 Streaming SIMD Extensions 2

27 SS Self-Snoop

28 HTT Multi-Threading

29 TM Thermal Monitor

30 IA64 IA64 Capabilities

31 PBE Pending Break Enable

ECX定义如下(资料来自Intel):

bit Name Description

---------------------------------------------------------

00 SSE3 Streaming SIMD Extensions 3

01 Reserved

02 DTES64 64-Bit Debug Store

03 MONITOR MONITOR/MWAIT

04 DS-CPL CPL Qualified Debug Store

05 VMX Virtual Machine Extensions

06 SMX Safer Mode Extensions

07 EST Enhanced Intel SpeedStep® Technology

08 TM2 Thermal Monitor 2

09 SSSE3 Supplemental Streaming SIMD Extensions 3

10 CNXT-ID L1 Context ID

12:11 Reserved

13 CX16 CMPXCHG16B

14 xTPR xTPR Update Control

15 PDCM Perfmon and Debug Capability

17:16 Reserved

18 DCA Direct Cache Access

19 SSE4.1 Streaming SIMD Extensions 4.1

20 SSE4.2 Streaming SIMD Extensions 4.2

21 x2APIC Extended xAPIC Support

22 MOVBE MOVBE Instruction

23 POPCNT POPCNT Instruction

25:24 Reserved

26 XSAVE XSAVE/XSTOR States

27 OSXSAVE

31:28 Reserved

下面是在DEBUG中当EAX=0时执行CPUID指令时的情况:

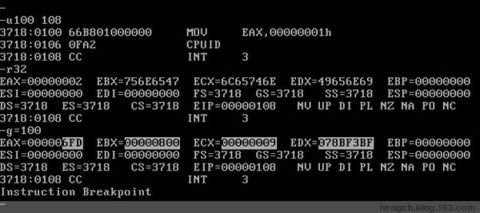

下面是在DEBUG中当EAX=1时执行CPUID指令时的情况

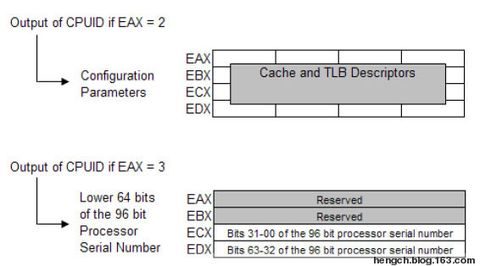

6、EAX=2:高速缓存描述符(Cache Descriptor)

mov eax, 2

cpuid

执行完CPUID指令后,高速缓存描述符和TLB(Translation Lookable Buffer)特性将在EAX、EBX、ECX和EDX中返回,每个寄存器中的4个字节分别表示4个描述符,描述符中不同的值表示不同的含义(后面有定义),其中EAX中的最低8位(AL)的值表示要得到完整的高速缓存的信息,需要执行EAX=2的CPUID指令的次数(一般都为1,在我这里的数台机器里,还没有为2的),同时,寄存器的最高位(bit 31)为0,表示该寄存器中的描述符是有效的,下面是描述符值的定义(资料来源与Intel):

Value Cache or TLB Descriptor Description

----------------------------------------------------------------------------------------

00h Null

01h Instruction TLB: 4-KB Pages, 4-way set associative, 32 entries

02h Instruction TLB: 4-MB Pages, fully associative, 2 entries

03h Data TLB: 4-KB Pages, 4-way set associative, 64 entries

04h Data TLB: 4-MB Pages, 4-way set associative, 8 entries

05h Data TLB: 4-MB Pages, 4-way set associative, 32 entries

06h 1st-level instruction cache: 8-KB, 4-way set associative, 32-byte line size

08h 1st-level instruction cache: 16-KB, 4-way set associative, 32-byte line size

09h 1st-level Instruction Cache: 32-KB, 4-way set associative, 64-byte line size

0Ah 1st-level data cache: 8-KB, 2-way set associative, 32-byte line size

0Ch 1st-level data cache: 16-KB, 4-way set associative, 32-byte line size

0Dh 1st-level Data Cache: 16-KB, 4-way set associative, 64-byte line size, ECC

21h 256-KB L2 (MLC), 8-way set associative, 64-byte line size

22h 3rd-level cache: 512-KB, 4-way set associative, sectored cache, 64-byte line size

23h 3rd-level cache: 1-MB, 8-way set associative, sectored cache, 64-byte line size

25h 3rd-level cache: 2-MB, 8-way set associative, sectored cache, 64-byte line size

29h 3rd-level cache: 4-MB, 8-way set associative, sectored cache, 64-byte line size

2Ch 1st-level data cache: 32-KB, 8-way set associative, 64-byte line size

30h 1st-level instruction cache: 32-KB, 8-way set associative, 64-byte line size

39h 2nd-level cache: 128-KB, 4-way set associative, sectored cache, 64-byte line size

3Ah 2nd-level cache: 192-KB, 6-way set associative, sectored cache, 64-byte line size

3Bh 2nd-level cache: 128-KB, 2-way set associative, sectored cache, 64-byte line size

3Ch 2nd-level cache: 256-KB, 4-way set associative, sectored cache, 64-byte line size

3Dh 2nd-level cache: 384-KB, 6-way set associative, sectored cache, 64-byte line size

3Eh 2nd-level cache: 512-KB, 4-way set associative, sectored cache, 64-byte line size

40h No 2nd-level cache or, if processor contains a valid 2nd-level cache, no 3rd-level cache

41h 2nd-level cache: 128-KB, 4-way set associative, 32-byte line size

42h 2nd-level cache: 256-KB, 4-way set associative, 32-byte line size

43h 2nd-level cache: 512-KB, 4-way set associative, 32-byte line size

44h 2nd-level cache: 1-MB, 4-way set associative, 32-byte line size

45h 2nd-level cache: 2-MB, 4-way set associative, 32-byte line size

46h 3rd-level cache: 4-MB, 4-way set associative, 64-byte line size

47h 3rd-level cache: 8-MB, 8-way set associative, 64-byte line size

48h 2nd-level cache: 3-MB, 12-way set associative, 64-byte line size, unified on-die

49h 3rd-level cache: 4-MB, 16-way set associative, 64-byte line size(Intel Xeon

processor MP, Family 0Fh, Model 06h) 2nd-level cache: 4-MB, 16-way set associative,

64-byte line size

4Ah 3rd-level cache: 6-MB, 12-way set associative, 64-byte line size

4Bh 3rd-level cache: 8-MB, 16-way set associative, 64-byte line size

4Ch 3rd-level cache: 12-MB, 12-way set associative, 64-byte line size

4Dh 3rd-level cache: 16-MB, 16-way set associative, 64-byte line size

4Eh 2nd-level cache: 6-MB, 24-way set associative, 64-byte line size

50h Instruction TLB: 4-KB, 2-MB or 4-MB pages, fully associative, 64 entries

51h Instruction TLB: 4-KB, 2-MB or 4-MB pages, fully associative, 128 entries

52h Instruction TLB: 4-KB, 2-MB or 4-MB pages, fully associative, 256 entries

55h Instruction TLB: 2-MB or 4-MB pages, fully associative, 7 entries

56h L1 Data TLB: 4-MB pages, 4-way set associative, 16 entries

57h L1 Data TLB: 4-KB pages, 4-way set associative, 16 entries

5Ah Data TLB0: 2-MB or 4-MB pages, 4-way associative, 32 entries

5Bh Data TLB: 4-KB or 4-MB pages, fully associative, 64 entries

5Ch Data TLB: 4-KB or 4-MB pages, fully associative, 128 entries

5Dh Data TLB: 4-KB or 4-MB pages, fully associative, 256 entries

60h 1st-level data cache: 16-KB, 8-way set associative, sectored cache, 64-byte line size

66h 1st-level data cache: 8-KB, 4-way set associative, sectored cache, 64-byte line size

67h 1st-level data cache: 16-KB, 4-way set associative, sectored cache, 64-byte line size

68h 1st-level data cache: 32-KB, 4 way set associative, sectored cache, 64-byte line size

70h Trace cache: 12K-uops, 8-way set associative

71h Trace cache: 16K-uops, 8-way set associative

72h Trace cache: 32K-uops, 8-way set associative

73h Trace cache: 64K-uops, 8-way set associative

78h 2nd-level cache: 1-MB, 4-way set associative, 64-byte line size

79h 2nd-level cache: 128-KB, 8-way set associative, sectored cache, 64-byte line size

7Ah 2nd-level cache: 256-KB, 8-way set associative, sectored cache, 64-byte line size

7Bh 2nd-level cache: 512-KB, 8-way set associative, sectored cache, 64-byte line size

7Ch 2nd-level cache: 1-MB, 8-way set associative, sectored cache, 64-byte line size

7Dh 2nd-level cache: 2-MB, 8-way set associative, 64-byte line size

7Fh 2nd-level cache: 512-KB, 2-way set associative, 64-byte line size

82h 2nd-level cache: 256-KB, 8-way set associative, 32-byte line size

83h 2nd-level cache: 512-KB, 8-way set associative, 32-byte line size

84h 2nd-level cache: 1-MB, 8-way set associative, 32-byte line size

85h 2nd-level cache: 2-MB, 8-way set associative, 32-byte line size

86h 2nd-level cache: 512-KB, 4-way set associative, 64-byte line size

87h 2nd-level cache: 1-MB, 8-way set associative, 64-byte line size

B0h Instruction TLB: 4-KB Pages, 4-way set associative, 128 entries

B1h Instruction TLB: 2-MB pages, 4-way, 8 entries or 4M pages, 4-way, 4 entries

B2h Instruction TLB: 4-KB pages, 4-way set associative, 64 entries

B3h Data TLB: 4-KB Pages, 4-way set associative, 128 entries

B4h Data TLB: 4-KB Pages, 4-way set associative, 256 entries

CAh Shared 2nd-level TLB: 4 KB pages, 4-way set associative, 512 entries

D0h 512KB L3 Cache, 4-way set associative, 64-byte line size

D1h 1-MB L3 Cache, 4-way set associative, 64-byte line size

D2h 2-MB L3 Cache, 4-way set associative, 64-byte line size

D6h 1-MB L3 Cache, 8-way set associative, 64-byte line size

D7h 2-MB L3 Cache, 8-way set associative, 64-byte line size

D8h 4-MB L3 Cache, 8-way set associative, 64-byte line size

DCh 2-MB L3 Cache, 12-way set associative, 64-byte line size

DDh 4-MB L3 Cache, 12-way set associative, 64-byte line size

DEh 8-MB L3 Cache, 12-way set associative, 64-byte line size

E2h 2-MB L3 Cache, 16-way set associative, 64-byte line size

E3h 4-MB L3 Cache, 16-way set associative, 64-byte line size

E4h 8-MB L3 Cache, 16-way set associative, 64-byte line size

F0h 64-byte Prefetching

F1h 128-byte Prefetching

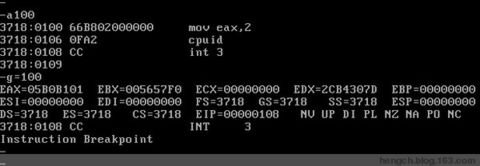

举例来说,在我的机器上执行记过如下:

EAX、EBX、ECX和EDX的bit 31均为0,说明其中的描述符均有效,EAX中的低8位(AL)为1,说明执行一次即可,下面是描述符含义:

05h:Data TLB: 4-MB Pages, 4-way set associative, 32 entries

B0h:Instruction TLB: 4-KB Pages, 4-way set associative, 128 entries

B1h:Instruction TLB: 2-MB pages, 4-way, 8 entries or 4M pages, 4-way, 4 entries

56h:L1 Data TLB: 4-MB pages, 4-way set associative, 16 entries

57h:L1 Data TLB: 4-KB pages, 4-way set associative, 16 entries

F0h:64-byte Prefetching

2Ch:1st-level data cache: 32-KB, 8-way set associative, 64-byte line size

B4h:Data TLB: 4-KB Pages, 4-way set associative, 256 entries

30h:1st-level instruction cache: 32-KB, 8-way set associative, 64-byte line size

7Dh:2nd-level cache: 2-MB, 8-way set associative, 64-byte line size

7、EAX=3:处理器序列号

mov eax,3

cpuid

只有Pentium III提供该功能,486以后的CPU就不再提供该功能,据说是出于隐私的原因。查看你的处理器是否支持处理器序列号功能,可以执行EAX=1的CPUID指令,然后查看EDX的PSN功能(bit 18),如果为1,说明你的处理器可以返回序列号,否则不支持序列号功能或者是序列号功能被关闭了。

处理器序列号一共96位,最高32位就是处理器签名,通过执行EAX=1的CPUID指令获得,其余的64位在执行EAX=3的CPUID指令后,中间32位在EDX中,最低32位在ECX中。

顺便提一句,AMD所有的CPU都没有提供过处理器序列号的功能。

CPUID指令的基本信息,其实后面还有好几个,不过我在我这里的机器(大概有7、8台吧),好像都不支持,大多数只支持EAX=0、1、2三个,所以后面的就不介绍了。

8、EAX=80000001h:最大扩展功能号

mov eax, 80000001h

cpuid

该功能除了能够向(一)中介绍的那样返回CPU支持的最大扩展功能号外,并没有其它作用,EBX、ECX、EDX都不返回有意义的信息。

9、EAX=80000002h:返回CPU支持的扩展功能

mov eax, 80000002h

cpuid

执行CPUID指令后,扩展功能标志在EDX和ECX中返回,EDX中的定义如下:

Bit Name Description

-------------------------------------------------------------------

10:00 Reserved

11 SYSCALL SYSCALL/SYSRET

19:12 Reserved

20 XD Bit Execution Disable Bit

28:21 Reserved

29 Intel® 64 Intel® 64 Instruction Set Architecture

31:30 Reserved

返回在ECX中的位定义:

Bit Name Description

-------------------------------------------------------------------

0 LAHF LAHF / SAHF

31:01 Reserved

10、EAX=80000002h、80000003h、80000004h:返回处理器名称/商标字符串

mov eax, 80000002h

cpuid

......

mov eax, 80000003h

cpuid

......

mov eax, 80000004h

cpuid

每次调用CPUID分别在EAX、EBX、ECX、EDX中返回16个ASCII字符,处理器名称/商标字串最多48个字符,前导字符为空格,结束字符为NULL,在寄存器中的排列顺序为little-endian(即低字符在前),下面程序可以在DOS下显示处理器名称/商标字串(使用MASM 6编译)。

.model tiny

.386

cseg segment para public 'code'

org 100h

assume cs:cseg, ds:cseg, es:cseg

cpuid macro

db 0fh

db 0a2h

endm

begin:

mov eax, 80000000h

cpuid

cmp eax, 80000004h

jb not_supported

mov di, offset CPU_name

mov eax, 80000002h

cpuid

call save_string

mov eax, 80000003h

cpuid

call save_string

mov eax, 80000004h

cpuid

call save_string

mov dx, offset crlf

mov ah, 9

int 21h

cld

mov si, offset CPU_name

spaces:

lodsb

cmp al, ' '

jz spaces

cmp al, 0

jz done

disp_char:

mov dl, al

mov ah, 2

int 21h

lodsb

cmp al, 0

jnz disp_char

done:

mov ax, 4c00h

int 21h

not_supported:

jmp done

save_string:

mov dword ptr [di], eax

mov dword ptr [di + 4], ebx

mov dword ptr [di + 8], ecx

mov dword ptr [di + 12], edx

add di, 16

ret

crlf db 0dh, 0ah, '$'

CPU_name db 50 dup(0)

cseg ends

end begin

11、EAX=80000005h:备用

12、EAX=80000006h:扩展L2高速缓存功能

mov eax, 80000006h

cpuid

执行完CPUID指令后,相应信息在ECX中返回,以下是ECX中返回信息的定义:

Bits Description

-----------------------------------------------------------

31:16 L2 Cache size described in 1024-byte units.

15:12 L2 Cache Associativity Encodings

00h Disabled

01h Direct mapped

02h 2-Way

04h 4-Way

06h 8-Way

08h 16-Way

0Fh Fully associative

11:8 Reserved

7:0 L2 Cache Line Size in bytes.

13、EAX=80000007h:电源管理

mov eax, 80000007h

cpuid

执行CPUID指令后,是否支持电源管理功能在EDX的bit8中返回,其余位无意义。

14、EAX=80000008h:虚拟地址和物理地址大小

mov eax, 80000008h

cpuid

执行CPUID指令后,物理地址的大小在EAX的bit[7:0]返回,虚拟地址的大小在EAX的bit[15:8]返回,返回的内容为虚拟(物理)地址的位数。例如在我的机器上的运行结果如下:

表明我的机器支持36位的物理地址和48位的虚拟地址。

659

659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?