1.上载1—RSLINK连接查看版本号

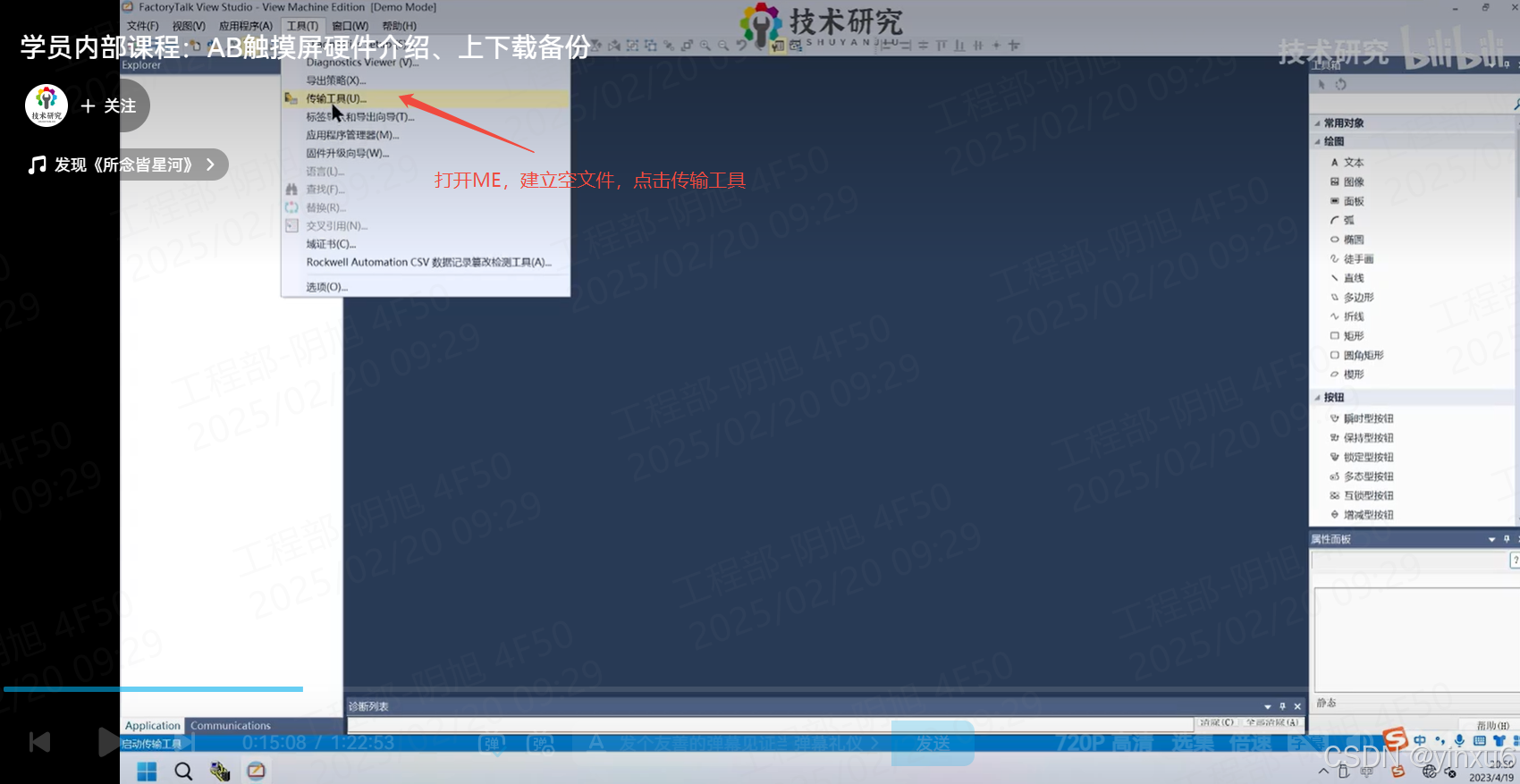

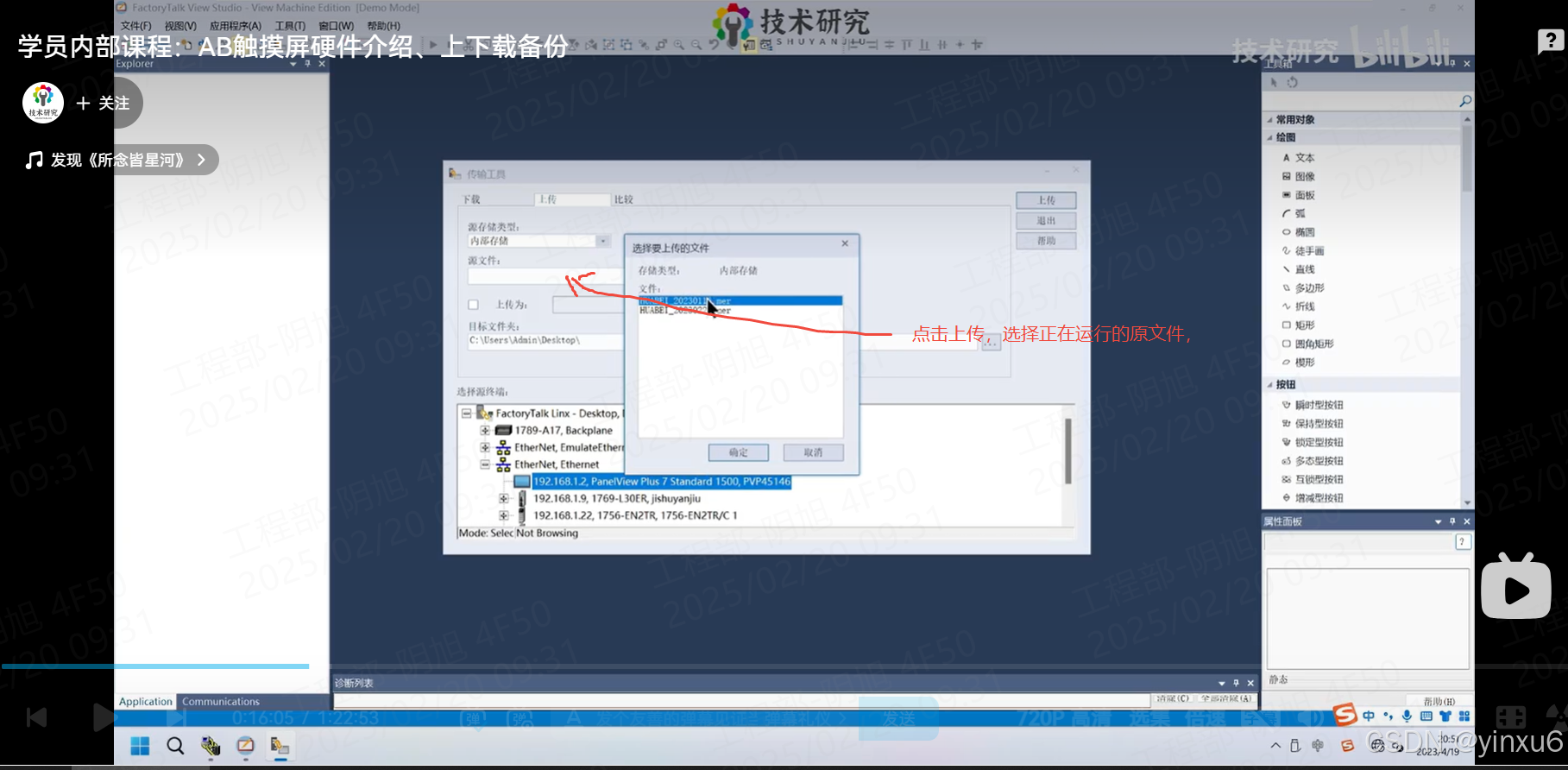

1.上载2—选择运行程序上传,高版本软件可以上传低版本的程序

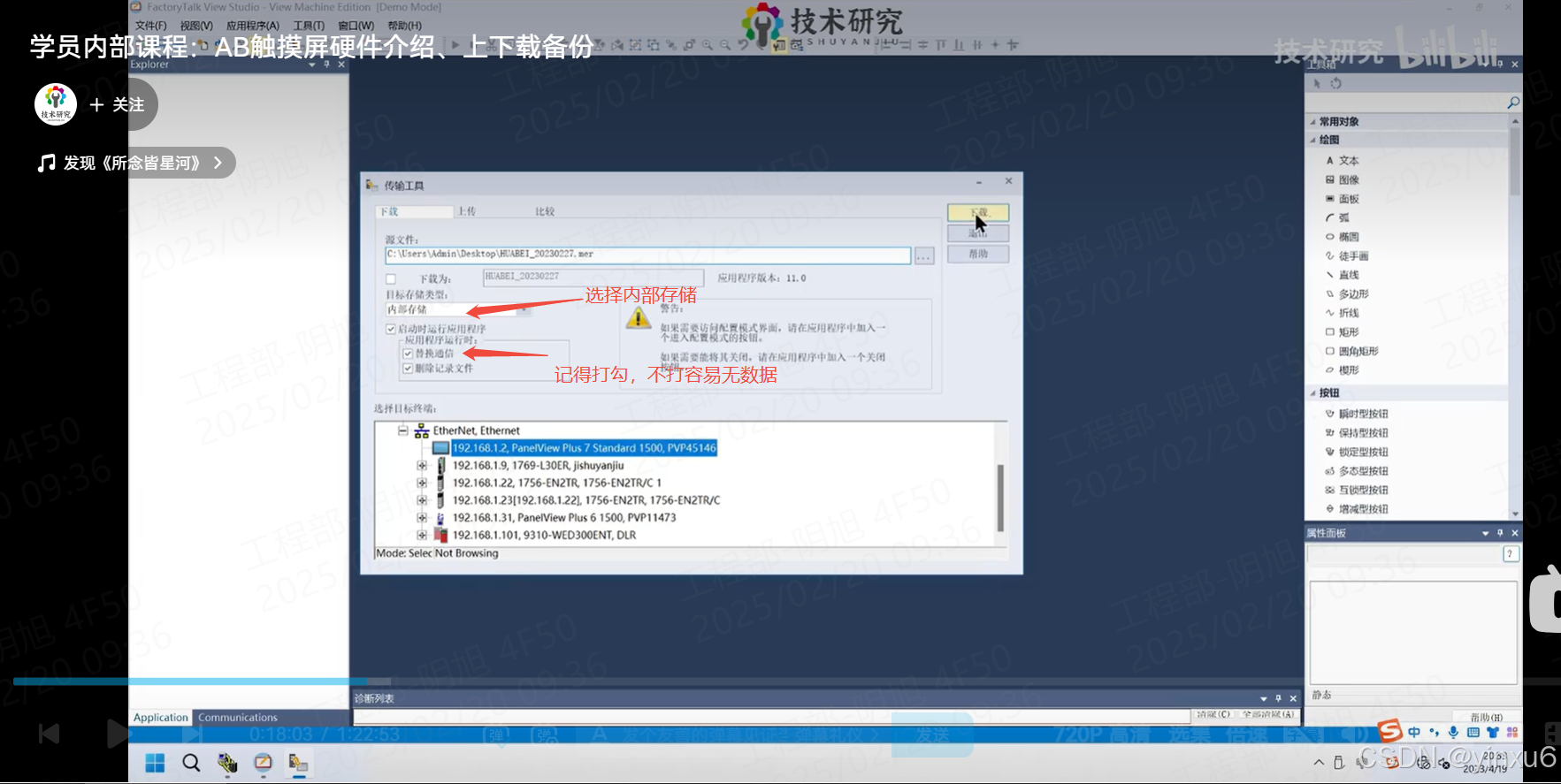

2.下载1—步骤同上载,高版本软件可以下载低版本的上载程序

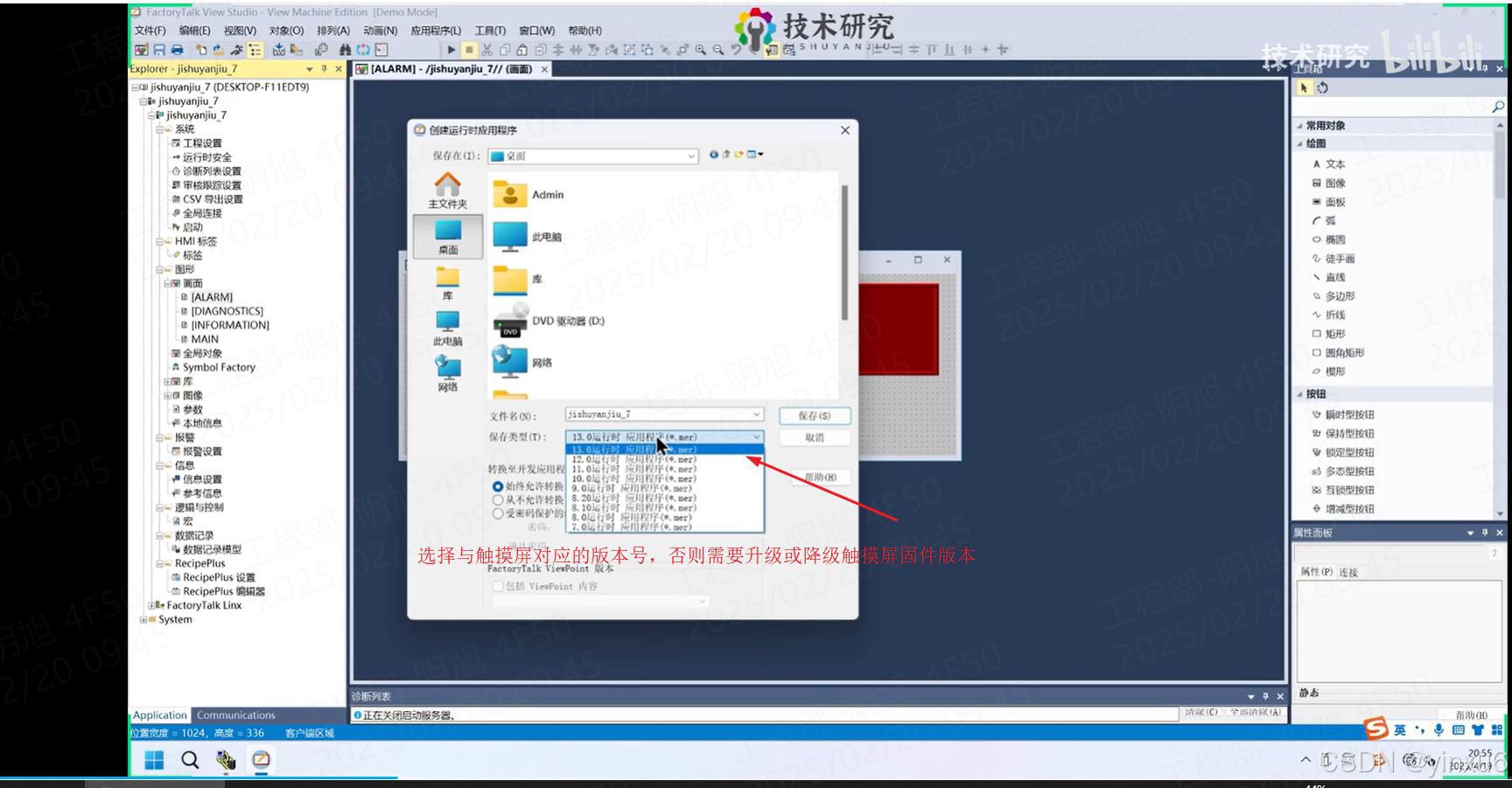

2.下载2—软件更改后下载下载方法,先生成.MER文件

07-05

01-09

2331

2331

2331

2331

05-23

624

624

624

624

01-22

10-21

09-17

6071

6071

6071

6071

07-28

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?