本文主要直译了MIPI D-PHY的规范,基于v3.5的版本。在正文中,译者会添加部分解释,并补充新版本中的差异部分,这部分内容会以引用的形式出现。为了方便对比阅读,章节的顺序和编号,与原文保持一致。各版本差异

6.11 初始化

所有的PHY都支持LP模式。如果同时也支持ALP模式,则由系统实现者决定是使用LP还是使用ALP来初始化链接。所选的初始化取决于目标的低功耗模式,它可以是LP模式或ALP模式。

6.11.1 LP初始化

上电后,当发送端PHY驱动持续时间超过T-INIT的停止状态(LP-11)时,接收器侧PHY应被初始化。时间大于指定T-INIT的第一个停止状态称为初始化周期。发送端PHY本身应通过系统或协议输入信号(PPI)进行初始化。发送端端应确保在初始化之前,不会出现超过T-INIT的停止状态。接收器应忽略初始化期间之前未指定长度的间隔内的所有线路状态。在多通道配置中,所有通道都应同时初始化。

请注意,T-INIT是一个依赖于协议的参数,因此T-INIT-PRIMARY和T-INIT-SECONDARY(发送端和接收器初始化停止状态长度)的确切要求是由协议层规范定义的,不在本文档的范围之内。然而,D-PHY规范确实对T-INIT-PRIMARY和T-INIT-SECONDARY的长度设置了最小限制,每个长度应不小于100µs。使用D-PHY规范的协议层规范可以指定大于此限制的任何值,例如,T-INIT-PRIMARY≥1 ms和T-INIT-SECONDARY= 500到800µs。

6.11.2 ECM LP初始化

嵌入式时钟模式,在LP时钟初始化期间额外消耗600µs的T-INIT,用于配置和与嵌入式时钟模式相关的电路的初始化。因此,T-INIT-PRIMARY 和 T-INIT-SECONDARY长度的总体最小界限应分别为≥700µs。

6.11.3 ECM 初始化和初始训练

本节定义了使用嵌入式时钟模式,在LP初始化后发送的HS初始化序列。这些序列的目标,是将接收器的时钟数据恢复(CDR)块位锁到发射器操作数据的速率和相位,并可选地调整均衡化以补偿符号间的干扰。术语“位锁”,是指CDR电路锁定输入数据的频率和相位的能力。

如图37所示,发射机应以T-INIT-TRAIN的运行数据速率发送嵌入式时钟模式初始训练(定义见表36)序列。接收机应在该时间内完成锁位操作。

如果需要均衡码间干扰(ISI),则发射器应发送如第6.13节中规定的嵌入式时钟模式-交替校准(ECM-ALTCAL)模式。

6.11.4 ALP初始化

上电后,当发送端PHY传输持续时间大于T-INIT的ALP唤醒脉冲时,应初始化接收器PHY。这个传输脉冲然后过渡到ALP停止状态的序列,称为初始化周期。链路的配置应为,在发送端PHY传输初始化序列之前,接收器PHY已通电并准备就绪。发送端PHY本身应通过系统或协议层输入信号(PPI)进行初始化。发送端PHY应确保在初始化发送端PHY之前,通道上没有出现周期超过TINIT的ALP-01通道状态。

当接收器PHY在主PHY之前进入Init状态时,Dp和Dn线不由主PHY驱动。接收器PHY应启用其差分终止Z-ID,直到观察到ALP唤醒脉冲,以避免其接收器输入引脚出现不受控制的电压差,这可能导致错误的ALP-ED触发。发送端PHY在初始状态下不得使用半摆动模式。在关闭发送端PHY电源之前,应确保接收器PHY处于Init状态或已经关闭,以避免错误的ALP-ED触发。

请注意,T-INIT是一个依赖于协议的参数,因此T-INIT-PRIMARY和T-INIT-SECONDARY(发送端和接收器初始化停止状态长度)的确切要求是由协议层规范定义的,不在本文档的范围之内。然而,D-PHY规范确实对T-INIT-PRIMARY和T-INIT-SECONDARY的长度设置了最小限制,每个长度应不小于100µs。使用D-PHY规范的协议层规范可以指定大于此限制的任何值,例如,T-INIT-PRIMARY≥1 ms和T-INIT-SECONDARY= 500到800µs。接收器PHY应在分配的T-INIT周期内禁用其终止。

6.12 Skew Calibration 偏斜校准

注意:

偏斜校准功能仅适用于转发时钟模式,不适用于嵌入时钟模式。

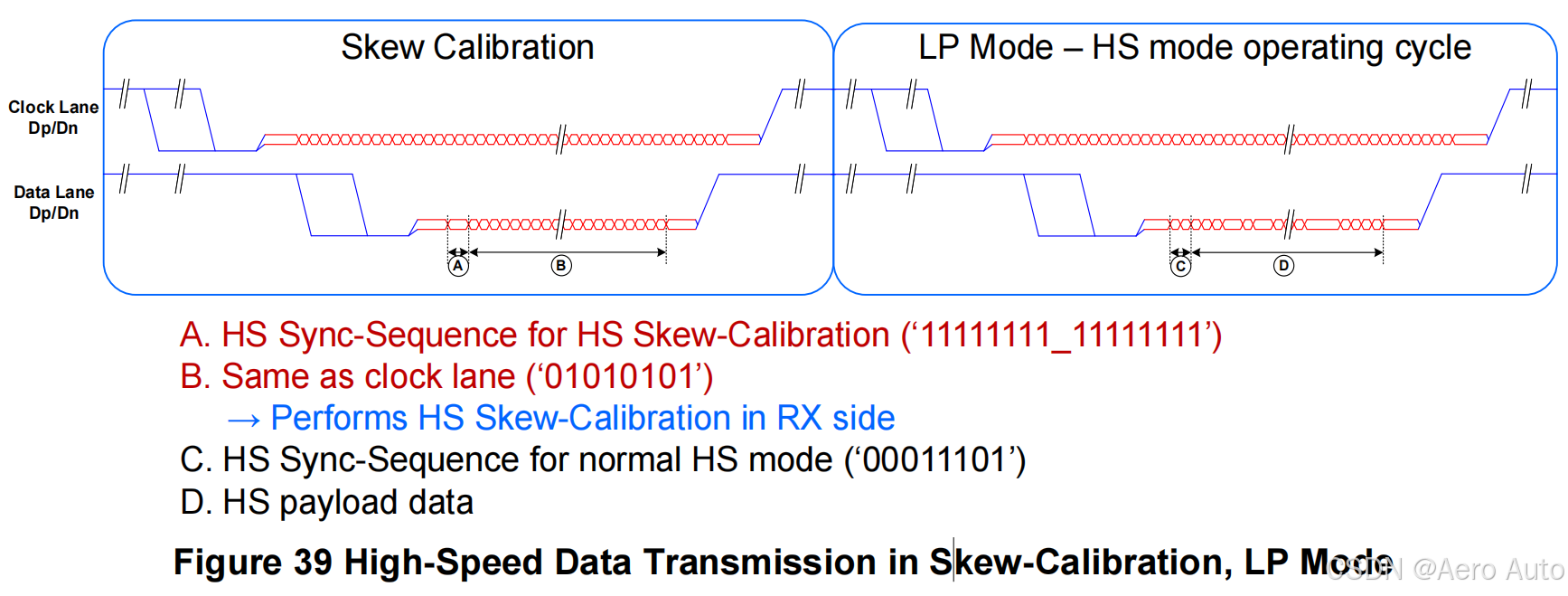

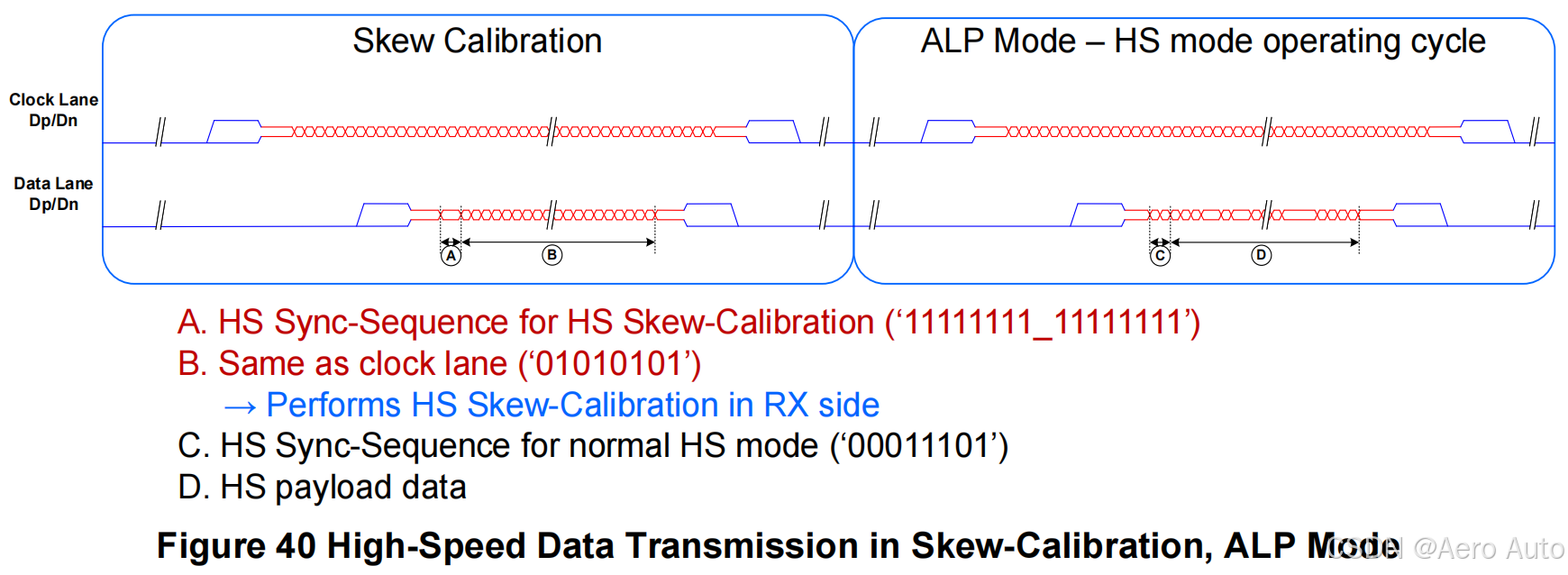

对于支持超过1.5 Gbps速率的DUT(Device Under Test 待测设备),应由发射器启动发射器的偏斜校准。发射器应发送一个特殊的去偏斜突发,如图39和图40所示。当操作速率超过1.5 Gbps或更改为任何超过1.5 Gbps的速率时,应在正常操作的高速数据传输之前,传输一个初始去偏斜序列。当操作速率在或低于1.5 Gbps时,初始去偏斜序列的传输是可选的。周期性去偏斜(Periodic deskew),无论数据速率如何都是可选的。

如果某个速率之前发送过初始去偏斜序列,在改变状态时,例如从ULPS(超低功耗状态)到HS(高速状态),这个速率下的去偏斜序列的传输都是可选的。

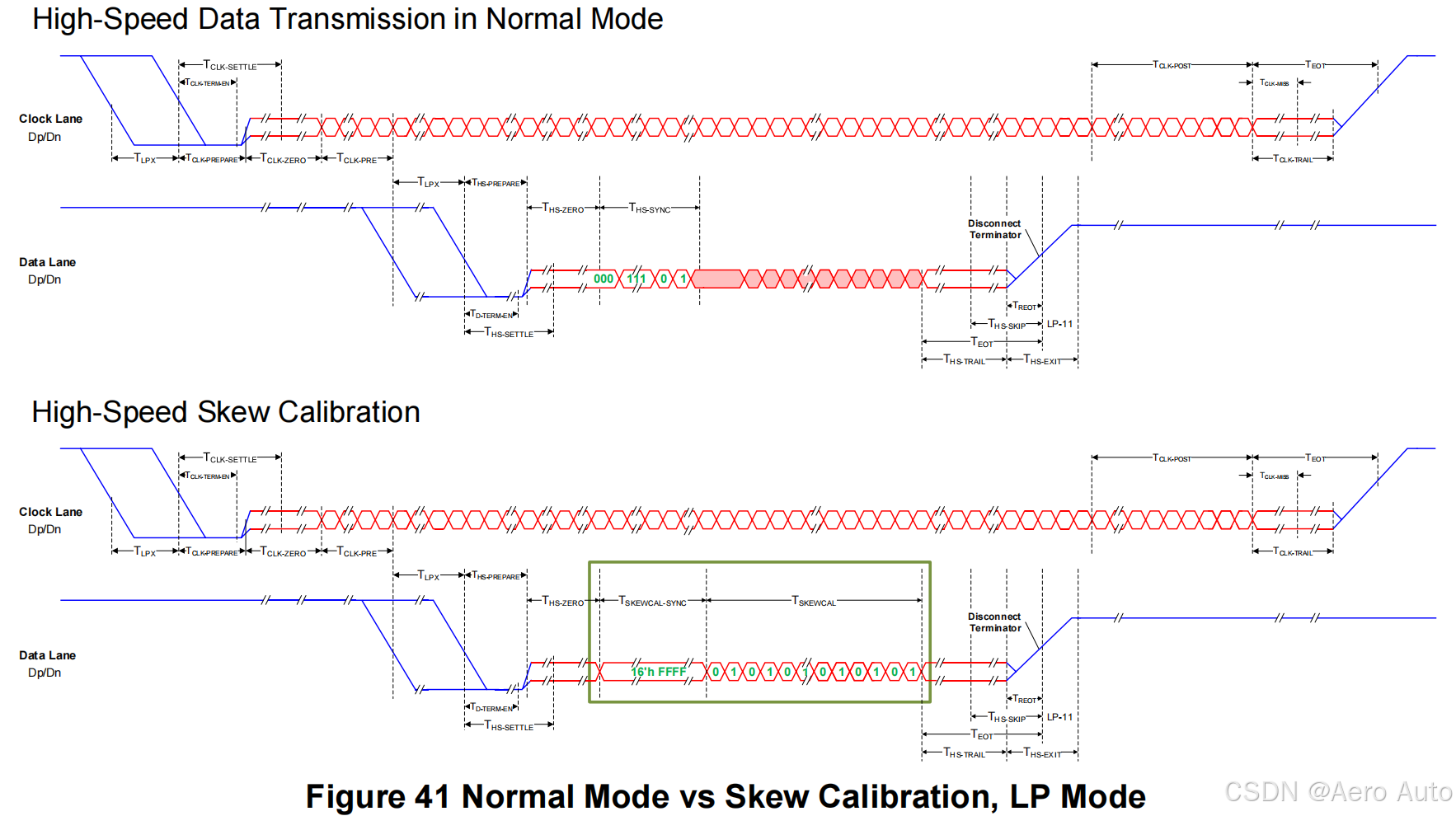

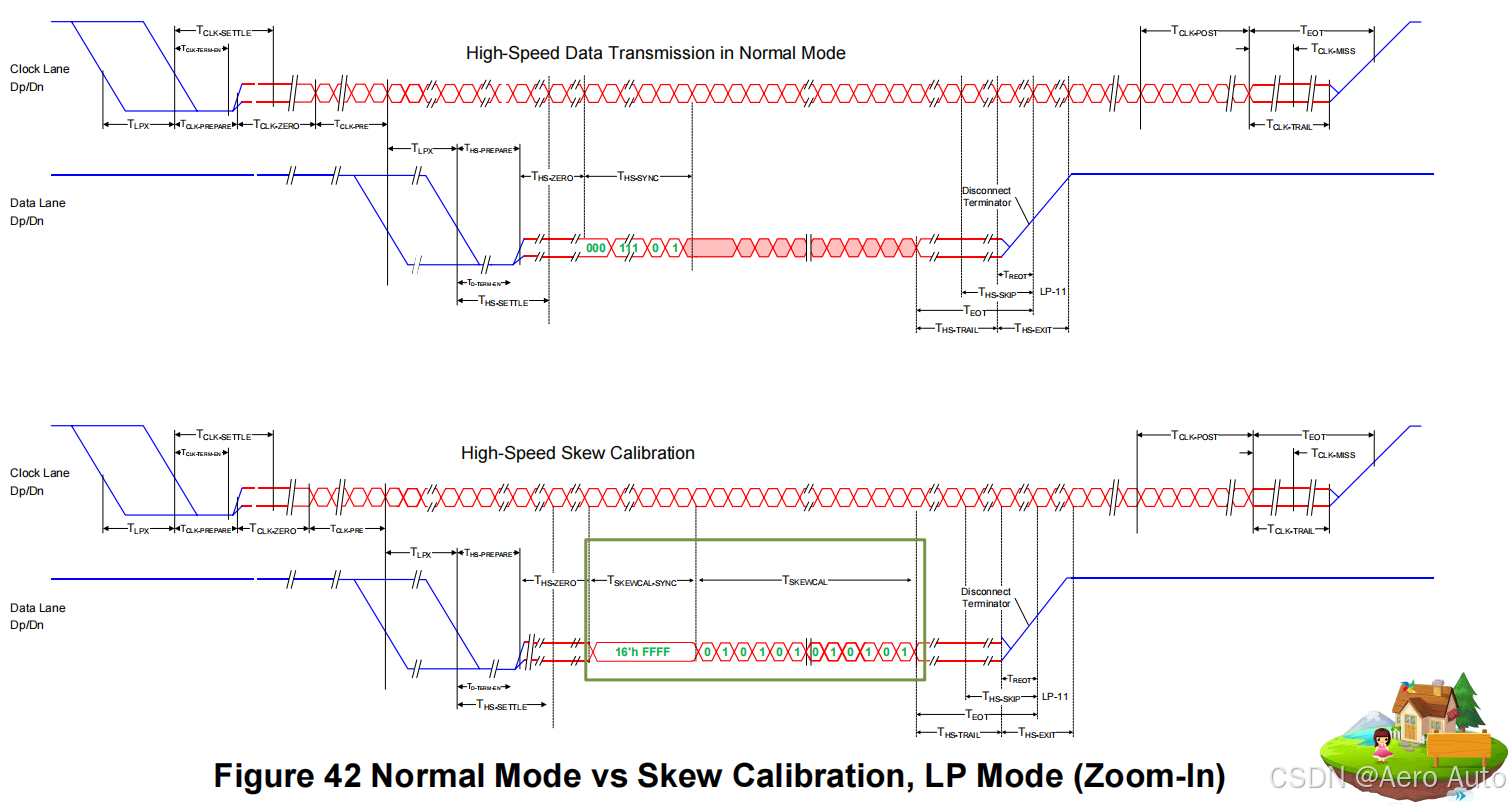

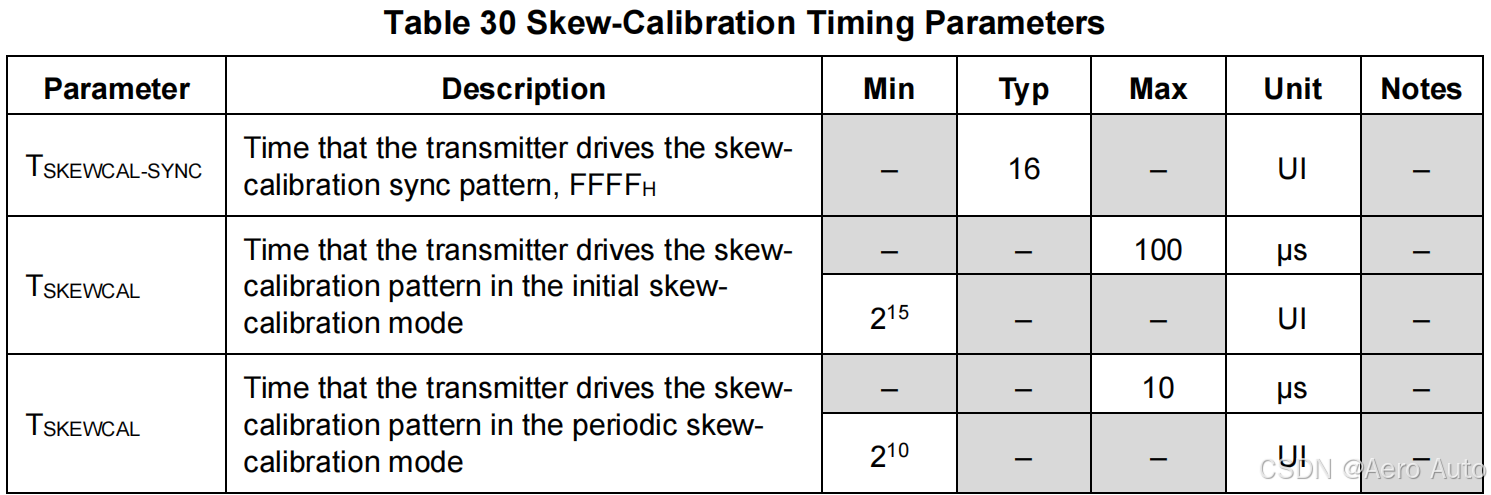

发射器去偏斜脉冲应使用由全1脉冲组成的同步pattern,持续时间为16 UI。同步模式发送后,有效载荷应为时钟模式(0101010101…),初始去偏斜校准的最短持续时间为215UI,用于周期性校准的最短持续时间为210 UI。请参见图41和图42。

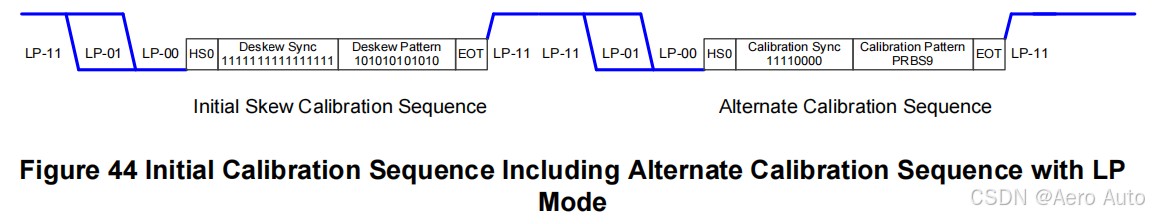

接收器应检测去偏斜同步pattern,并在检测时启动去偏校准。发射器去偏斜序列传输,需要在发射器配置控制时,在所有通道上同时被初始化。传输的SOT开始序列如表28所示,当使用LP模式时的EOT传输结束序列如表29所示。

注意:

在偏斜校准期间, RX端必须完成高速偏斜校准. TX端不会感知RX的偏斜校准是否已经完成.

初始校准时的最大值为100µs,周期校准时的最大值为10µs。时序参数见表30。

对于周期性的去倾斜校准,发送端应在发送去倾斜序列之前,完成电流突发。

在接收器去偏校准期间,接收器的输入端存在抖动信号。在活动模式下,接收机偏斜校准块,应通过扩频时钟Spread Spectrum Clocking正常工作。周期去偏斜的目的,在初始去偏序列所建立的去偏斜基础上,再进行微调。

在ECM嵌入式时钟模式下,不需要偏斜校准(也不需要周期偏斜校准),因为时钟通道没有从数据通道中独立出来。

6.13 备用校准序列Alternate Calibration Sequence

6.13.1 FCM备用校准序列

对于前向时钟模式(FCM),备用校准序列旨在补偿符号间干扰。它与初始偏斜校准结合使用。当运行频率高于2.5 Gbps,或更改到高于2.5 Gbps的任何数据速率时,应在所有的初始偏斜校准之后,传输备用校准序列。备用校准序列由一组前导HS0模式、校准同步和校准模式组成。此校准在链路启动或链路重新初始化时是必需的。

对于工作速率在2.5 Gbps及以下的发射器,传输备用校准序列是可选的。如果接收器不需要或不支持此功能,系统集成商可以禁用备用校准序列。

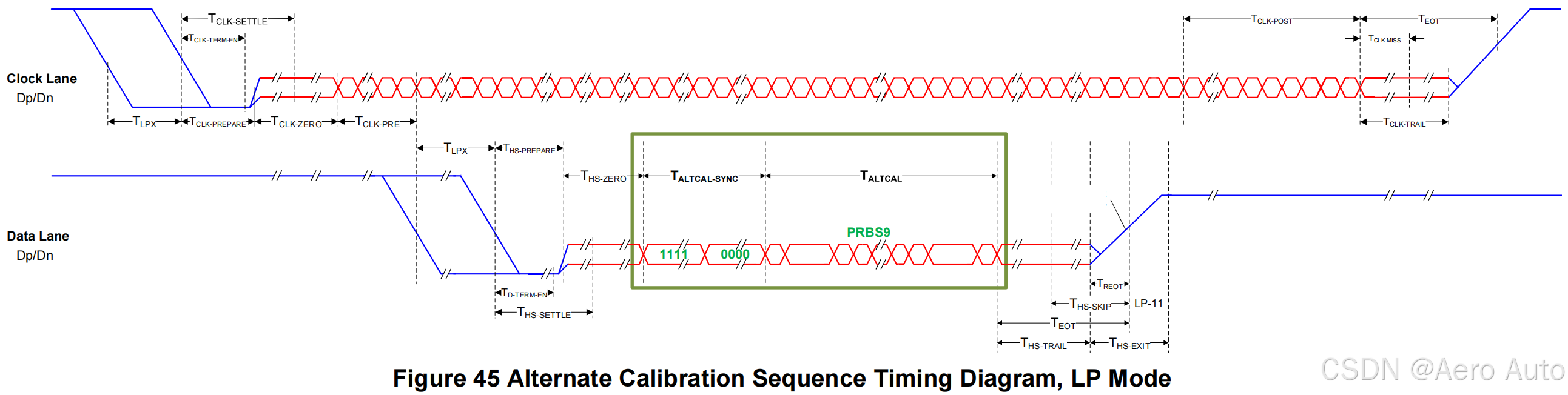

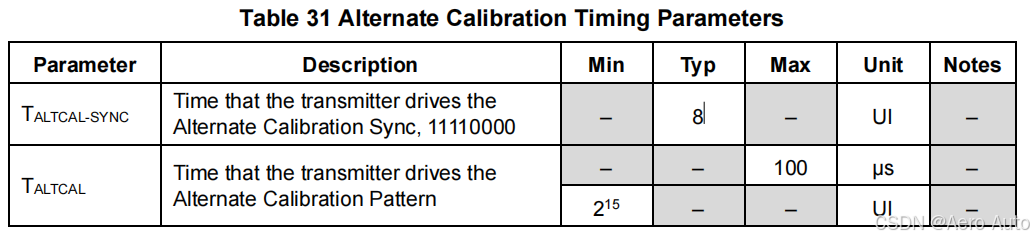

备用校准序列应使用持续时间为T-ALTCAL-SYNC的备用校准同步。在发送备用校准同步后,负载应为最小持续时间为T-ALT-CAL的PRBS9序列。

PRBS9序列由多项式x0 + x5 + x9定义。在备用校准之前,PRBS9序列生成器应使用初始的9位种子值011111111(Q9:Q1)进行初始化。负载的第一个8位字是包含在PRBS9序列生成器寄存器Q1到Q8中的种子值。PRBS9序列生成器在每次输出连续的8位字之前被移位8次。Data[7:0]在附录D中显示。

同样的,多项式x0 + x5 + x9也适用于16位和32位数据接口。在每次输出连续的16位或32位字之前,PRBS9序列生成器分别移位16次或32次,输出到Data[15:0]或Data[31:0]。

如附录D中的图150所示,PRBS9序列生成器应支持8位数据接口示例。

传输顺序应为最低有效位(LSb)优先。例如,使用初始种子的前两个字节传输为1111 1111 1000 0011。

6.13.2 ECM 备用校准序列

嵌入式时钟模式-备用校准序列(ECM-ALTCAL)旨在补偿嵌入式时钟模式下的符号间干扰(ISI: inter-symbol interference)。

在传输ECM-INIT-TRAIN序列后,可以传输ECM-ALTCAL序列。之后,可以传输正常的高速数据(HS-data)突发。

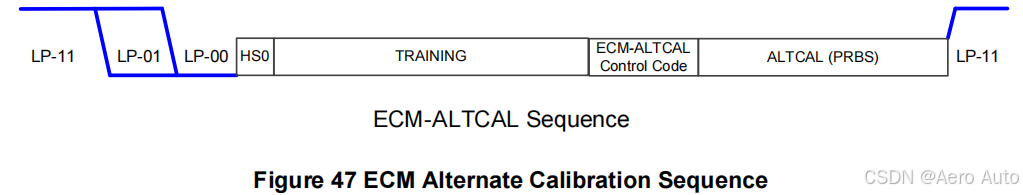

如图47所示,在传输训练模式(TRAINING Pattern)后,发射器应传输表36中定义的ECM-ALTCAL控制代码,然后是持续时间为TALTCAL-SYNC的PRBS9序列。接收器应检测ECM-ALTCAL控制代码,如果该代码被支持,接收器可以使用后续的PRBS9序列对ISI进行均衡,直到高速数据突发结束。PRBS9序列的多项式和种子值定义在第6.13.1节和附录D中。

当运行速度高于2.5 Gbps时,发射器应传输ECM-ALTCAL序列,除非接收器不需要或不支持ECM-ALTCAL序列(在这种情况下,系统集成商可以禁用此功能)。在速度低于2.5 Gbps时,发射器可以支持ECM-ALTCAL序列。

6.14 前导序列 Preamble Sequence

注意: 前导序列功能仅适用于转发时钟模式,不适用于嵌入式时钟模式。

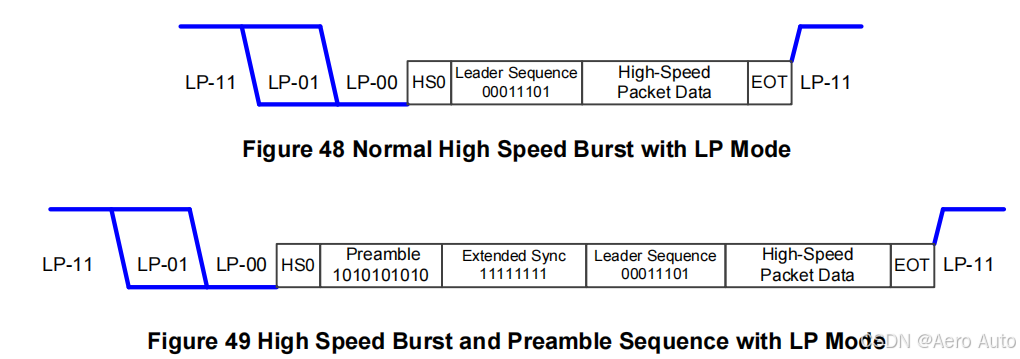

前导序列长度较短,并插入在每个高速有效载荷的开头,其目的是为了微调由于温度和电压变化引起的时钟与数据的偏差。前导序列适用于数据速率超过2.5 Gbps的情况。

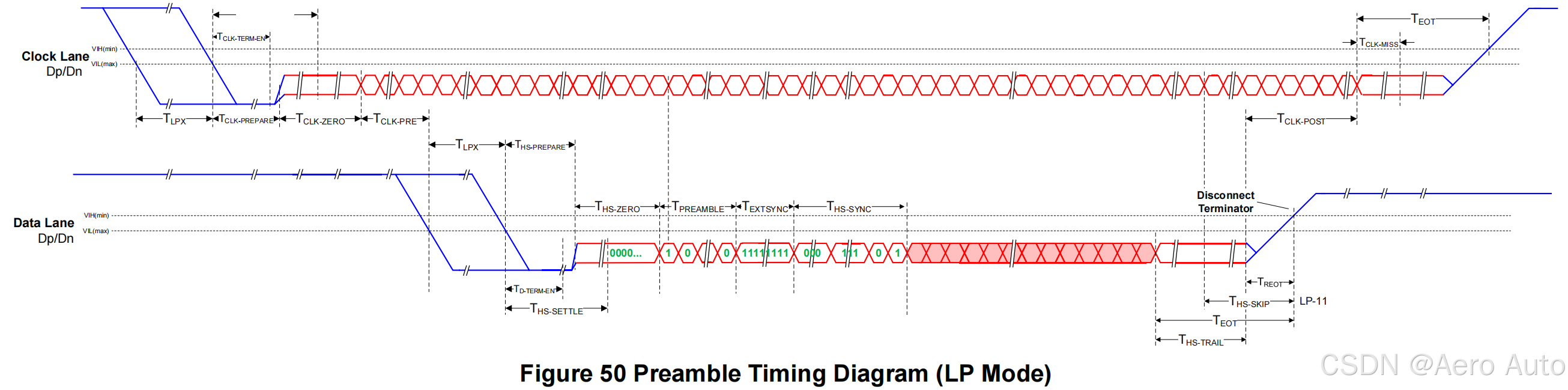

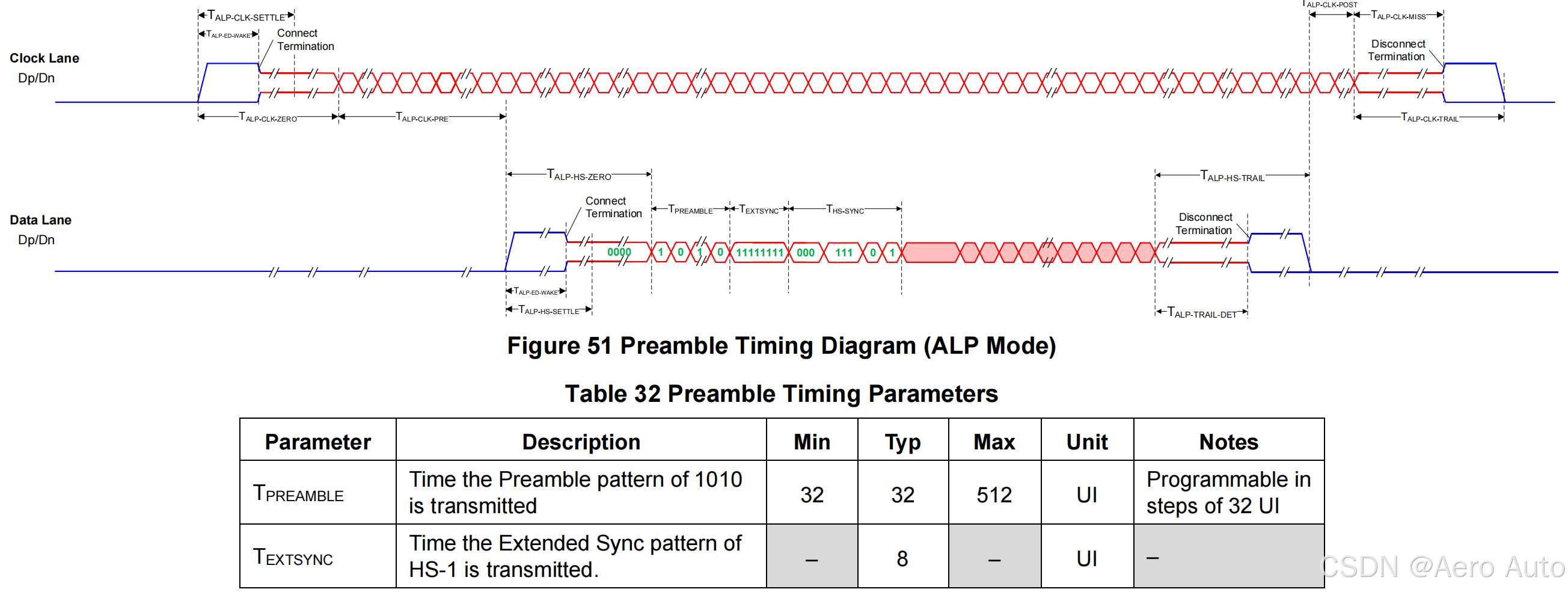

前导序列由可编程长度的前导模式(持续时间为T-PREAMBLE)和固定长度的扩展同步模式(持续时间为T-EXTSYNC)组成。提供扩展同步模式是为了防止前导模式在某些2位错误情况下被检测为引导序列。

前导序列应由运行在超过2.5 Gbps的发射器和接收器支持。在这种情况下,前导序列应在每个高速突发传输时插入(如果启用)。

运行在超过2.5 Gbps的接收器应检测扩展同步模式和引导序列(Leader sequence)。

发射器应允许前导模式的持续时间在T-PREAMBLE范围内可编程,以32 UI为步长。

**所有前导模式在传输引导序列之前应始终跟随扩展同步模式。**前导模式应由表32中定义的持续时间为T-PREAMBLE的1010…模式组成。

发射器的前导模式持续时间应可由系统集成商配置,并应覆盖表32中的整个TPREAMBLE范围,包括禁用前导、扩展同步、仅传输高速突发的选项。

接收器可能只支持T-PREAMBLE范围的一个子集,该子集应在接收器的数据手册中指定。扩展同步模式应由持续时间为T-EXTSYNC的HS-1组成。

发射器应为所有前导长度值传输扩展同步模式。

6.15 HS-空闲状态

注意: 在使用ALP模式或嵌入式时钟模式时,HS-空闲状态功能不被支持。

对于在LP模式 - HS模式操作周期中的PHY,支持HS-空闲状态是可选的。在使用ALP模式时不支持HS-空闲状态。

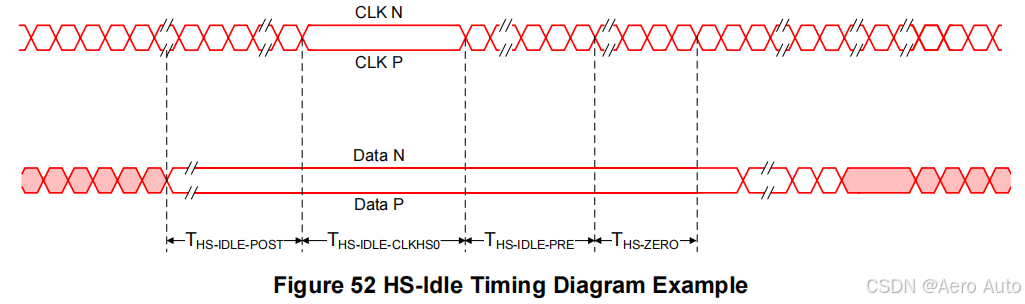

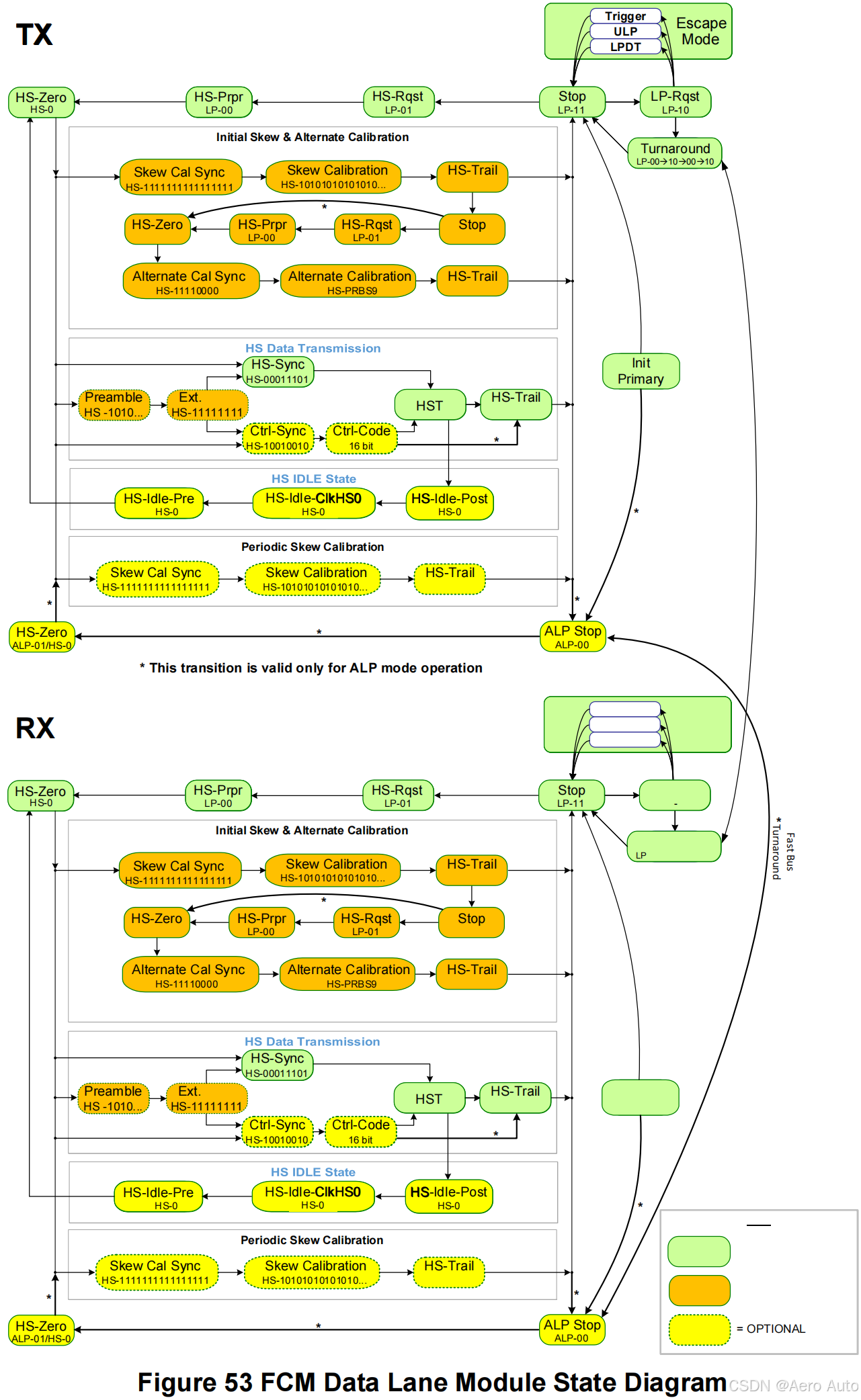

HS-空闲状态可以在保持HS信号传输的情况下用于两个HS数据突发之间。当使用HS-空闲状态时,在两个HS数据突发之间不会转换到LP信号。通过使用HS-空闲状态,可以根据数据速率和HS-空闲时序减少两个HS数据突发之间的延迟。HS-空闲状态包括HS-空闲后期(HS-Idle-Post),HS-空闲时钟HS0(HS-Idle-ClkHS0),和HS-空闲前期(HS-Idle-Pre)子状态,如图53中的状态图所示。PHY可以选择进入HS-空闲状态或LP停止状态,适用于所有数据通道。

在HS-空闲状态下,时钟通道应在所有数据通道完成数据突发并转换到HS-0状态后停止于HS-0状态。时钟通道和处于HS-空闲状态的数据通道的HS-0状态应由PHY生成。在传输完负载数据后,所有数据通道应发出HS-0信号,而不管最后一个负载位的极性如何。如果时钟通道接收器检测到T-CLK-MISS期间没有时钟活动并且所有数据通道都处于HS-0状态,则接收器状态机应转换到HS-空闲状态。当所有数据通道都处于LP-11时,接收器状态机应转换到停止状态。

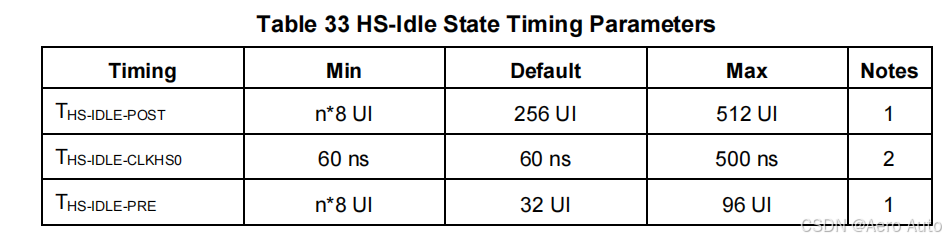

表34描述了HS-空闲状态的状态转换。该表从HS数据突发的最后一位开始,描述了进入和退出HS-空闲状态之前和之后的状态。表34以退出HS-空闲状态后的HS数据突发的第一位结束。

在所有通道完成HS数据突发后,时钟通道应继续发出信号持续T-HS-IDLE-POST的时间,以便有足够的时间清除接收器流水线。

时钟通道的HS-0状态应持续T-HS-IDLE-CLKHS0的时间。

在下一个HS数据突发之前,时钟通道应在T-HS-IDLE-PRE期间保持活动状态。HS-空闲状态应退出到SoT(开始信号)。T-HS-IDLE-POST、T-HS-IDLE-CLKHS0和T-HS-IDLE-PRE时序参数的开始和结束如图52所示。这些时序参数的值在表33中定义。发射器应在启动时支持默认定时值。系统集成商可以根据接收器的能力配置HS-空闲状态参数。

在通道上使用 占空比校正机制(duty cycle correction) 的接收器,在支持可选的HS-空闲状态时,可能需要特别考虑如何处理空闲期。

备注:

- 发射器应支持在最小值到最大值范围内以n*8 UI步长的可编程性。如果使用PPI,则n是TX PPI总线宽度(以字节为单位);如果不使用PPI,则n是特定的实现。系统集成商应能够根据应用需求编程这些参数。

- 对于长时间的HS-空闲状态,如果延迟不存在限制,传统的LP模式能提供更优的功耗解决方案。

6.16 同步Pattern和控制代码

6.16.1 FCM同步Pattern

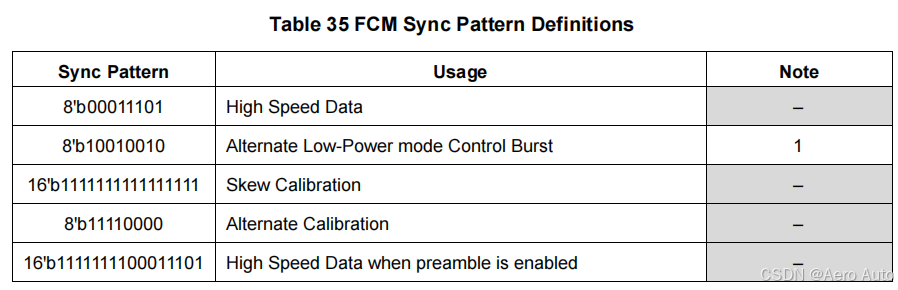

表35列出了在转发时钟模式(FCM)中使用的所有同步模式及其目标用途。

注意:

- 使用方法可能在未来扩展。

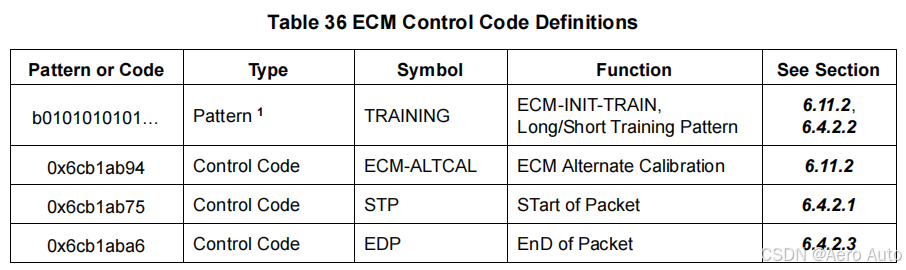

6.16.2 ECM训练模式和控制代码

在嵌入式时钟模式(ECM)中,所有控制代码应不进行加扰传输。表36列出了在嵌入式时钟模式中使用的所有控制代码及其目标用途。

注意:

- 或者,PRBS9训练模式也可以使用(见第6.4.2.2节)。

6.17 全局操作流程图

6.17.1 FCM流程

所有先前描述的操作方面,无论是否包含可选部分,都包含在通道模块(Lane Modules)中。图53显示了数据通道模块的操作流程图。在发送(TX)和接收(RX)过程中,可以区分出五个主要流程:高速传输、低功耗模式(LP模式)、ALP模式、校准和初始化。

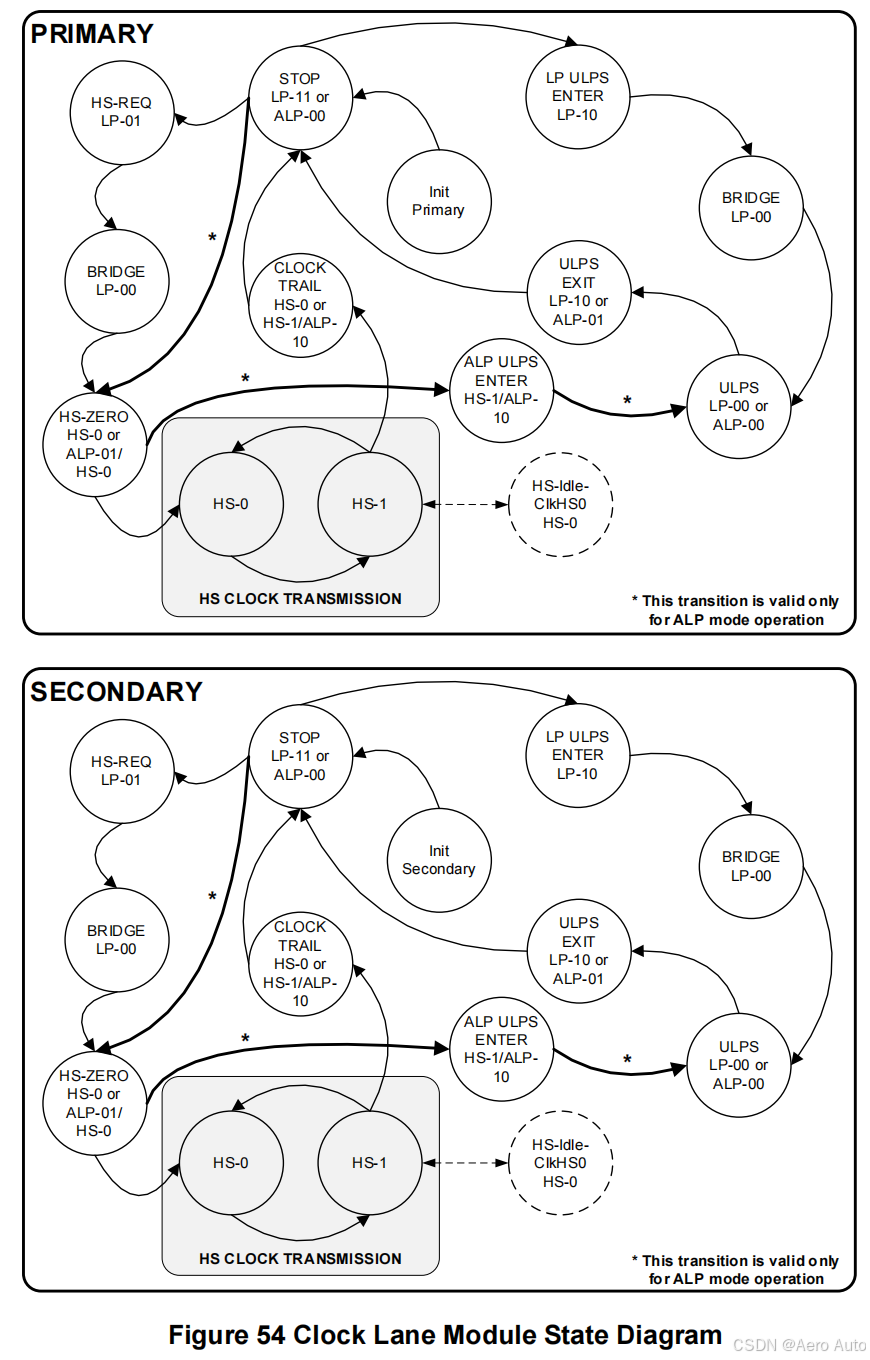

图54显示了时钟通道模块的状态图。时钟通道模块有四个主要操作状态:初始化状态(持续时间未指定)、低功耗停止状态、超低功耗状态和高速时钟传输状态。图中还显示了之前描述的状态转换。

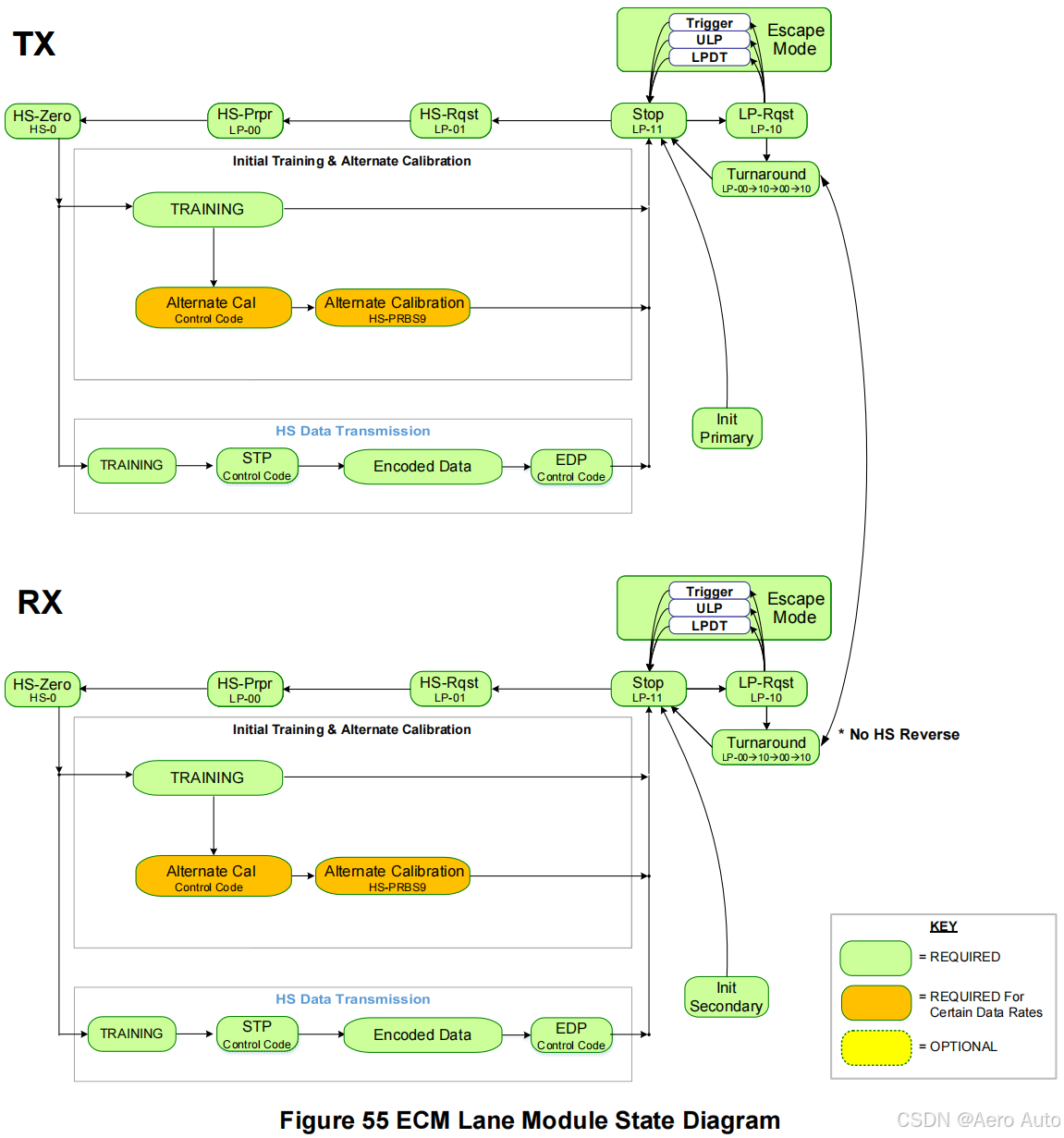

6.17.2 ECM 流程

图55 展示了通道模组状态示意。

6.18 数据速率相关参数(信息性内容)

D-PHY的高速数据传输速率可以根据特定实现进行编程。任何单一的数据传输在SoT和EoT序列之间必须以给定的固定速率进行。然而,允许在初始化时、退出超低功耗(ULP)状态之前或在停止状态(HS时钟未运行时)重新编程D-PHY高速传输的数据速率。本文件不涉及数据速率重新编程的方法。

本文件中的许多时间参数值被指定为固定时间和特定数量的高速UI(单元间隔)的总和。如果数据速率发生变化,从而导致UI值变化,这些参数可能需要重新计算。这些参数及其允许值列在表24和表25中。为了清晰起见,这里重复了参数名称和用途。

6.18.1 仅包含UI值的参数

T-CLK-PRE和T-ALP-CLK-PRE是主设备在时钟通道重新启动进入高速模式后,在任何数据传输开始之前必须发送的最小高速时钟周期数。如果次设备一侧的特定协议需要比T-CLK-PRE或T-ALP-CLK-PRE更多的时钟周期,主设备一侧的协议应确保这些周期被发送。

6.18.2 包含时间和UI值的参数

几个参数被指定为显式时间和UI数量的总和。显式时间值通常来源于在给定的驱动电压和线路终端值下,为了达到规定的值所需的充电和放电时间。因此,显式时间值不依赖于数据速率。可以考虑使用模拟定时器和高速时钟计数器的总和来确保实现满足这些参数。如果这些显式时间值仅通过计数高速时钟周期来实现,那么计数值是数据速率的函数,因此在数据速率变化时必须进行更改。

T-D-TERM-EN是从Dn跨过VIL,MAX开始测量的数据通道接收器线路终端启用时间。

T-HS-PREPARE是在数据通道上开始高速传输前驱动LP-00的时间。

T-HS-PREPARE + THS-ZERO,MIN是驱动LP-00以准备开始高速传输的时间加上发送高速0信号的时间,即在发送SoT同步序列之前,开启线路终端并用高速驱动器驱动互连的时间总和。

T-HS-TRAIL是发送高速传输突发的最后一个有效数据位后,发射器必须驱动翻转的最后一个数据位的时间。接收器需要这段时间来确定EoT。

T-HS-SKIP是接收器必须“回退”并跳过数据以忽略EoT序列的过渡期间的时间。

T-CLK-POST,MIN是最后一个数据通道在高速传输突发后转换到低功耗模式(LP模式)后,发射器继续发送高速时钟的最短时间。如果某个特定的接收器实现需要比T-CLK-POST,MIN更多的时钟周期来完成接收,发射器必须提供足够的时钟以完成接收。

对于ALP操作,有类似的参数:TALP-HS-ZERO、TALP-HS-TRAIL和TALP-CLK-POST。此外,还引入了新的参数,其计时既有绝对成分也有相对成分:TALP-HS-SETTLE,MIN、TALP-TRAIL-DET、TALP-TA-GO、TALP-TA-SURE和TALP-TA-GET。

6.18.3 仅包含时间值的参数

几个参数仅以显式时间值来指定。如在第6.18.2节中,这些显式时间值通常来源于为使互连充电和放电所需的时间,因此不依赖于数据速率。可以使用模拟定时器或高速时钟计数器来确保实现满足这些参数。然而,如果这些时间值仅通过计数高速时钟周期来实现,那么计数值是数据速率的函数,因此在数据速率变化时必须进行更改。

以下参数仅基于时间值:

- T-HS-SKIP,MIN

- T-CLK-MISS,MAX

- T-CLK-TRAIL,MIN

- T-CLK-TERM-EN

- T-CLK-PREPARE

- T-ALP-CLK-MISS,MAX

- T-ALP-CLK-SETTLE

- T-ALP-CLK-TRAIL,MIN

- T-ALP-CLK-ZERO,MIN

- T-ALP-ED-WAKE,MAX

- T-ALP-HS-SETTLE,MIN

6.18.4 仅包含与数据速率无关的时间值的参数

表24中的其余参数,即使在高速时钟关闭时也应遵守。这些参数包括低功耗和初始化状态的持续时间,以及低功耗信号间隔。尽管这些参数不依赖于高速数据速率,一些D-PHY的实现可能需要在数据速率变化时调整这些值。

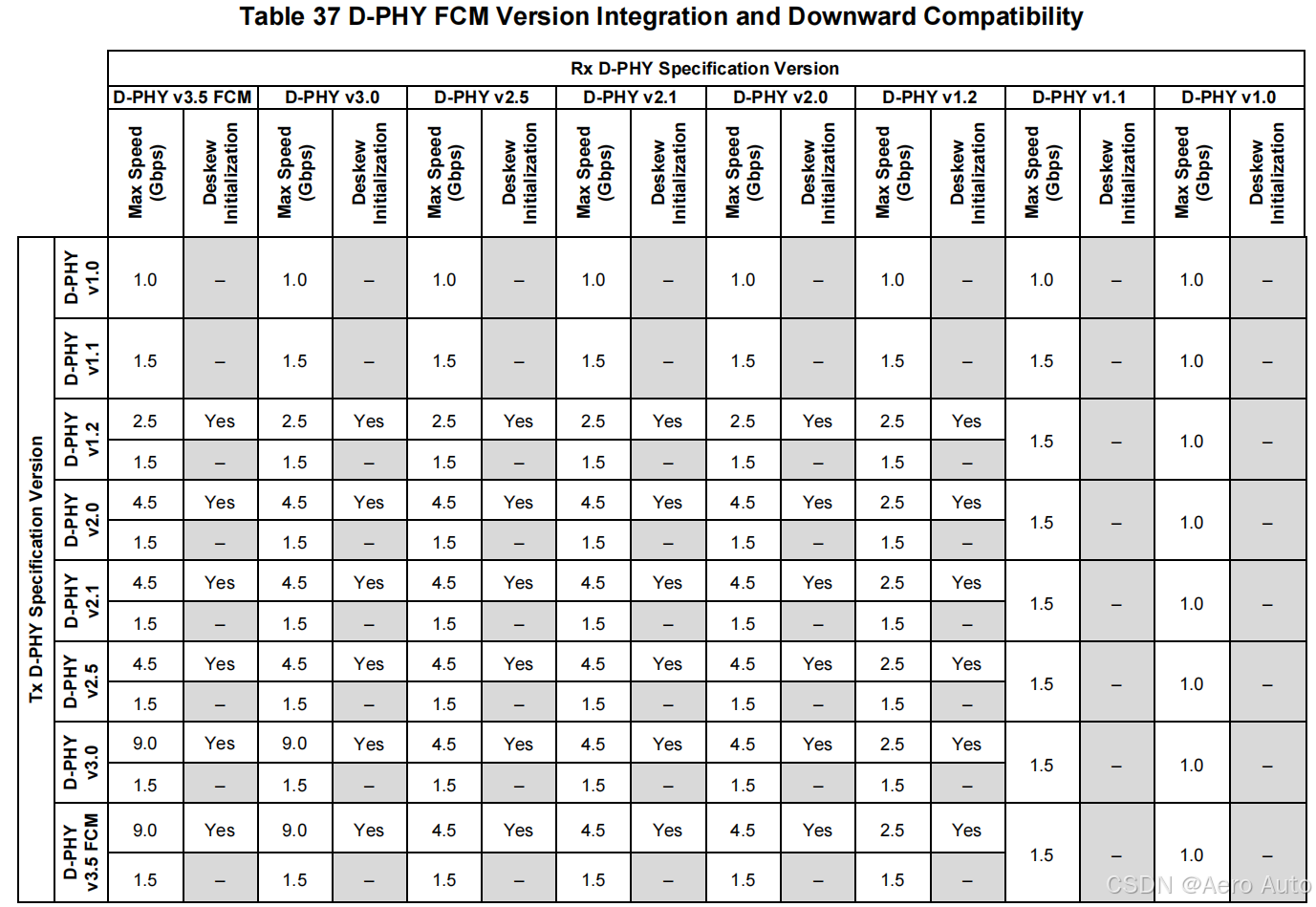

6.19 互操作性

对于转发时钟模式,表37总结了发送端(Tx)的D-PHY规范版本和接收端(Rx)的D-PHY规范版本所有可能组合的集成和向下兼容性。该表显示了每个可能组合的最大工作速度,并指出哪些组合需要进行去斜初始化。例如,D-PHY v2.0发送端和D-PHY v1.2接收端在不进行去斜初始化的情况下兼容速度可达1.5 Gbps,而在进行去斜初始化后可以支持超过1.5 Gbps的速度。

对于嵌入时钟模式,表38总结了发送端(Tx)的D-PHY规范版本和接收端(Rx)的D-PHY规范版本所有可能组合的集成和向下兼容性。

连接在一起的发送端和接收端必须在同一种时钟模式下运行:要么都在转发时钟模式下,要么都在嵌入时钟模式下。

D-PHY v2.0物理层发射器与D-PHY v2.1物理层接收器兼容,反之亦然。

D-PHY v2.0发射器可以与D-PHY v2.1接收器一起工作,但这样的发射器无法向接收器发送D-PHY 2.1的备用校准序列或前导序列加扩展同步模式。

类似地,D-PHY v2.1发射器可以与D-PHY v2.0接收器一起工作,但必须确保在发射器中禁用D-PHY v2.1的备用校准序列和前导序列加扩展同步模式。

D-PHY v2.1的备用校准序列和前导序列加扩展同步模式在操作速率超过2.5 Gbps时由D-PHY v2.1发射器和接收器支持。当启用时,备用校准序列会在任何初始斜率校准之后传输,而前导序列加扩展同步模式会插入每个高速传输突发中。这些功能允许系统在速率超过2.5 Gbps时更稳定地补偿诸如温度和电压的变化。 因此,这些功能的启用取决于具体使用情况,并且在存在D-PHY v2.0发射器或接收器时不能启用。

89

89

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?