day 2 Ubuntu安装vivado2017.04 附 设置全局变量

安装好Ubuntu之后,建立共享文件夹,在虚拟机设置中》选项》共享文件夹

建立好共享文件夹之后,把vivado2017.4复制进改文件夹中(最好是解压好之后复制进去,减少在Ubuntu中解压的步骤)。

在Ubuntu系统中路径:计算机/mnt/hgfs/winshare/ 下(或直接在桌面打开终端,输入 cd /mnt/hgfs/winshare 然后ls ),可看到_v2017的文件夹

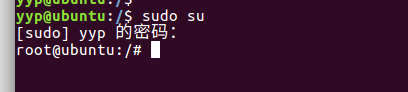

此时,进入_v2017的文件夹进入Xilinx_Vivado_SDK_2017.4_1216_1文件夹,可以看到xsetup文件,在此打开终端(终端中进入此目录也行)切换到root权限(sudo su 后回车 输入你的密码 如果有密码),终端中输入./xsetup,执行该文件。

会弹出vivado的安装界面,此安装过程和在windows下的安装过程一样(安路径默认opt),此处省略。。。。

vivado安装完成后,记得加载lic文件,加载方式与windows相同。

到此安装过程已基本结束,还需注意的是,要加载一个vivado脚本到系统的环境变量中,这样打开vivado的时候就不用每次执行这个脚本了,否则在终端中打开vivado需要先执行settings64.sh 这个脚本 然后再输入vivado 启动vivado软件。

加载到环境变量的操作:

在终端中,切换root用户,输入gedit /etc/bash.bashrc 进入文本编辑状态(也可以用vim或其他方式)

在最后一行添加: source /opt/Xilinx/Vivado/2017.4/settings64.sh

这样,以后开机后,直接在想要建立工程的地方直接打开终端输入vivado就可以打开vivado软件了。。。。

至此,day2结束,到这里,已经可以在Ubuntu中建立vivado工程了。

如果有不对的地方,请大家多多指教。。。。。

1570

1570

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?