前言

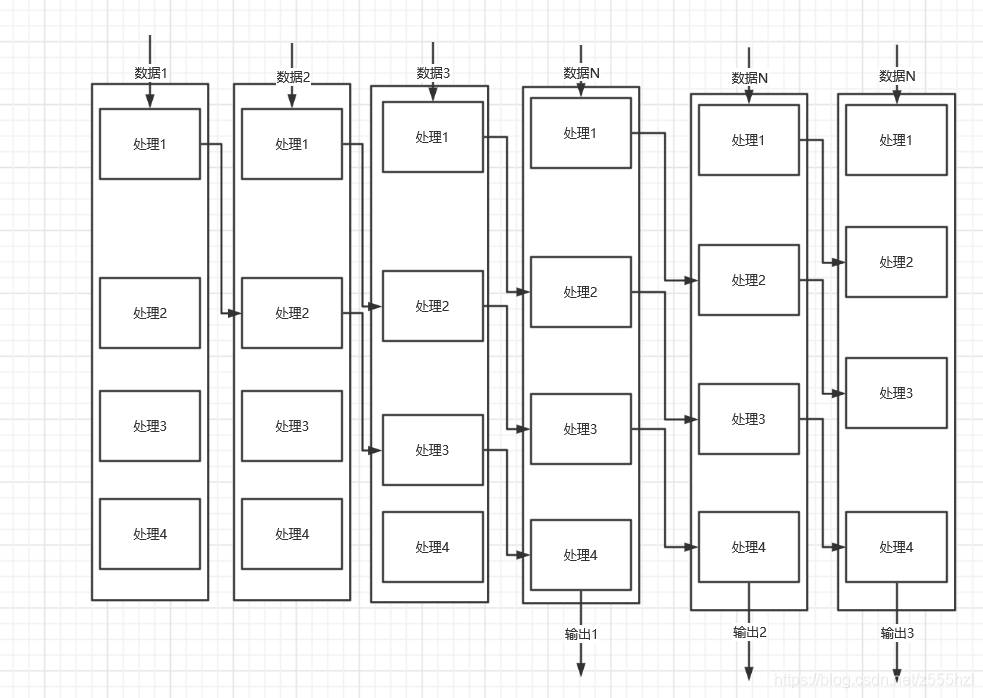

FPGA中的流水线操作是FPGA的优势之一,可以并行的进行单向数据流处理,提高数据处理速度。

一、什么是流水操作?

就是需要N步处理一组数据时,处理单元的前级输入是上一个处理单位的后级输出,可以M组数据同时输入并行流入处理单元,实现原本需要N个的处理单元的时间t之和(t*N)输出一次,在固定延迟之后,以每t个时间输出一次。

二、代码

1.实现了c= (a*b + a)*b的流水计算;

代码如下(示例):

module run_water (

input clk ,

input _rst ,

input [7:0] a ,

input [7:0] b ,

output[15:0] c

);

reg [7:0] a1 = 'd0;

reg [7:0] a2 = 'd0;

reg [7:0] a3 = 'd0;

reg [7:0] a4 = 'd0;

reg [7:0] b1 = 'd0;

reg

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?