DSP复习

1. DSP概述

DSP–>Digital Signal Processor

增强了运算能力,针对数字信号处理做了结构、指令优化和功能增强。

1.1 特点

-

采用流水线操作:在不提高时钟频率的条件下减少了每条指令的执行时间;

-

哈佛结构:数据总线和程序总线分离,比传统处理器的冯·诺依曼结构有更高的指令执行速度;

-

独立的硬件乘法器和加法器:同一时钟周期内可以完成相乘、累加两个运算,适用于滤波、相关、矩阵运算等需要大量乘法累加运算的场合。

-

零开销循环:处理器在执行循环时,不用花时间去检查循环计数器的值、条件转移到循环的顶部、将循环计数器减1。

-

专门的寻址方式:模块(循环)寻址(对实现数字滤波器延时线很有用)

位倒序寻址(间接寻址)(对FFT很有用)

-

优化的精简指令集

1.2 分类

-

按数据格式分:定点型、浮点型(F28335属于定点型)

-

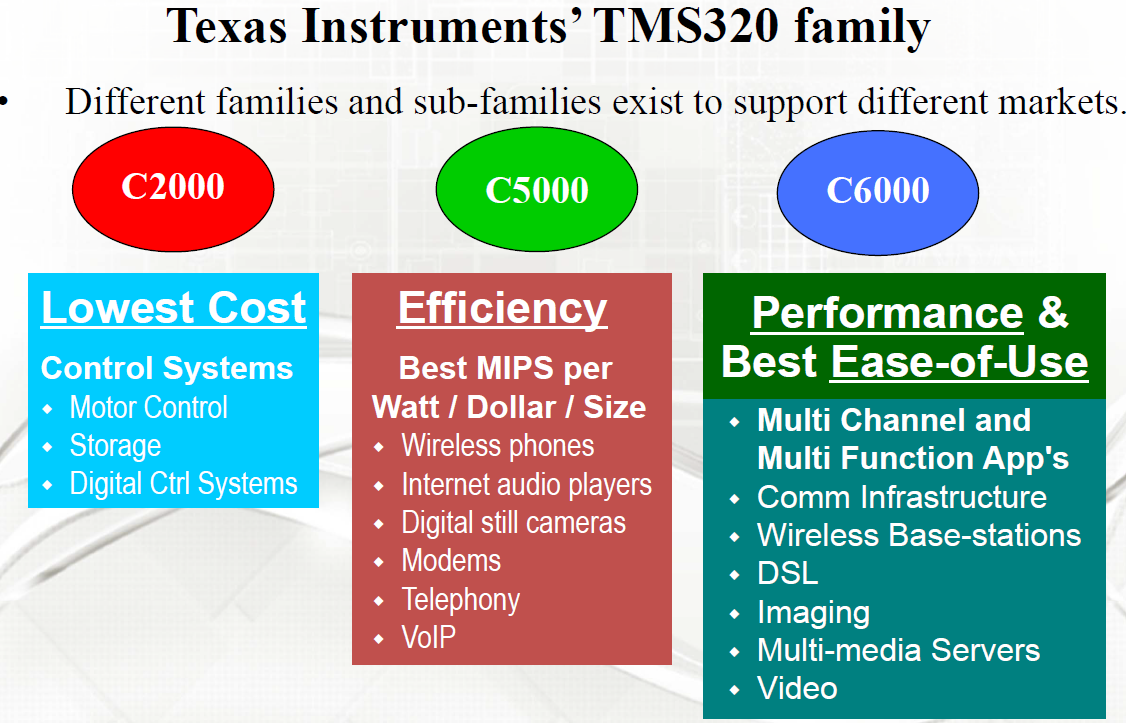

按用途分:通用、专用(C2000、C5000、C6000)

1.3 发展

1980年,日本NEC公司推出第一个具有乘法器的商用DSP芯片PD7720

2. TMS320F28335功能结构

2.1 概述

-

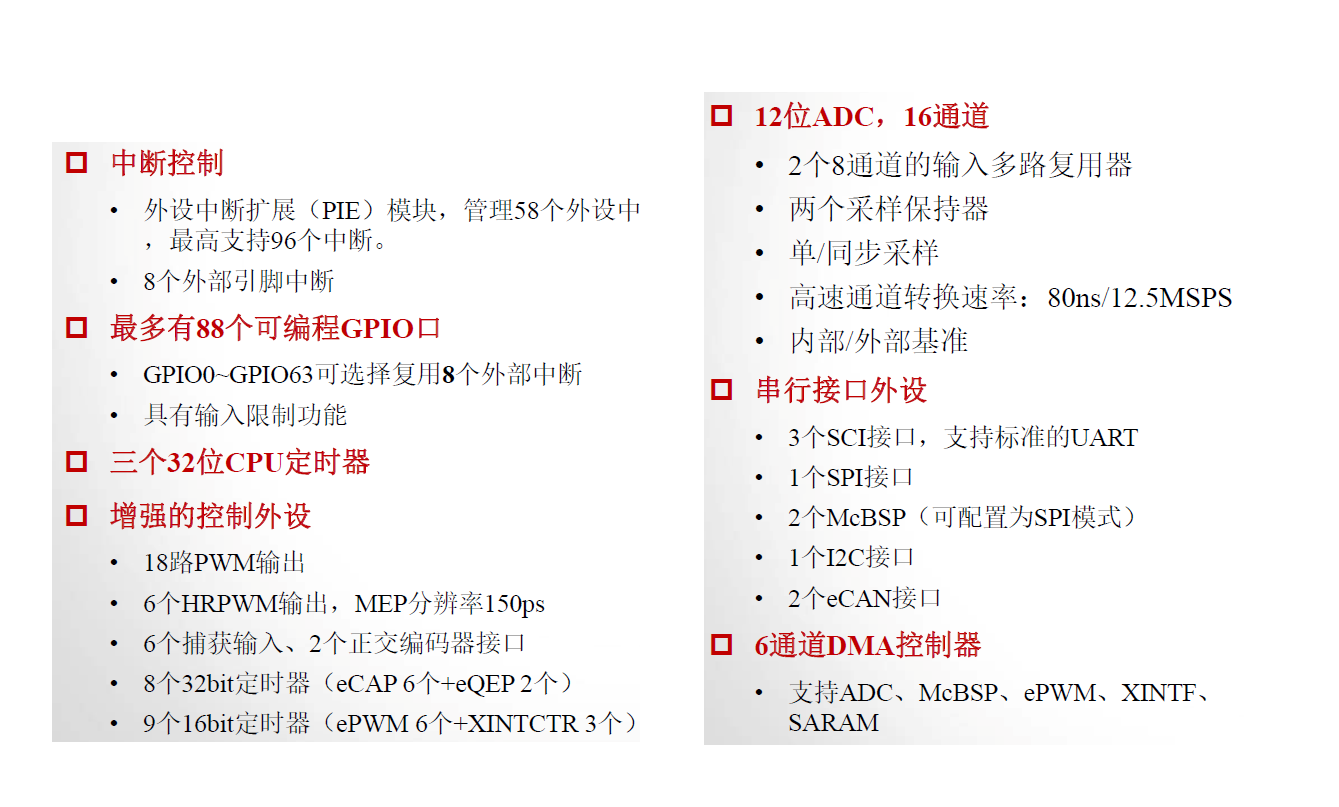

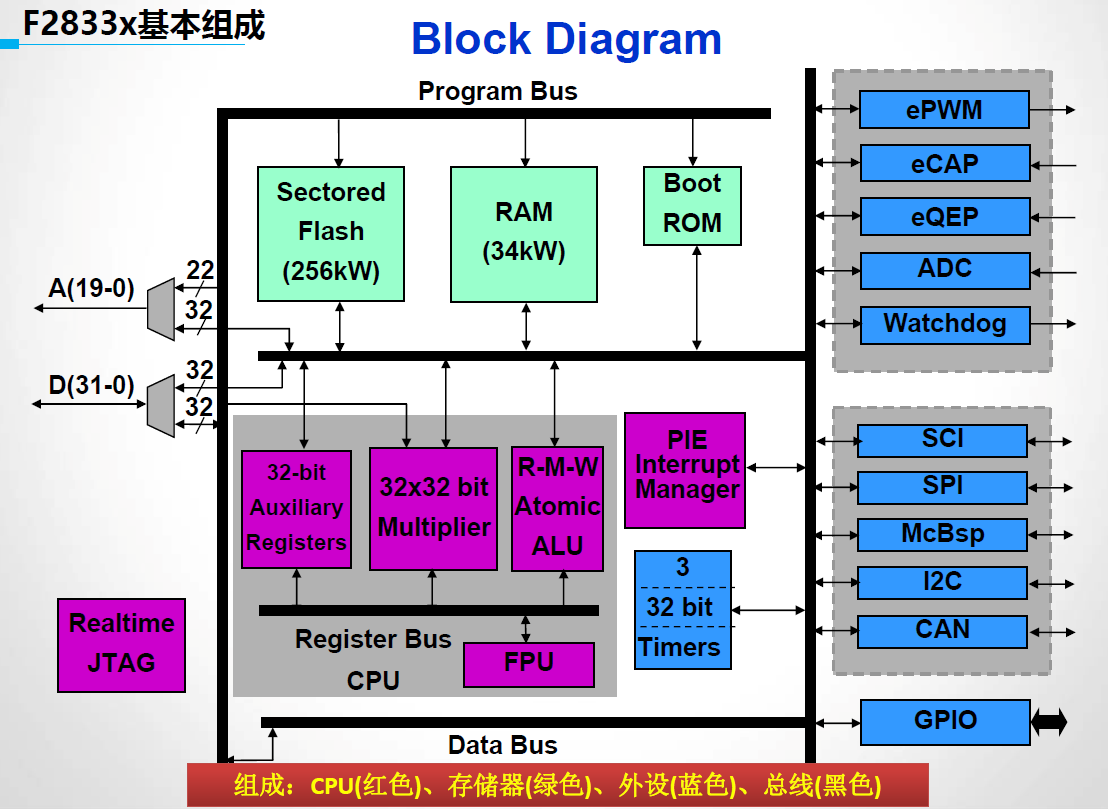

CPU

- 32位定点CPU @150MHz

- 单精度FPU @150MHz

- 硬件乘加器

-

内存

- SARAM @34KW

- Flash @256KW

-

外设

- 控制类:I/O、定时器、ePWM、DMA

- 测量类:eCAP,正交编码器,ADC

- 通讯类:UART、SPI、I2C、McBsp、eCAN

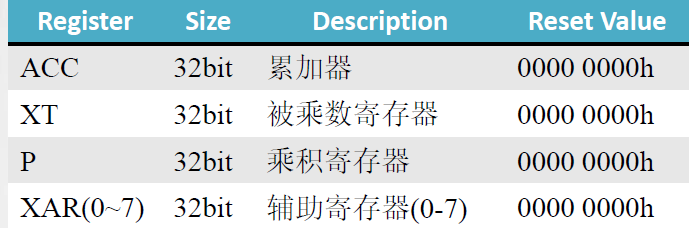

四个32位CPU寄存器

2.2 八级流水线

取指1(F1)、取指2(F2)、译码1(D1)、译码2(D2)

读1(R1)、读2(R2)、执行(E)、写(W)

一条指令一旦到达D2阶段,该指令将一直执行完毕

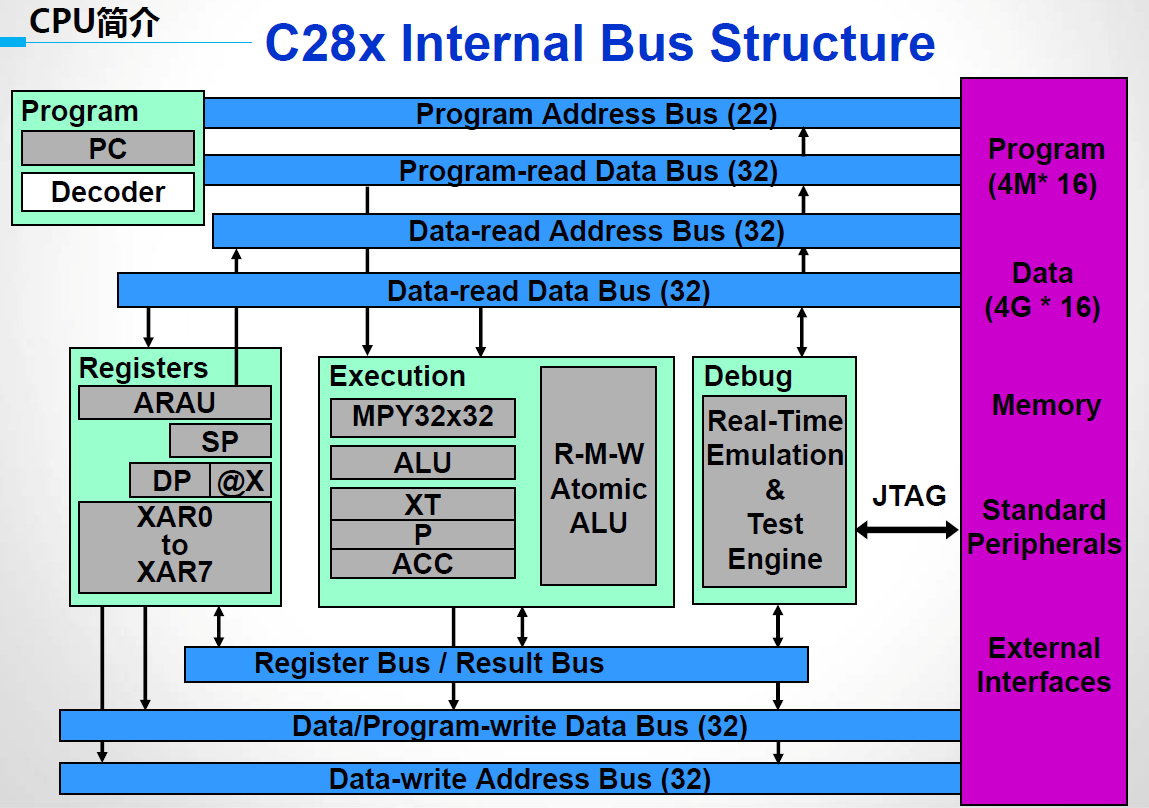

2.3 总线结构

程序读总线、数据读总线、数据写总线(程序写数据总线与数据写数据总线共用)(程序写地址总线与程序读地址总线共用)

各类总线又分为地址总线和数据总线,只有程序地址总线是22位宽(寻址空间4M),其余都是32位宽(寻址空间4G)

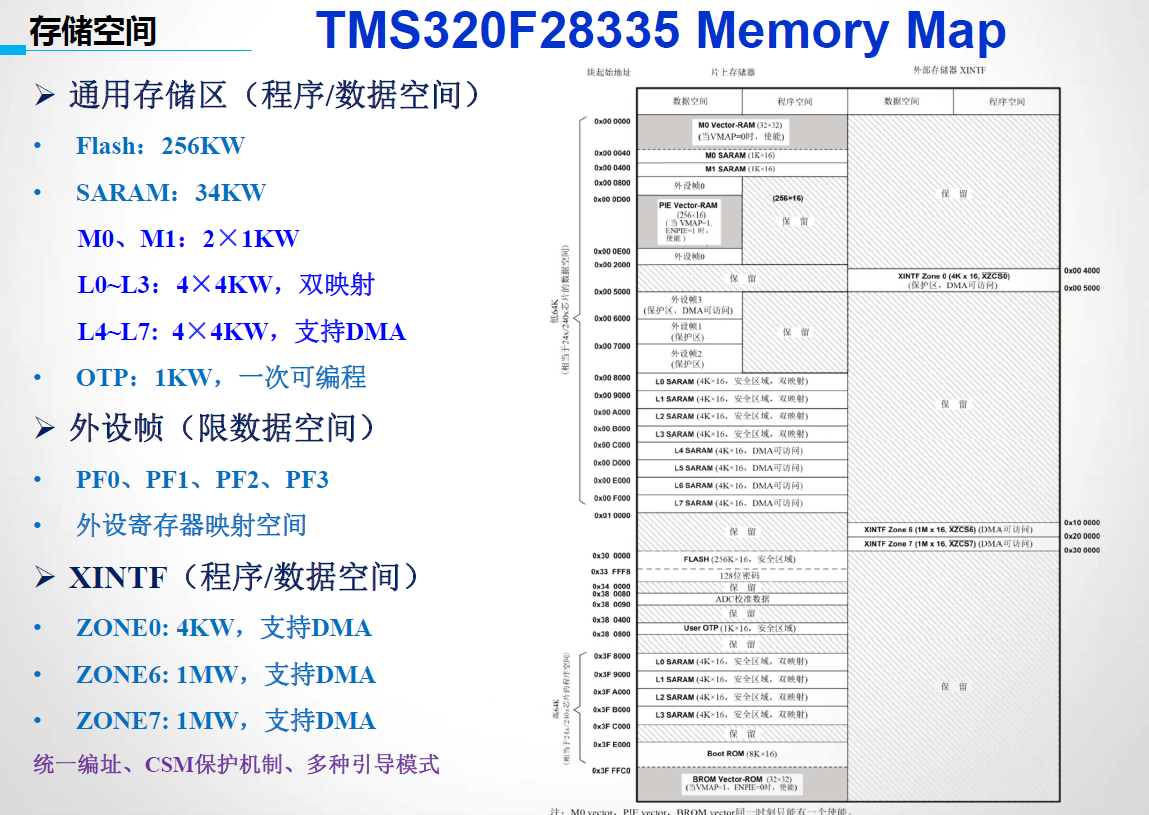

2.4 存储空间

受保护区域:FLASH(128位CSM密码区)、L0~L3 SARAM、OTP

3. 时钟与系统控制

3.1 锁相环PLL

功能:接收外部输入时钟,倍频后产生CPU时钟和系统时钟

3.2 看门狗Watchdog

功能:防止系统死机,确保程序正常运行

工作原理:看门狗模块使能时,其中增计数器开始增计数。计数器达到最大值时,产生复位脉冲信号使器件复位。通过“喂狗”指令在计数器达到最大值之前将其清零,使看门狗不产生复位信号。若程序跑飞或死机,“喂狗”指令不能在看门狗计数周期内得到执行,则计数器溢出产生复位信号使器件复位,从而使器件恢复正常运行。

工作时基为振荡器时钟OSCCLK(未经PLL倍频)

DSP复位时,看门狗默认开启

喂狗指令:向WDKEY寄存器先写入

0x55,再写入0xAA

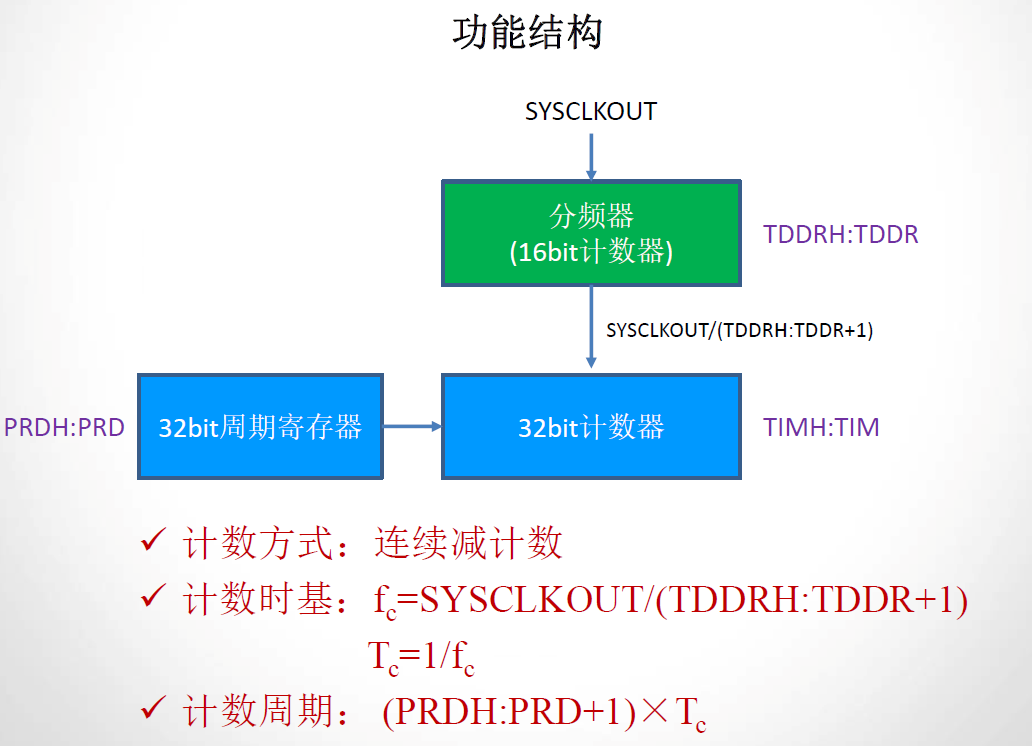

3.3 CPU定时器

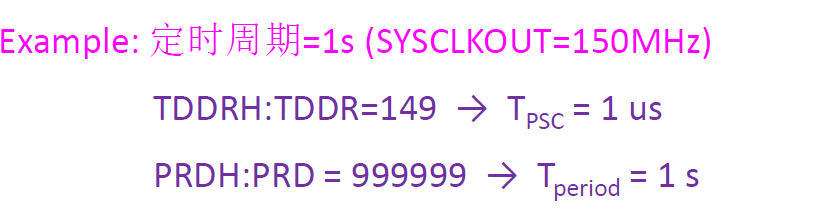

3个32位CPU定时器,TIMER0/1/2,用户程序可使用TIMER0/1,TIMER2为DSP/BIOS保留。减计数

CPU-TIMER0 产生PIE中断,CPU-TIMER1/2直接产生CPU级中断

4. DSP程序结构

4.1 程序文件

-

源程序文件:C/C++、汇编语言文件,功能实现代码;

-

头文件:对基本的数据类型、变量类型进行定义,对常用的数值、指令等进行宏定义,对外部变量、函数进行声明;

-

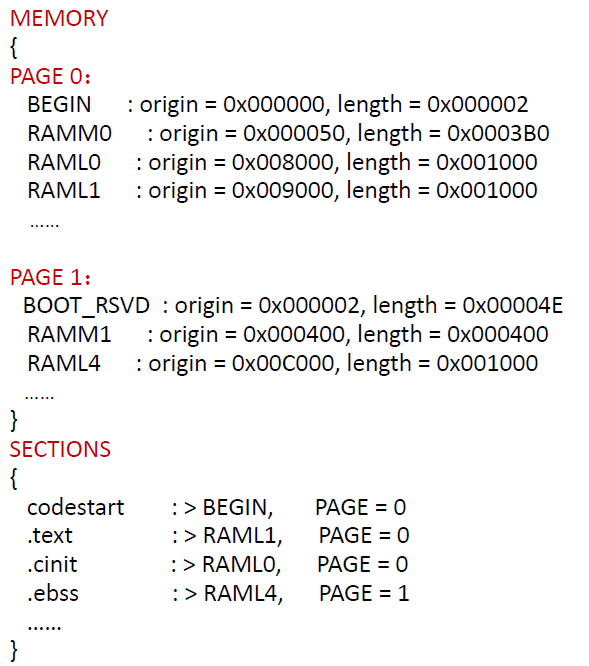

cmd文件:对程序和数据存储空间进行分配;

- Memory:用来标示实际存在目标系统中且可被使用的存储器范围,每个存储器范围具有名字,起始地址和长度。

PAGE0规定程序存储器,PAGE1规定数据存储器 - Sections :描述输入段怎样被组合到输出段内;在可执行程序内定义输出段;规定在存储器内何处放置输出段。

.cinit存放已明确初始化的全局/静态变量的初始值.text可执行代码和常量(立即数).econst已明确初始化的字符串、全局/静态常量(const声明).ebss存放未初始化的全局/静态变量;存放已明确初始化的全局/静态变量,程序复位后从.cinit中将初始值拷贝过来.stack定义栈空间,用于现场保存、存放局部变量 - Memory:用来标示实际存在目标系统中且可被使用的存储器范围,每个存储器范围具有名字,起始地址和长度。

-

运行支持库:C编译器所支持的ANSI标准运行支持函数、I/O函数、编译器公用程序函数和数学运算等。

5. GPIO

5.1 GPIO概述

-

88个I/O口:A组GPIO0–31(32个),B组GPIO32–63(32个),C组GPIO64–87(24个)

-

每个I/O口最多复用为3个外设功能

-

复位默认设为I/O功能输入口

-

支持8个外部中断功能

-

可提供4mA驱动电流

5.2 相关寄存器功能

以A组I/O为例

GPAMUX1 GPIOA(0~15)功能选择;GPAMUX2 GPIOA(16~31)功能选择

GPADIR GPIOA方向选择(输入/输出)

GPAQSEL1、GPAQSEL2 GPIOA输入限制模式:SYSCLKOUT同步、采样窗限制、异步输入

GPAPUD GPIOA上拉功能配置

GPADAT GPIOA读写寄存器(一般情况下,GPxDAT作为GPIO输入寄存器使用,用于读取I/O引脚的电

平状态)

GPASET 拉高

GPACLEAR 拉低

GPATOGGLE 翻转

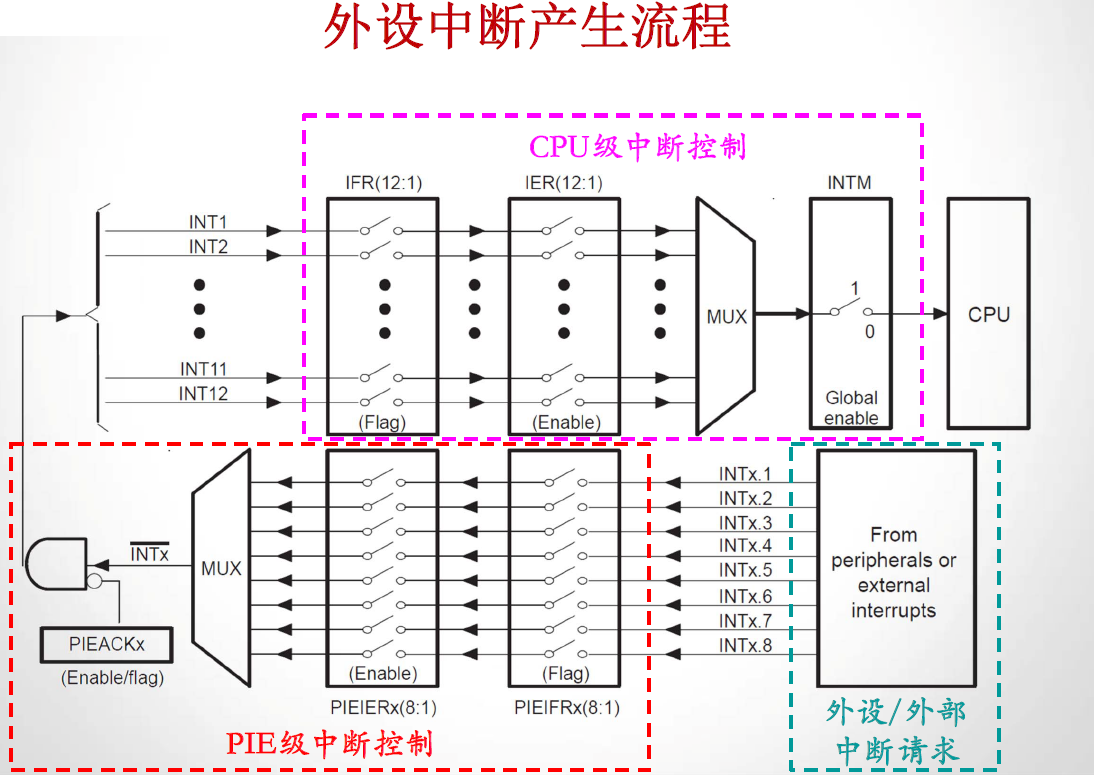

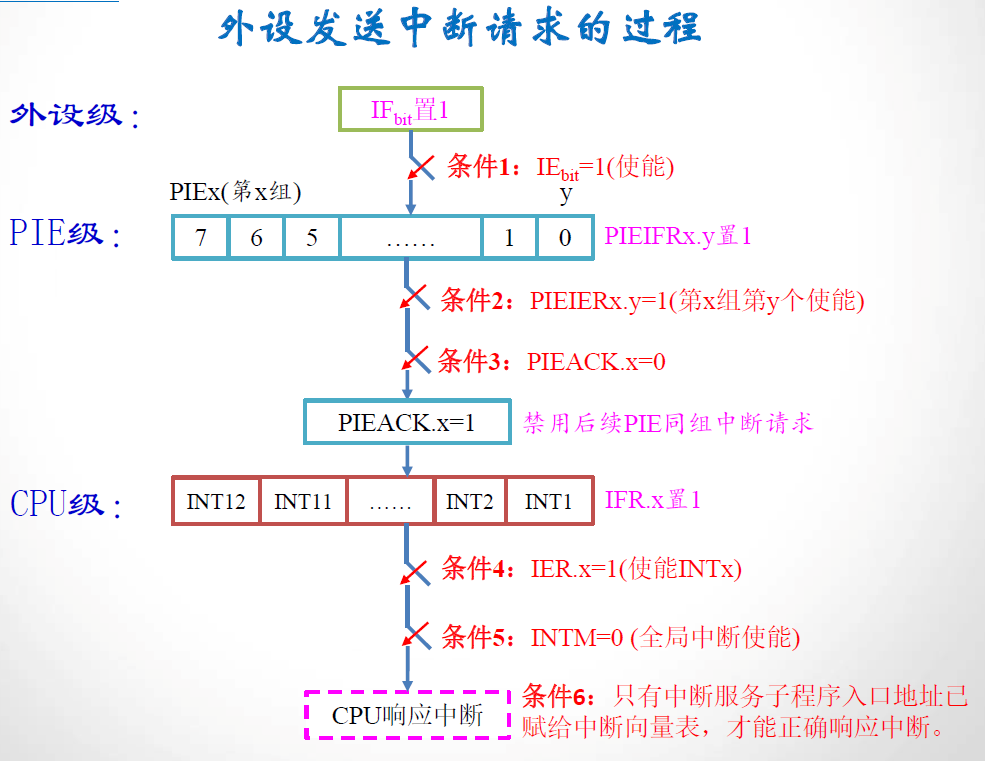

6. 中断管理控制

6.1 中断概述

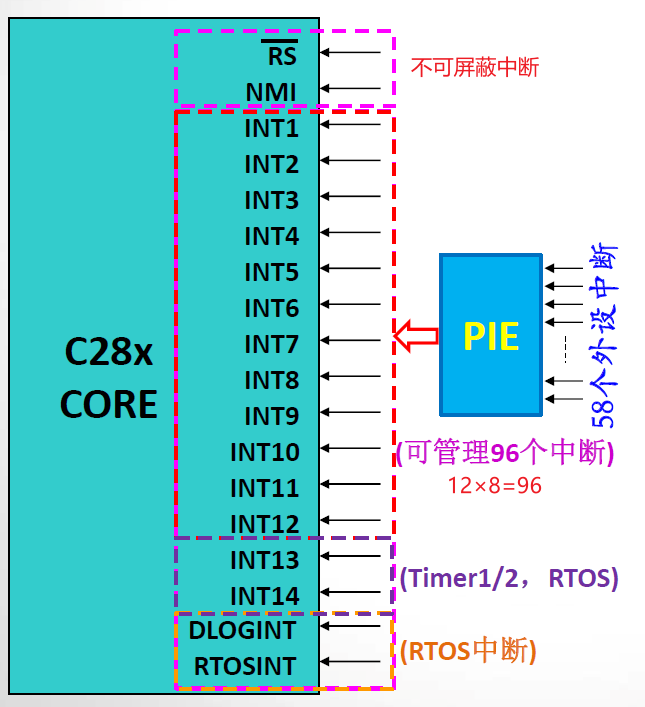

18个CPU级中断,2个不可屏蔽中断,16个可屏蔽中断

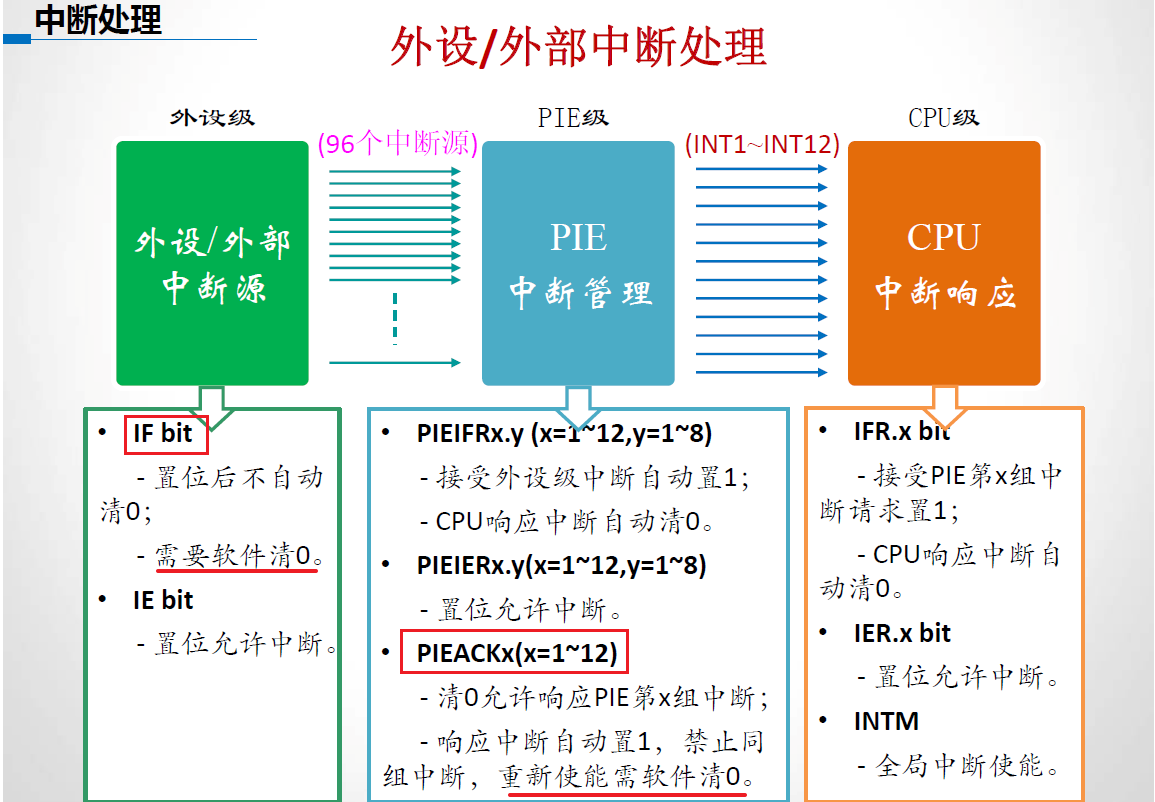

6.2 三级中断控制

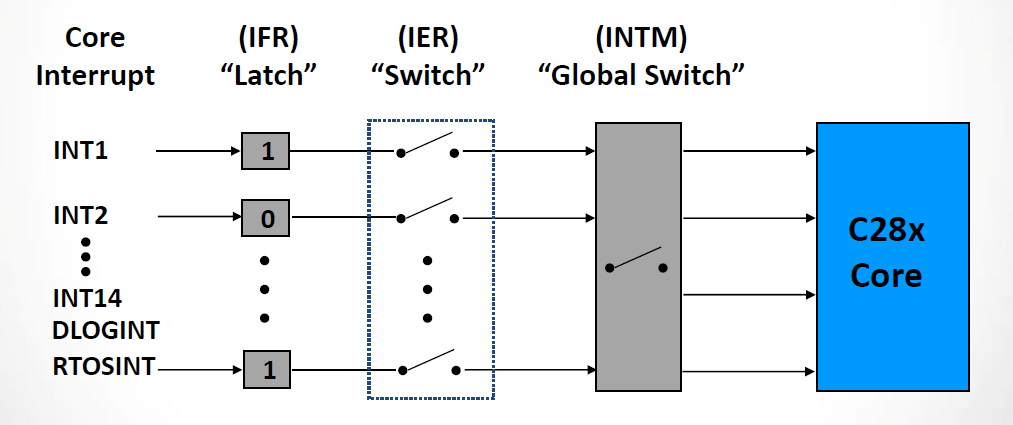

CPU级

中断标志寄存器(IFR):系统复位自动清0,响应硬件中断自动清0,亦可用户手动清0

中断使能寄存器(IER):系统复位默认清0,响应硬件中断自动清0,亦可用户手动清0

全局中断使能位INTM

PIE级

PIE可管理96个中断,8个/组×12组,对应CPU级INT1~INT12,F28335中只使用了58个中断资源

PIEACKx位为0时,允许INTx组向CPU发送中断请求;

PIEIFRx.y和PIEIERx.y同时为1时,PIE自动将PIEACKx置1,同时向CPU发送INTx组的中断请求;

PIEACKx置1后,禁止INTx组的后续中断请求,需软件写1清0;

外设级

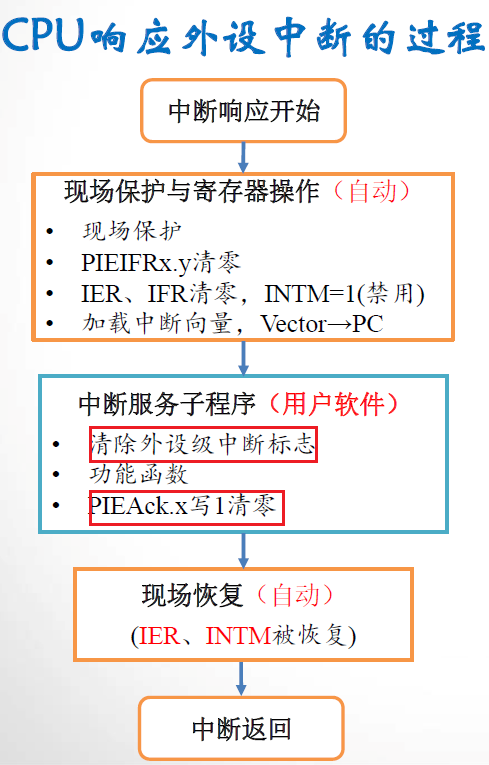

6.3 中断处理过程

6.4 补充

中断向量与中断向量表

中断向量:中断服务程序的入口地址,CPU响应中断后需获取中断向量来开始执行中断服

务程序;

中断向量表:存储中断向量的地址空间,占用256×16的SARAM区

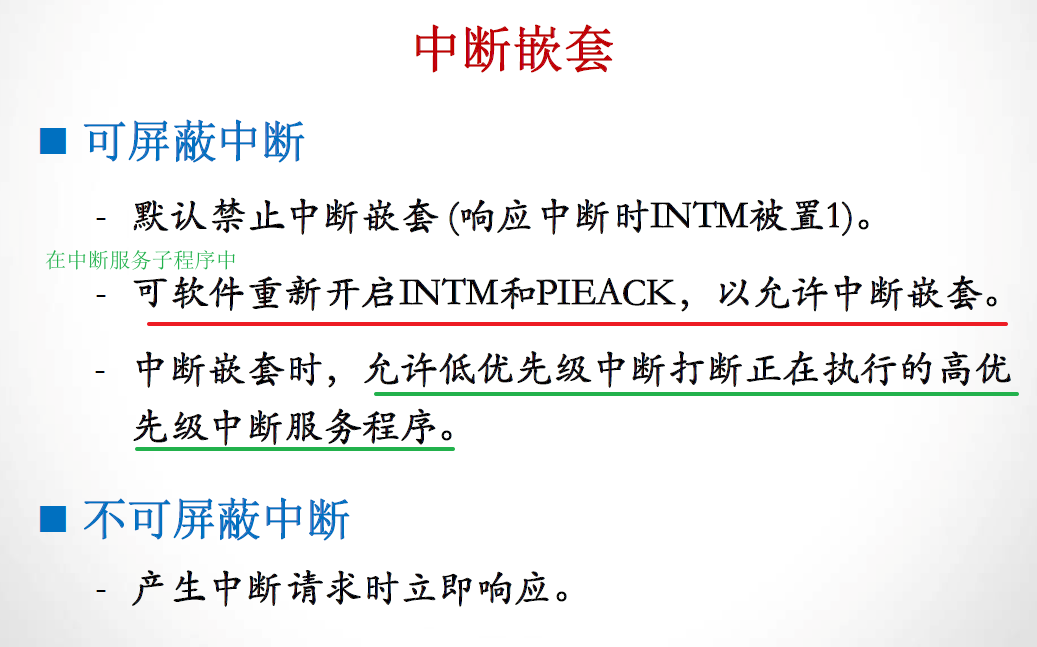

中断嵌套

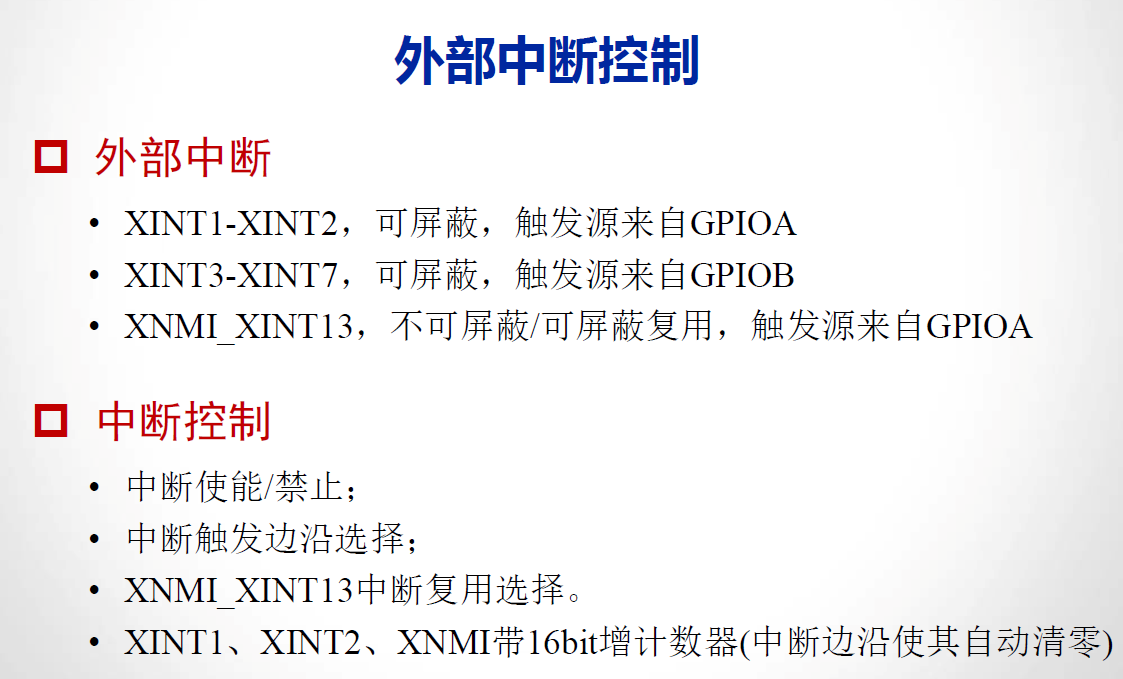

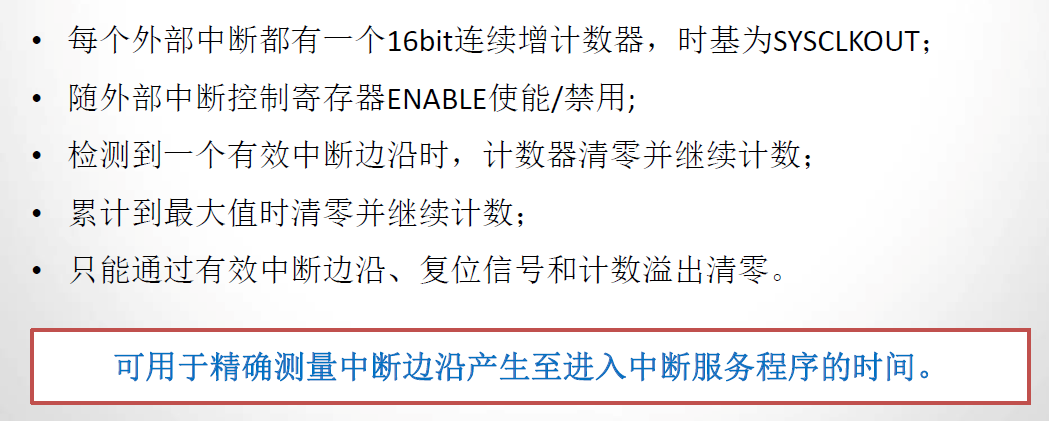

外部中断

7. 增强型脉宽调制器ePWM

7.1 概述

拥有6个相同的ePWM模块,每个模块可产生A、B两路PWM输出EPWMA EPWMB 和两路ADC启动脉冲信号SOCA SOCB,多个ePWM模块可级联同步工作;

基本用途:定时,PWM驱动,启动ADC(控制采样率)

周期和频率可控的16位时间基准计数器

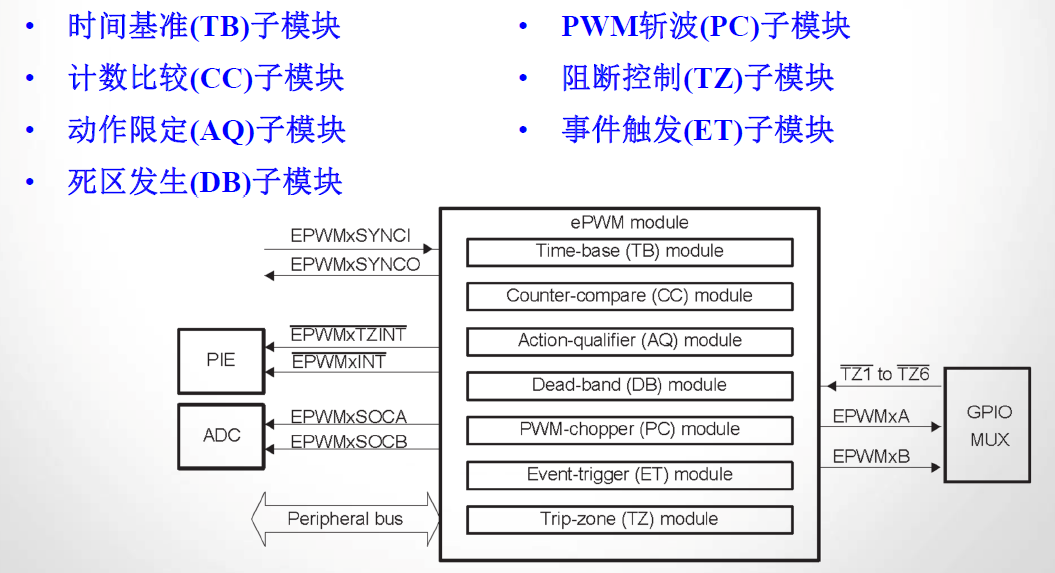

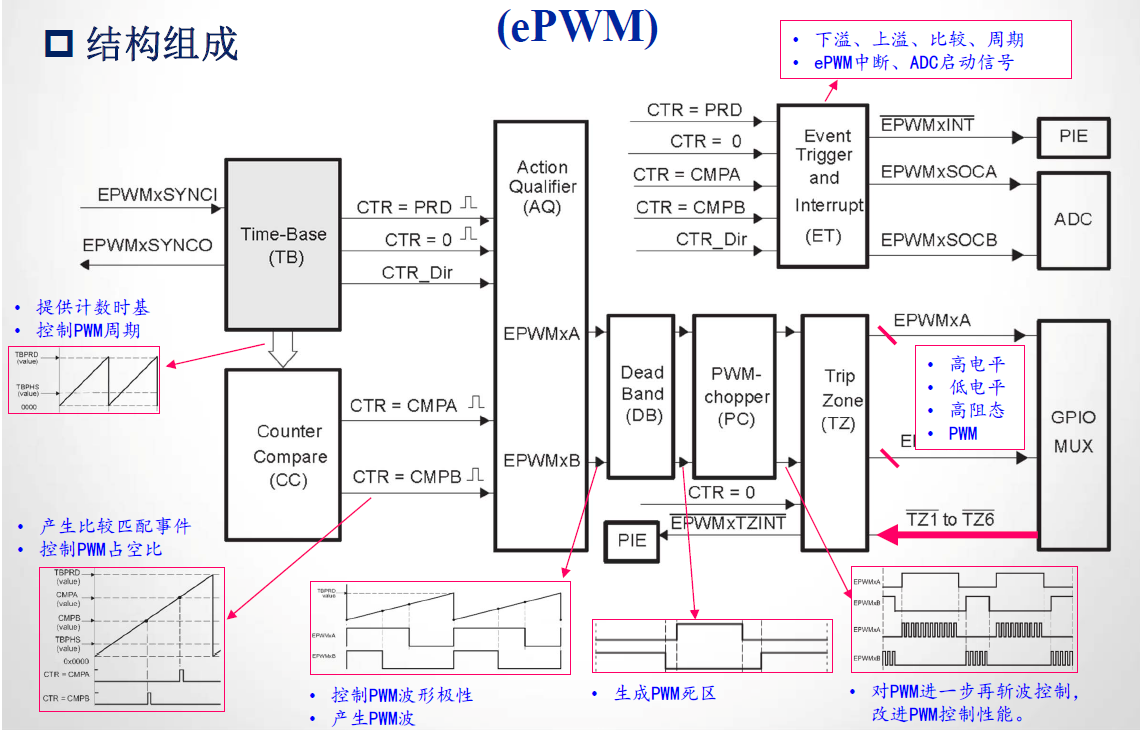

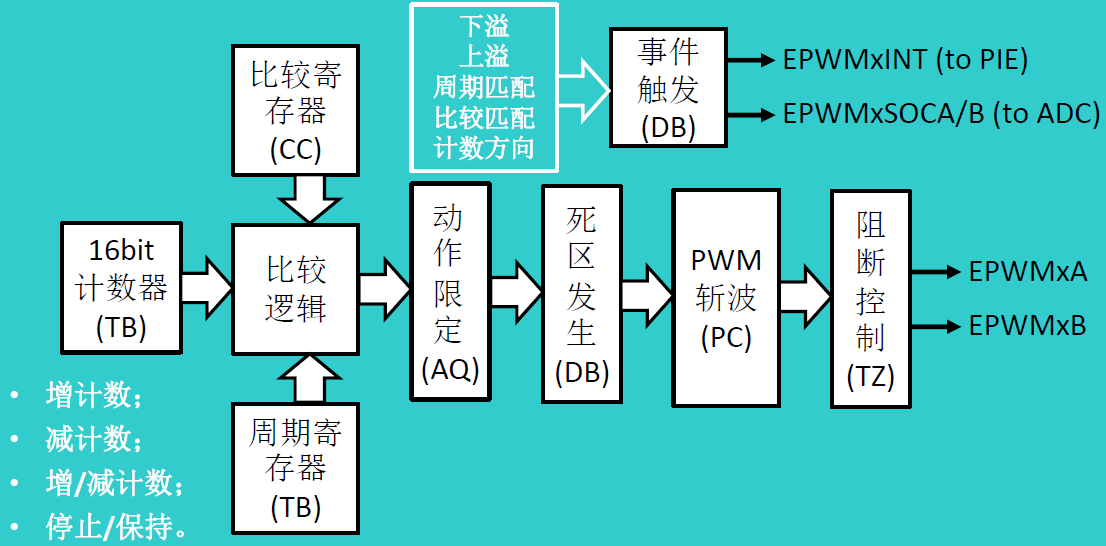

7.2 结构组成

每个ePWM模块包含7个子模块:

AQ动作触发事件优先级:发生较晚的事件具有较高的优先级,软件强制事件优先级最高。

7.3 PWM波形发生示例

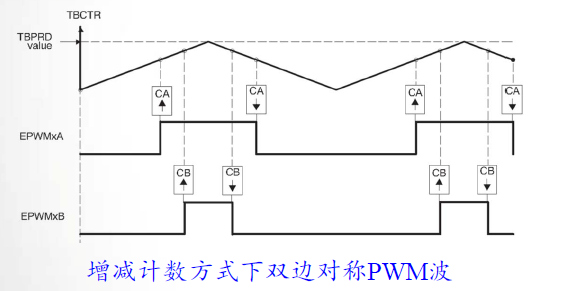

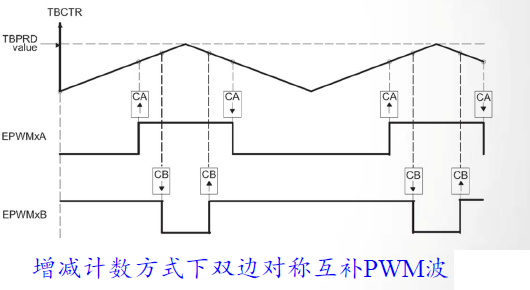

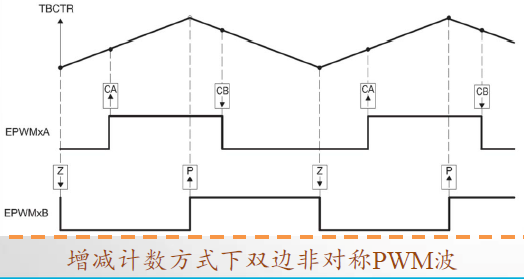

增减计数方式下

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CBD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.PRD = AQ_SET;

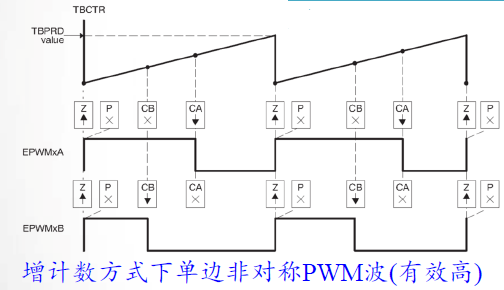

增计数方式下

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;

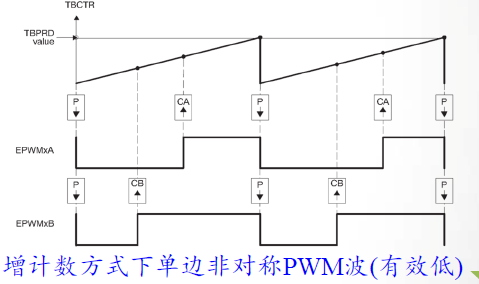

EPwm1Regs.AQCTLA.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLB.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

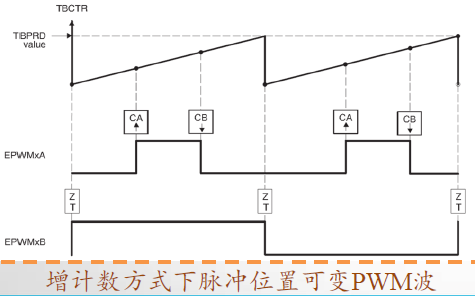

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_TOGGLE;

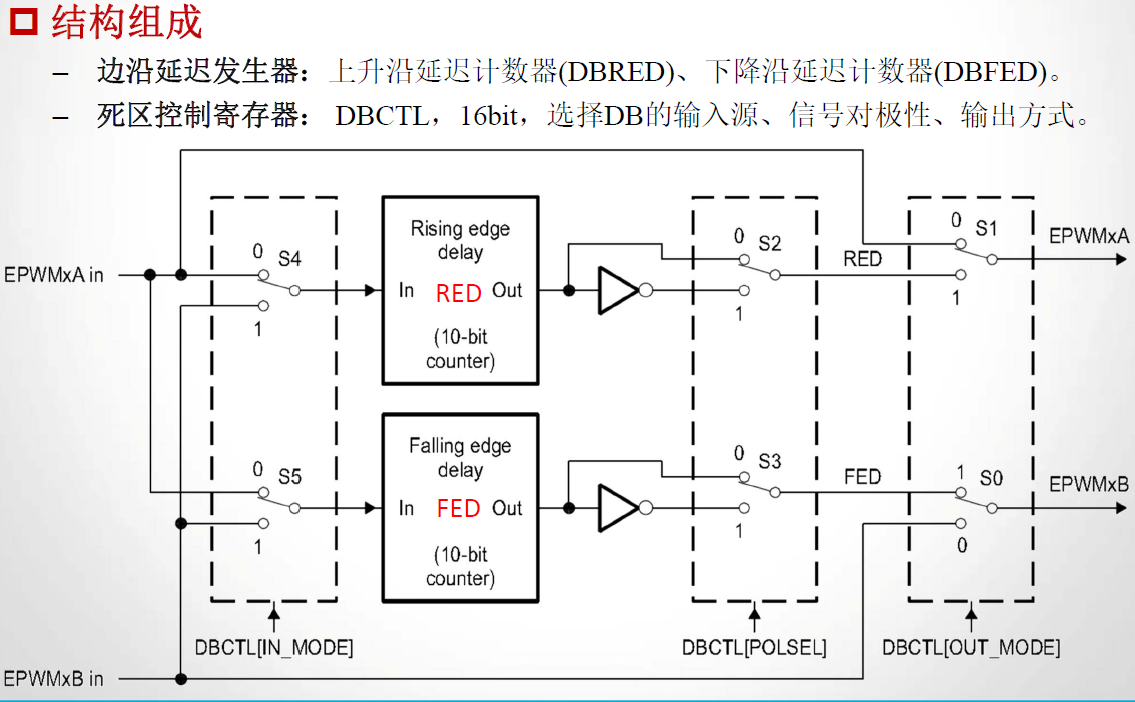

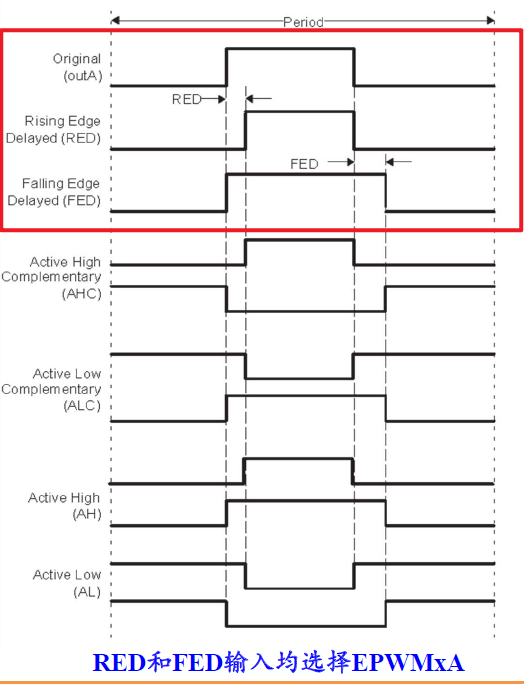

7.4 死区发生(DB)子模块

针对传统需要死区控制的应用,通常选择AQ输出的EPWMxA作为DB的输入,产生一对带死区的EPWMxA和EPWMxB。

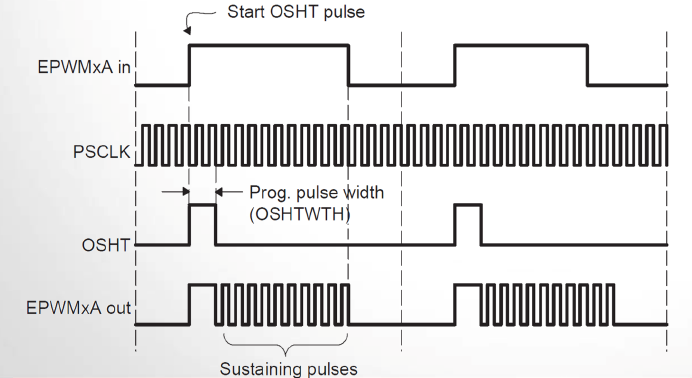

7.5 PWM斩波(PC)子模块

斩波频率可编程;第一个脉冲宽度独立可编程;第二个以后的脉冲占空比可编程。

7.6 阻断控制(TZ)子模块

-

DSP上有6个故障阻断输入引脚TZ1~TZ6,可独立用于检测外部故障信号;

-

阻断动作方式:置高、拉低、高阻、不动作;

-

阻断输入TZn的阻断方式可独立配置为单次阻断(OSHT)和周期阻断(CBC):

- 单次阻断(one-shot trip):单次故障触发、阻断动作持续,需软件清除故障条件,用于主要的短路故障和过流故障保护;

- 周期阻断(cycle-by-cycle tripping):故障条件周期检测、周期动作,故障消失时在新的PWM周期自动清除,用于限流保护。

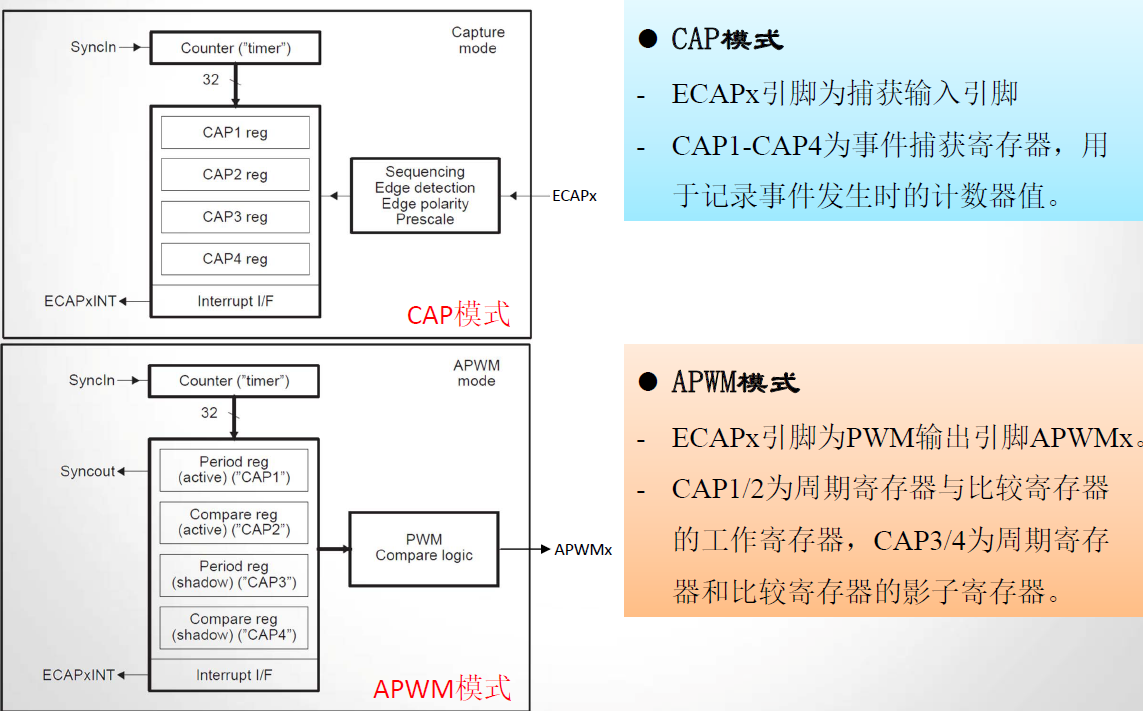

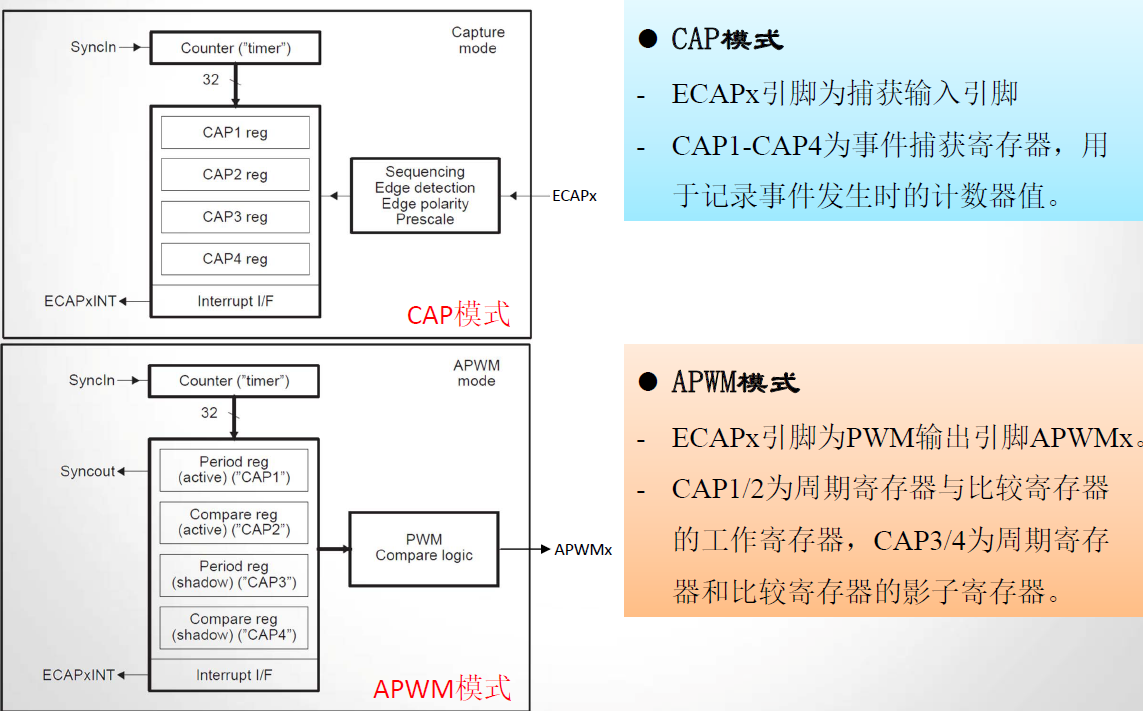

8. 增强型捕获模块eCAP

8.1 CAP模式

基本原理:检测外部引脚边沿(捕获边沿);保存捕获边沿发生时的计数器值。

用途:事件间隔时间测量;脉宽、周期(频率)测量;转速测量。

具有6个相同的eCAP模块,eCAP1-eCAP6,对应有6个捕获输入引脚eCAP1-eCAP6(每个捕获模块有一个捕获输入引脚),支持同步工作模式。

32bit时间戳计数器;

计数时钟:SYSCLKOUT

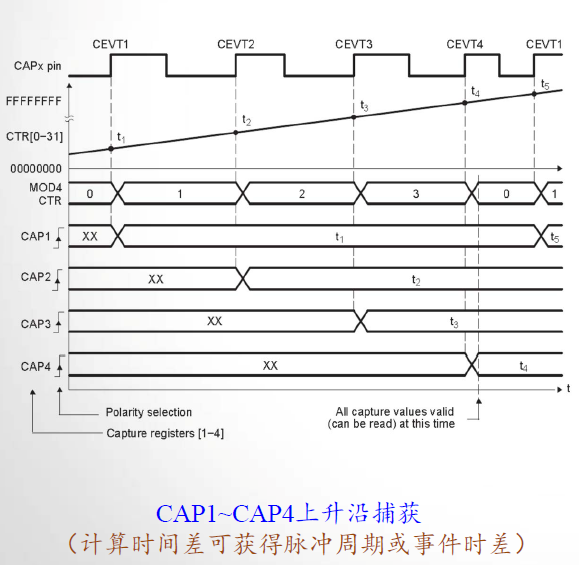

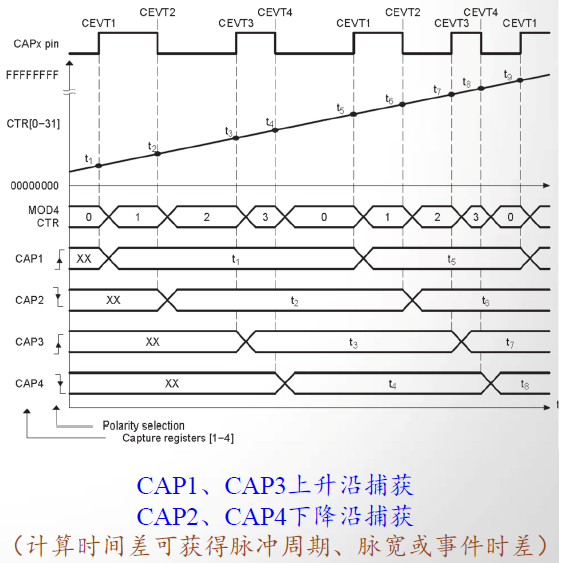

4个事件捕获单元CAP1~CAP4,有独立的时间戳捕获寄存器CAP1-CAP4(32bit),用于记录捕获引脚发生指定事件时的时间戳(计数器值);

绝对时间戳捕获和差分时间戳捕获

单次捕获与连续捕获

不使用CAP功能时,eCAP模块可配置为APWM工作模式,产生一路非对称PWM波

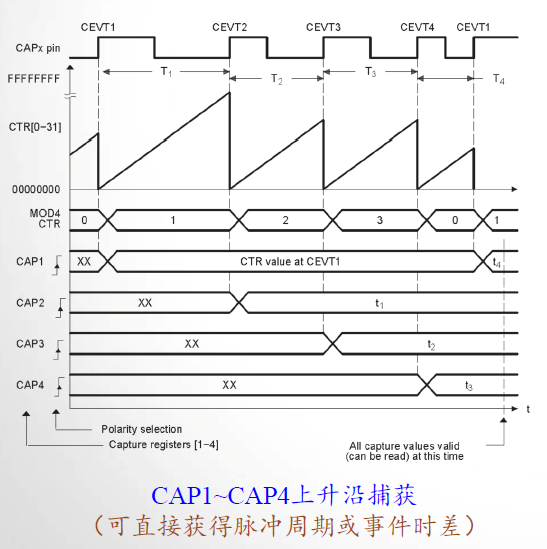

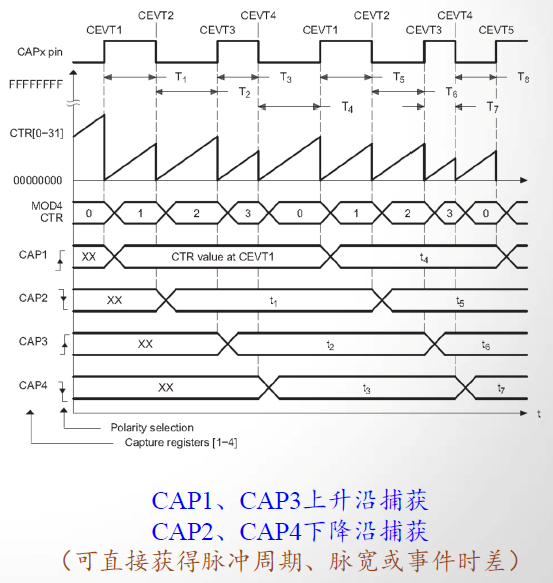

连续捕获

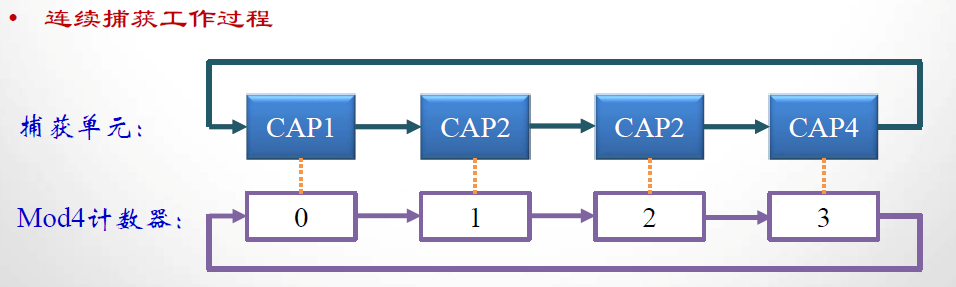

CAP1~CAP4依次连续循环捕获;每发生一次捕获事件,TSCTR值被装载到相应的捕获寄存器CAPx中,Mod4计数器加1;Mod4循环计数过程为0→1→2→3→0→…,依次控制捕获顺序为CAP1→CAP2→CAP3→CAP4→CAP1→…

单次捕获

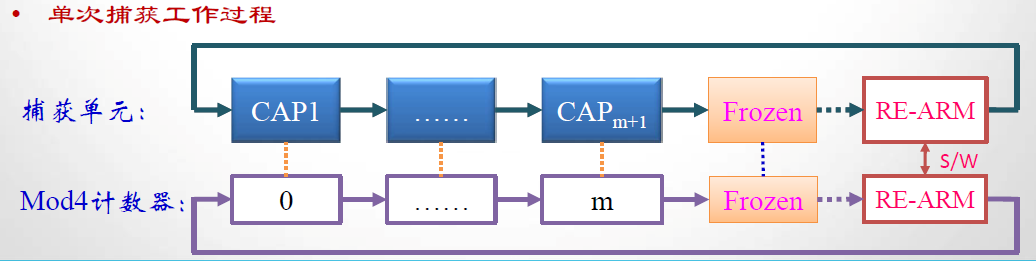

CAP1~CAP4依次捕获,每发生一次捕获事件, TSCTR值被装载到相应的捕获寄存器CAPx中,Mod4计数器加1;当Mod4计数器=[STOP_WRAP]且发生捕获事件后,Mod4计数器值和所有捕获寄存器值被冻结,完成一轮顺序捕获,且禁止后续捕获。软件重新使能捕获([RE-ARM] = 1)时,允许eCAP模块的新一轮顺序捕获,Mod4计数器自动清0并重新开始计数。

绝对时间戳捕获

发生捕获事件CAPx时,TSCTR值被装载入捕获寄存器CAPx中,TSCTR不复位为0而继续计数。

捕获寄存器装载的时间戳为绝对时间,两个事件的时间差需要软件读取捕获寄存器值并相减得到。

差分时间戳捕获

发生捕获事件CAPx时, TSCTR值被装载入捕获寄存器CAPx中,TSCTR复位为0并继续计数。

捕获寄存器装载的时间戳为两事件的时间差(差分时间),软件读取捕获寄存器值可直接得到两事件的时间差。

8.2 APWM模式

分辨率32位

比较寄存器ACMP和周期寄存器APRD均带影子寄存器,可工作在双缓冲模式

影子寄存器装载到工作寄存器的条件:立即、CTR=APRD

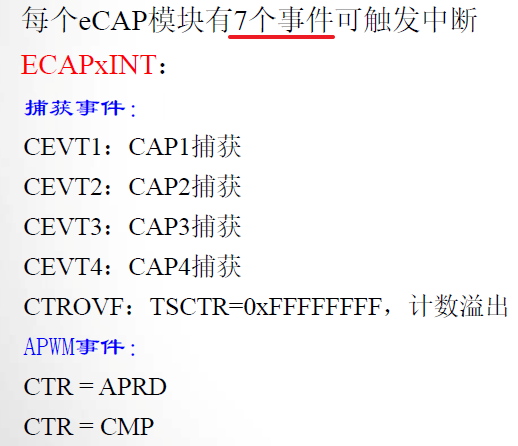

8.3 中断事件

9. ADC

9.1 概述

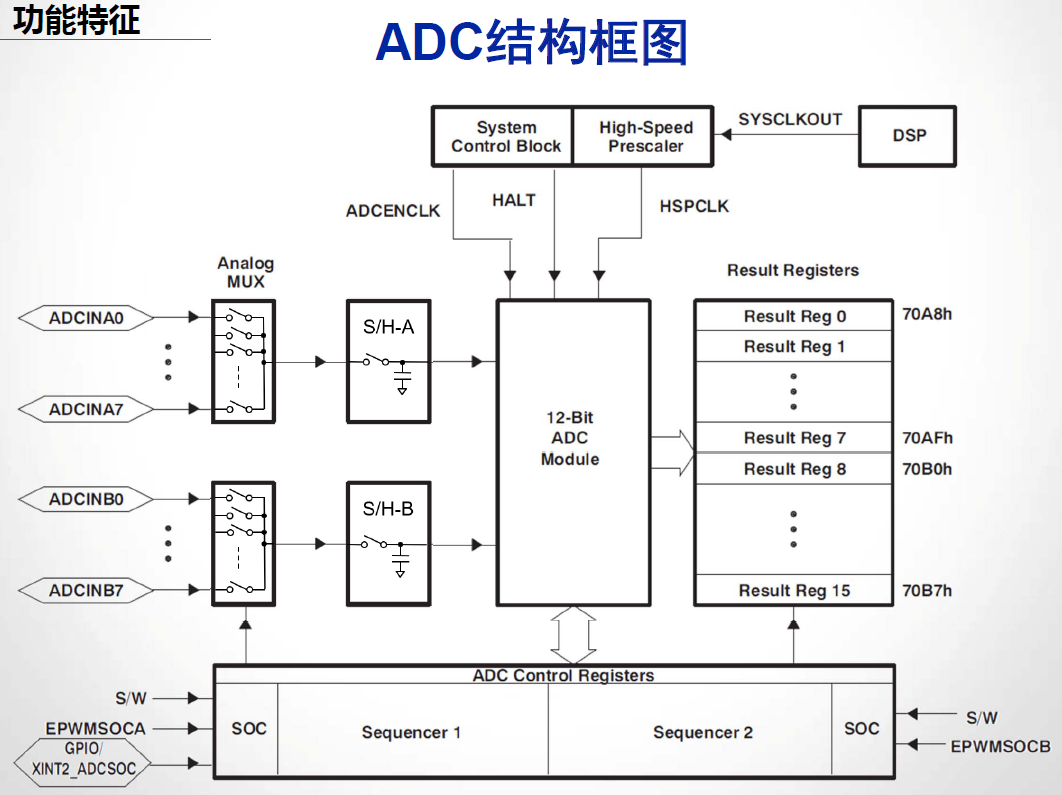

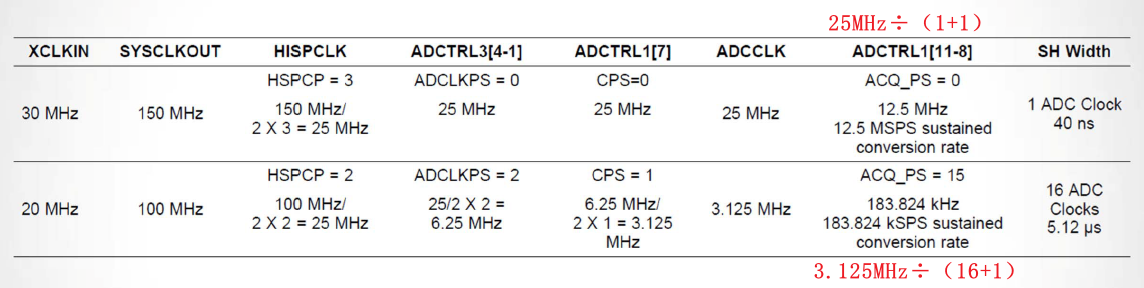

- 单个ADC核,流水线结构(pipeline),12位分辨率

- 最快采样速率为12.5M

SPS(sample per second)(工作在25MHz时钟下,ADC采样率为25MHz÷2=12.5MHz,采样时间最少为一个ADC时钟周期,保持时间为一个ADC时钟周期) - 16个模拟输入通道(模拟电压输入范围:0~3V),(8个通道+多路复用器+1个S/H电路)×2组

- 两种采样模式:同步、顺序

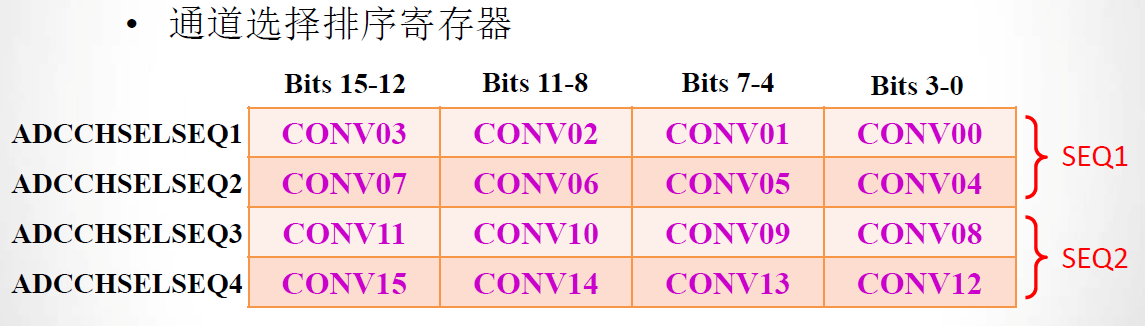

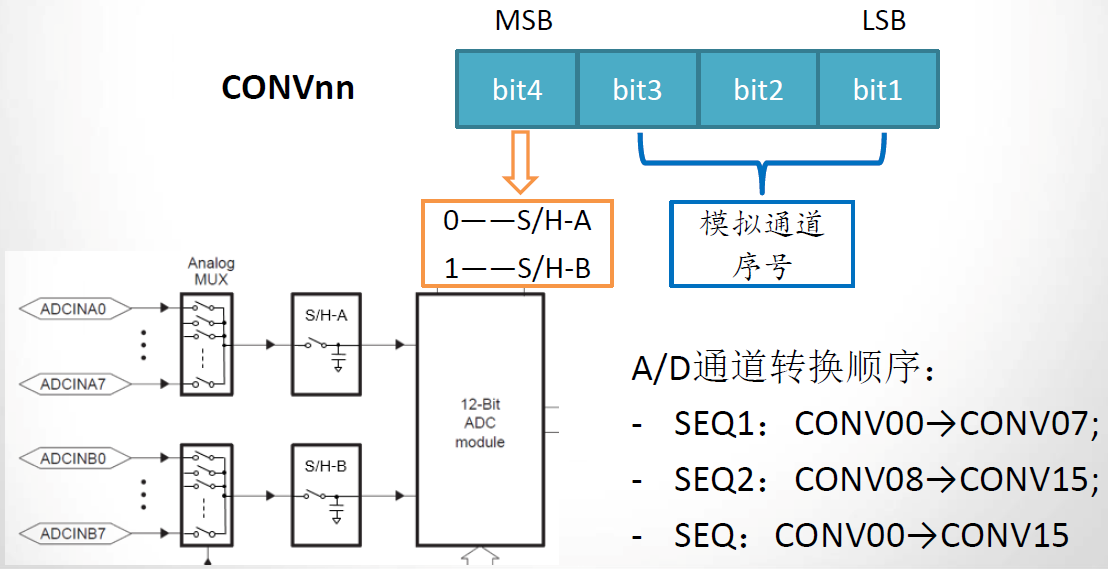

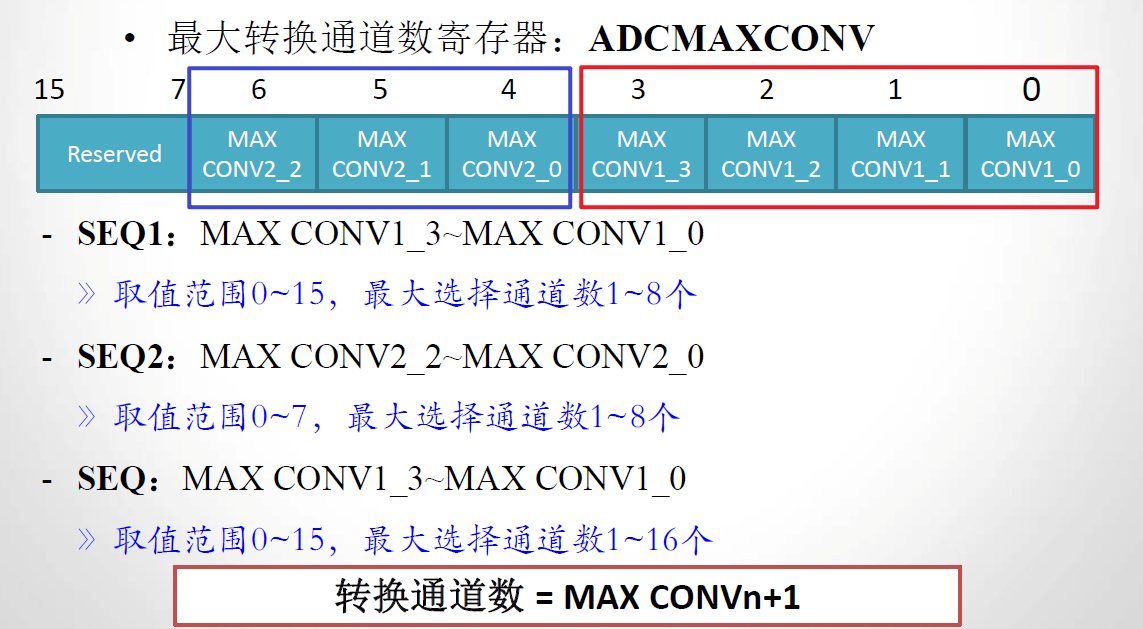

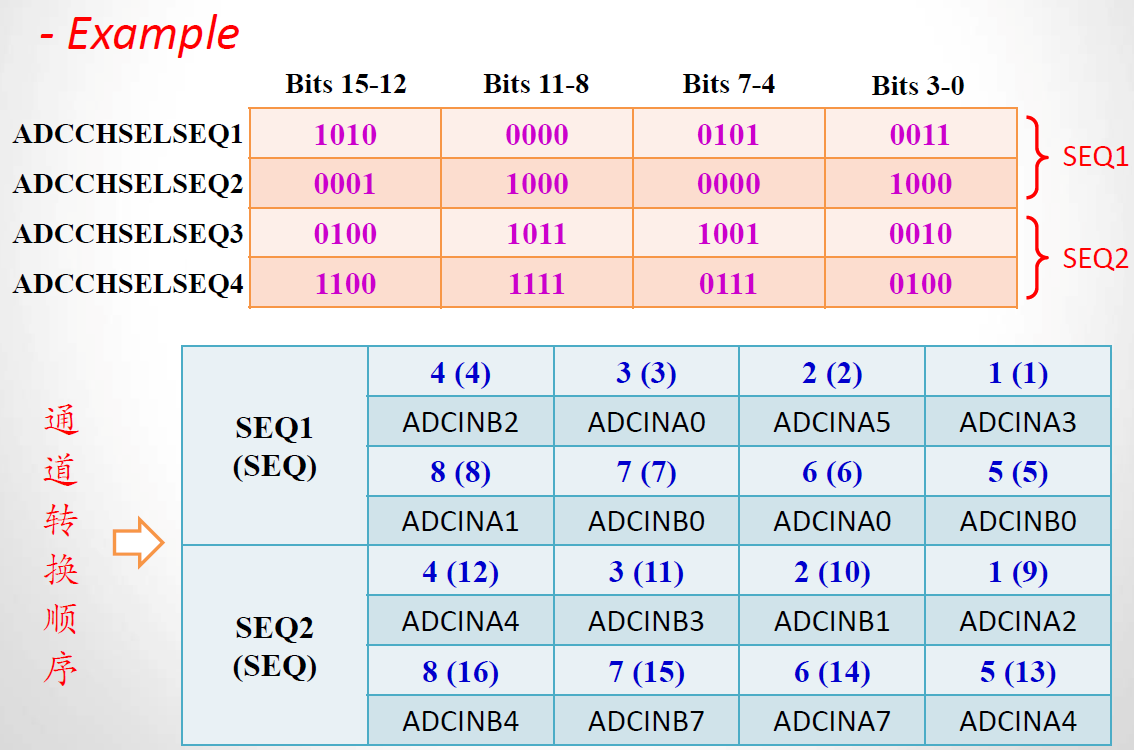

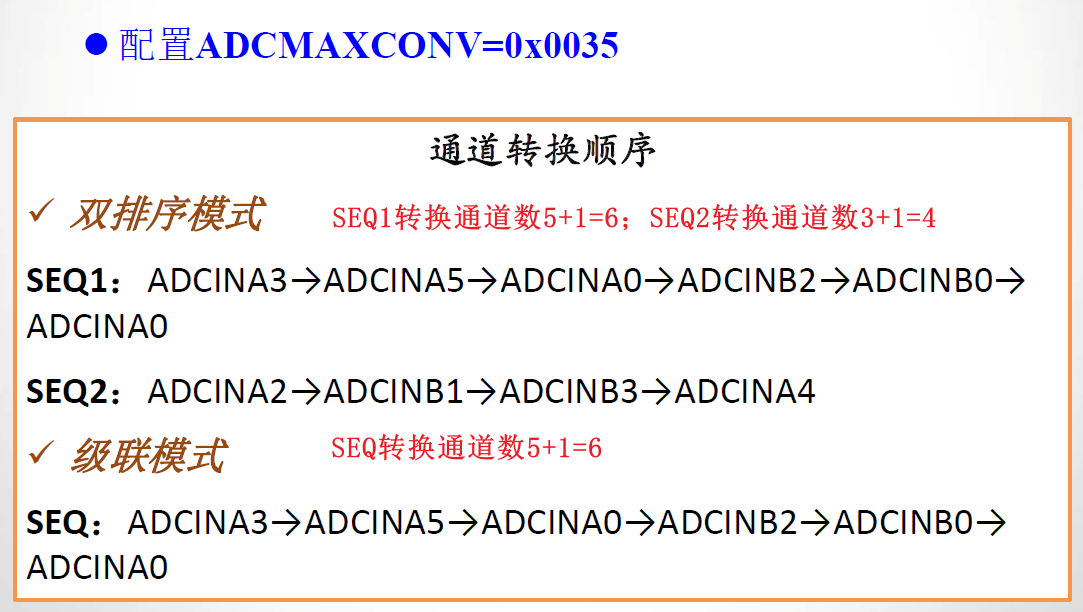

- 通道的转换顺序可由自动排序器决定,一次可执行16个通道的自动转换,每次转换亦可编程选择任何通道

- 两个独立的8通道排序器SEQ1、SEQ2:双排序模式、级联单排序模式

- 16个独立的转换结果寄存器,可单独访问,双映射,支持DMA访问

- 多个SOC(start-of-conversion)触发源:软件直接启动、EPWM1-6的SOCA、SOCB、外部引脚触发GPIO_XINT2

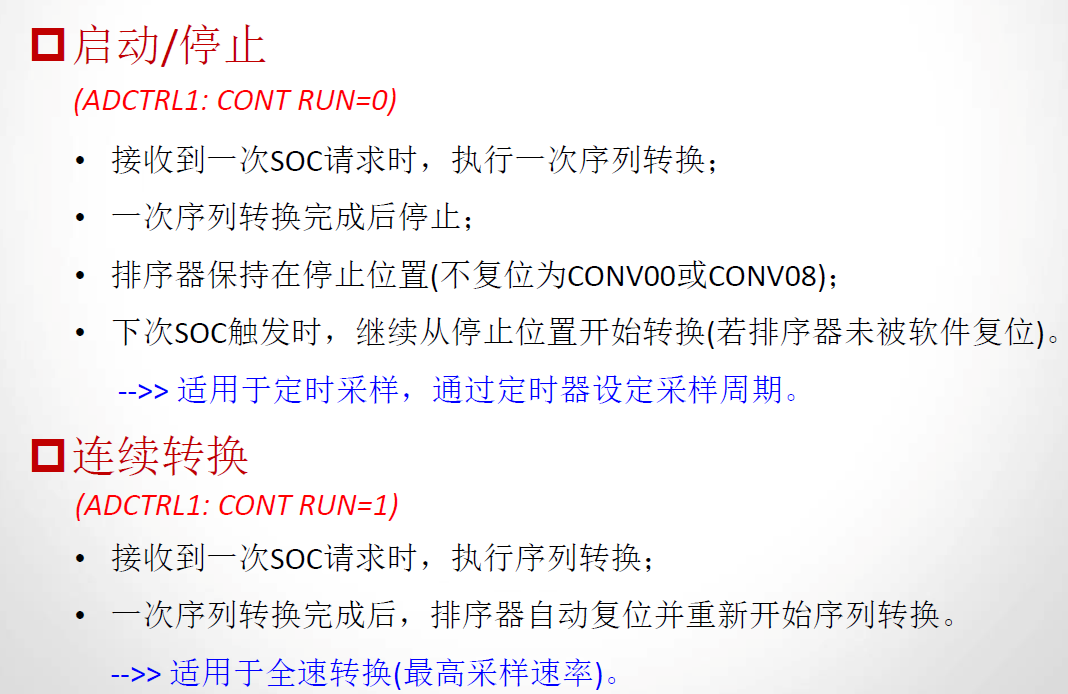

- 转换模式:启动/停止模式、连续转换模式

- 采样窗时间可配置(

ACQ_PS)为1~16个ADC时钟周期

9.2 排序器

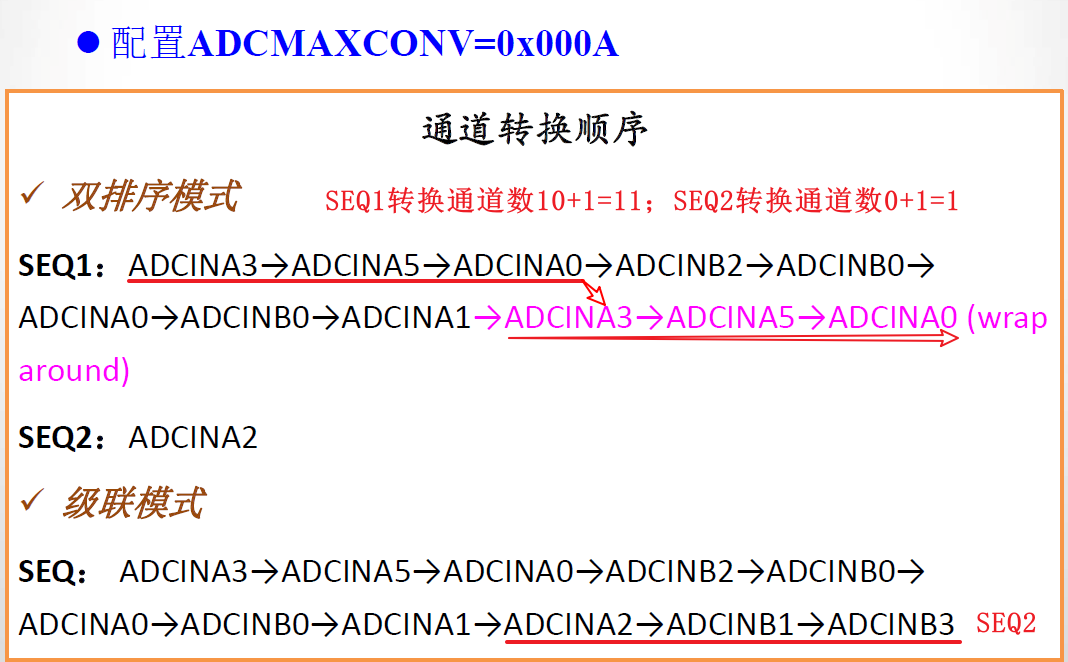

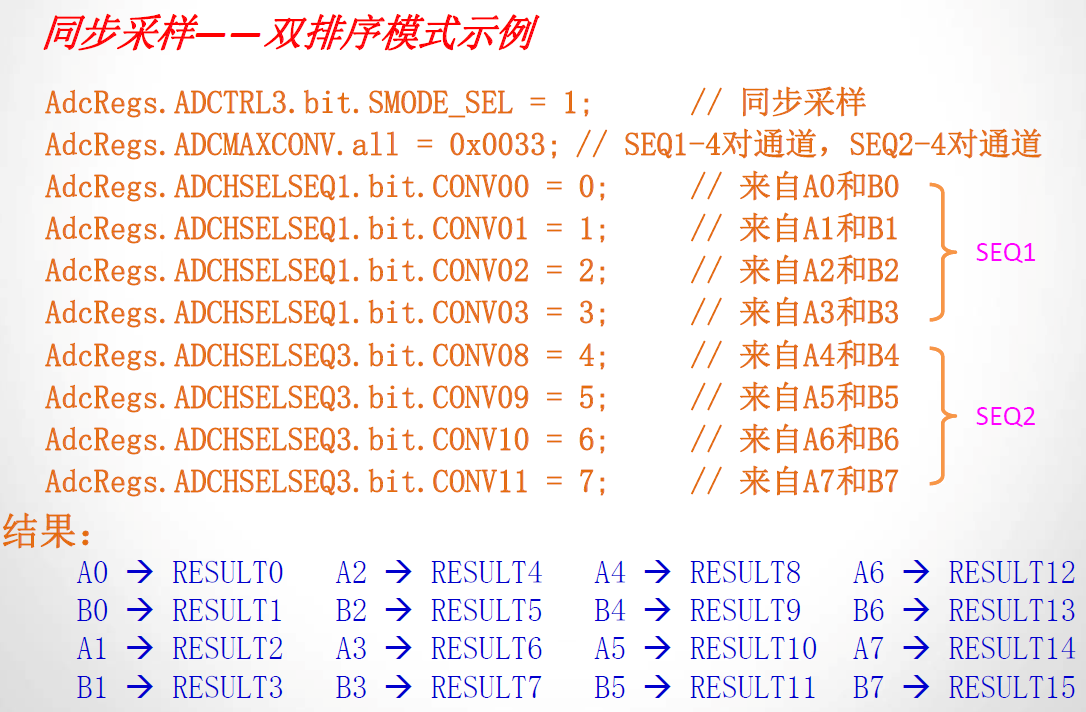

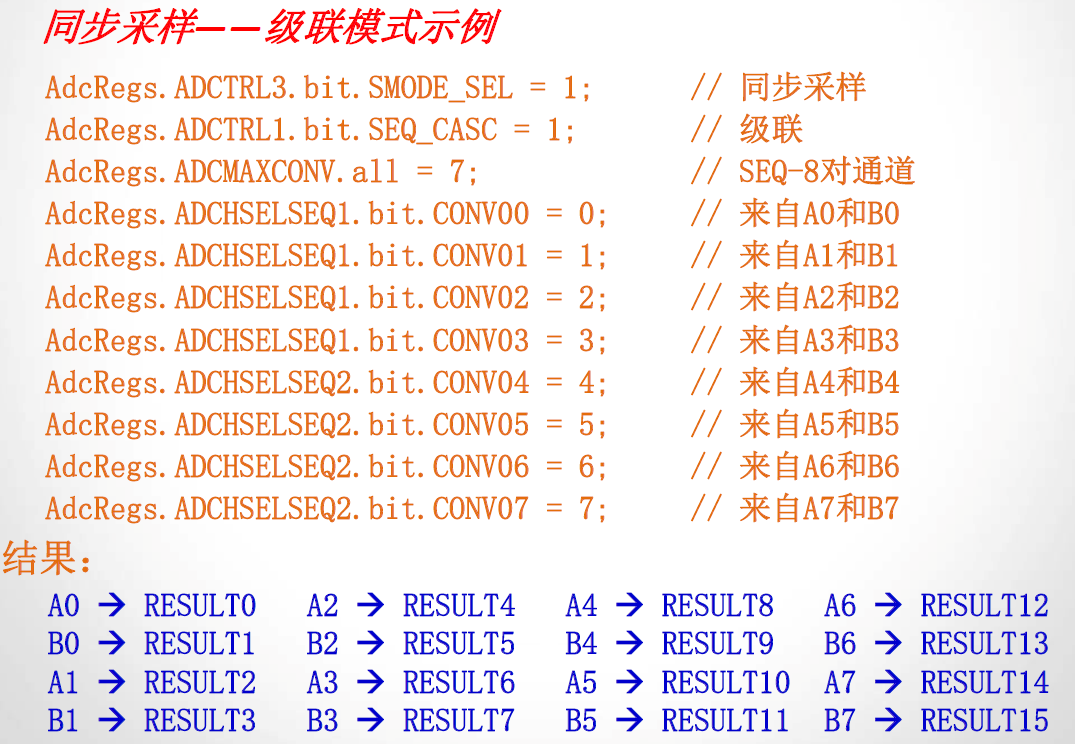

9.3 同步采样

- 忽略CONVnn中的MSB位,同时启用S/H-A和S/H-B;

- 一个排序器通道同时选中ADCINAx和ADCINBx进行采样/保持;

- ADC核先转换ADCINAx,再转换ADCINBx;

- ADCINAx和ADCINBx转换结果分别存放在ADCRESULTn和ADCRESULTn+1中。

9.4 启停/连续转换模式

连续转换:fsmax=ADC采样率/通道数;启停模式:fs=SOC触发频率≤fsmax

ADC采样率计算方式,Example

假设ADCCLK = 25MHz,

ACQ_PS=3,则采样时间为ACQ_PS+1=3+1=4个ADC时钟周期,保持时间为1个ADC时钟周期,ADC采样率为25MHz÷(4+1)= 5MHz。

- ADC采集(采样&转换)一点数据需要多少时间?

答:ADC采样率为5MHz,采样周期t=1÷5MHz=0.2us

CONV00 = 3,ADCMAXCONV=0x0000, 在顺序采样模式、连续转换模式下,启动SEQ1时,ADC转换哪些模拟输入通道?信号采样率是多少?答:ADC转换ADCINA3通道,信号采样率为5MHz÷1=5MHz。

CONV00 = 3,ADCMAXCONV=0x0000, 在同步采样模式、连续转换模式下,启动SEQ1时,ADC转换哪些模拟输入通道?信号采样率是多少?答:ADC转换ADCINA3、ADCINB3通道,信号采样率为5MHz÷2=2.5MHz。

CONV00 = 3,CONV01 = 9,ADCMAXCONV=0x0001, 在顺序采样模式、连续转换模式下,启动SEQ1时,ADC转换哪些模拟输入通道?信号采样率是多少?答:ADC转换ADCINA3、ADCINB1通道,信号采样率为5MHz÷2=2.5MHz。

CONV00 = 3,CONV01 = 9,ADCMAXCONV=0x0001, 在顺序采样模式、启动/停止模式下,通过EPWM1(设计数周期=1ms)的下溢事件启动SEQ1,ADC转换哪些模拟输入通道?信号采样率是多少?答:ADC转换ADCINA3、ADCINB1通道,信号采样率为1÷1ms=1kHz。

CONV00 = 3,CONV01 = 9,ADCMAXCONV=0x0001, 在同步采样模式、启动/停止模式下,通过EPWM1(设计数周期=1ms)的下溢事件启动SEQ1,ADC转换哪些模拟输入通道?信号采样率是多少?信号采样率最高可设为多少?答:ADC转换ADCINA3、ADCINB3和ADCINA1、ADCINB1通道;信号采样率为1÷1ms=1kHz;信号采样率最高可设为5MHz÷4=2.5MHz。

连续转换:fsmax=ADC采样率/通道数;启停模式:fs=SOC触发频率≤fsmax

9.5 ADC时钟配置示例

ADC对2.048V的外部基准电压进行了工业标准基准元件匹配

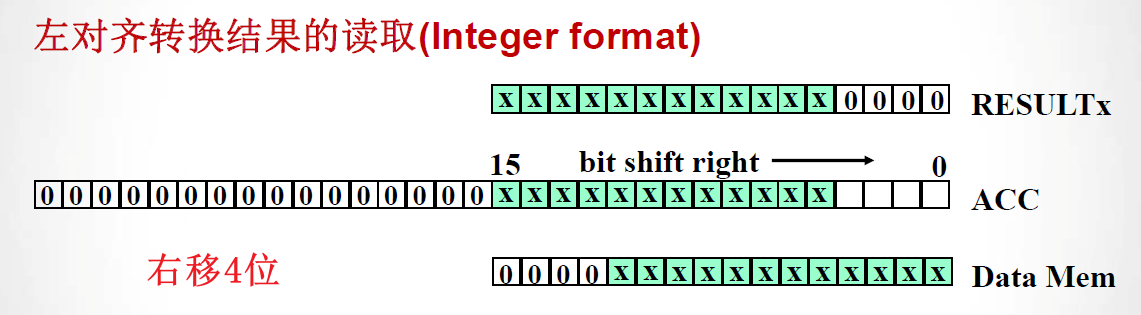

9.6 ADC转换结果

数字量化结果与模拟输入电压之间的转换

D i g i t a l 4095 = I n p u t A n a l o g V o l t a g e 3 \frac{Digital}{4095}=\frac{Input\ Analog\ Voltage}{3} 4095Digital=3Input Analog Voltage

int value;

float voltage;

value = AdcRegs.ADCRESULT0 >> 4;

voltage = (value/4095.0)*3.0;

10. 串行同步通信SPI模块

10.1 SPI概述

- SPI(Serial Peripheral Interface――串行外设接口)

- 多用于MCU与各种外围设备(括A/D转换器、D/A转换器、LCD、EEPROM、网络控制器、MCU)之间通信;

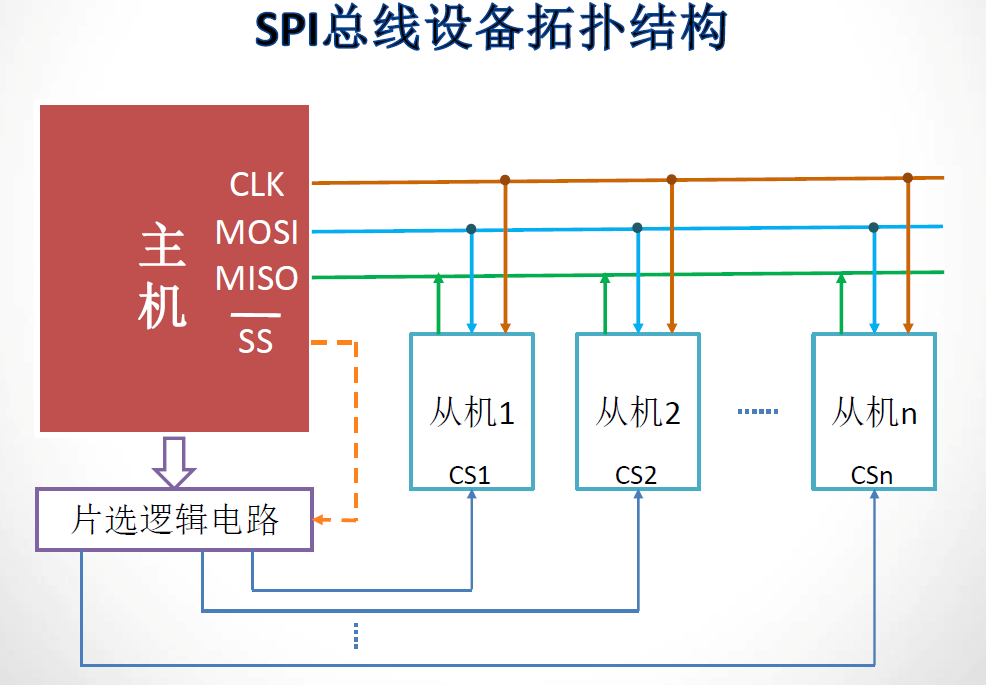

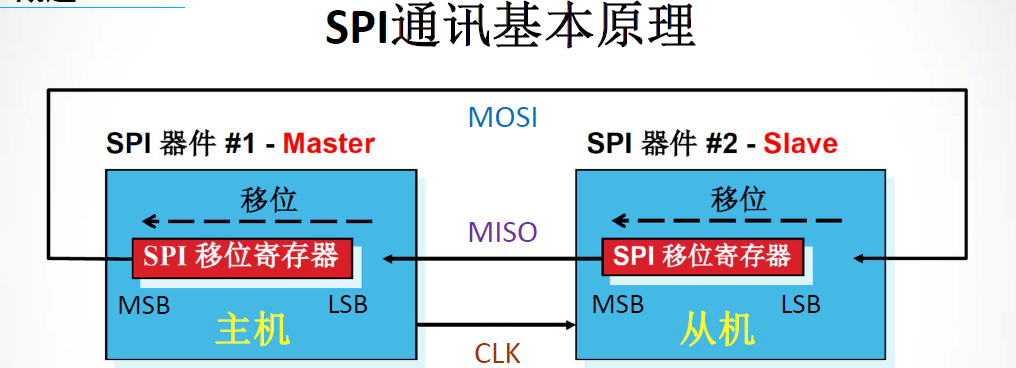

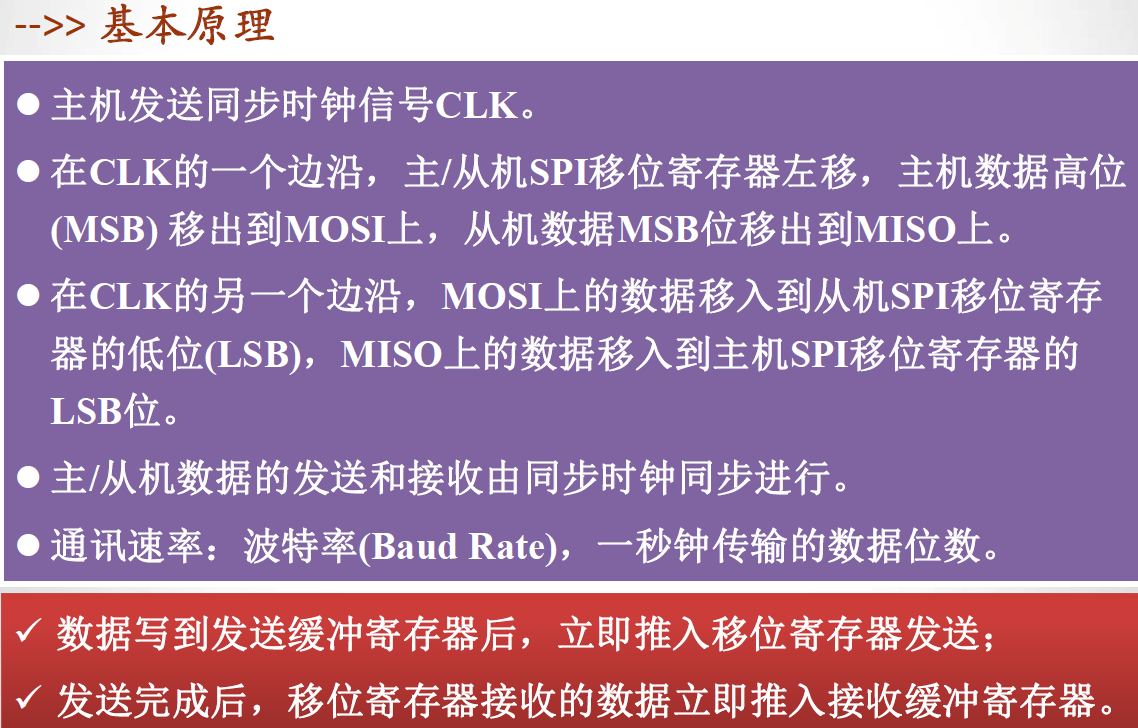

- SPI总线接口一般使用4根线:串行同步时钟线CLK、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS;

- SPI总线至少包括1根串行同步时钟信号线和1根数据线;

- 一主多从,主机发送同步时钟信号,控制通讯。

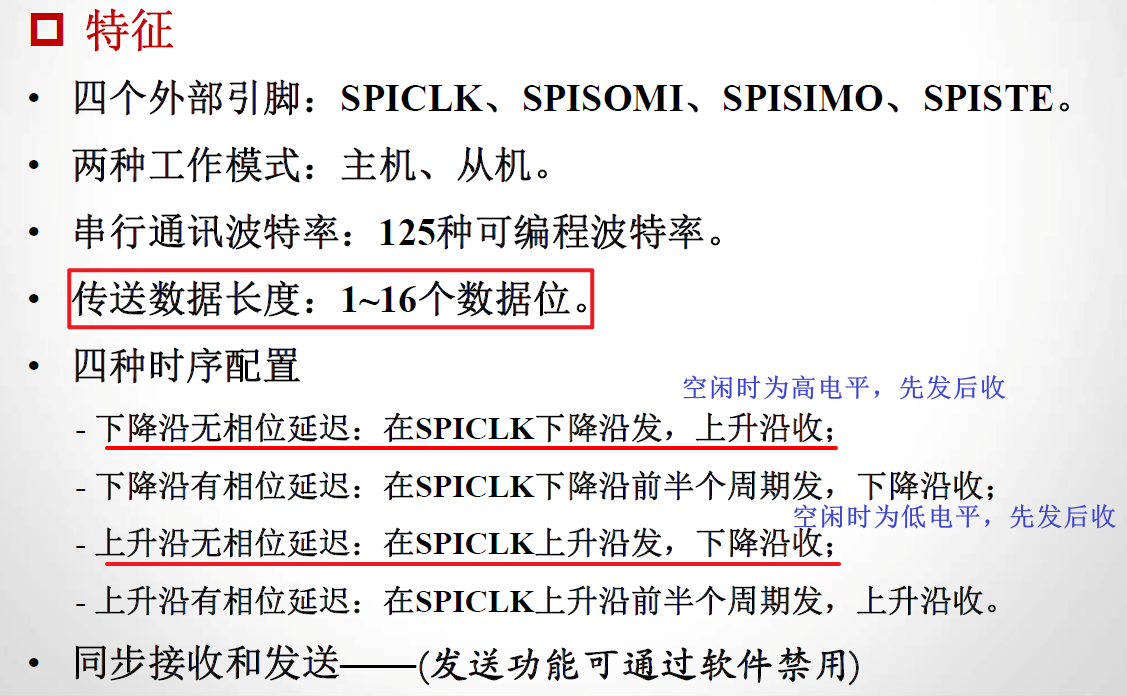

10.2 C28x 增强型SPI模块

F28335片上只有一个SPI模块

11. 串行异步通信SCI模块

11.1 串行通信概述

- 帧同步:收发双方不使用串行同步时钟,由双方各自的时钟实现数据帧的同步,但要求双方使用同一标称频率,允许有一定偏差。要正确传输数据帧,准确读取每一位时必须用各自的时钟同步的,为克服不同时钟的偏差,每个数据帧都有一个起始位进行同步;

- 典型的异步串行通信接口:RS-232、RS-422/485、USB等;

- RS-232C接口采用EIA电平:低电平为+3V~+15V;高电平为-3V~-15V(负逻辑),2发3收5接地;TTL与232电平转换芯片RS232;

- RS-485总线采用差分传输方式

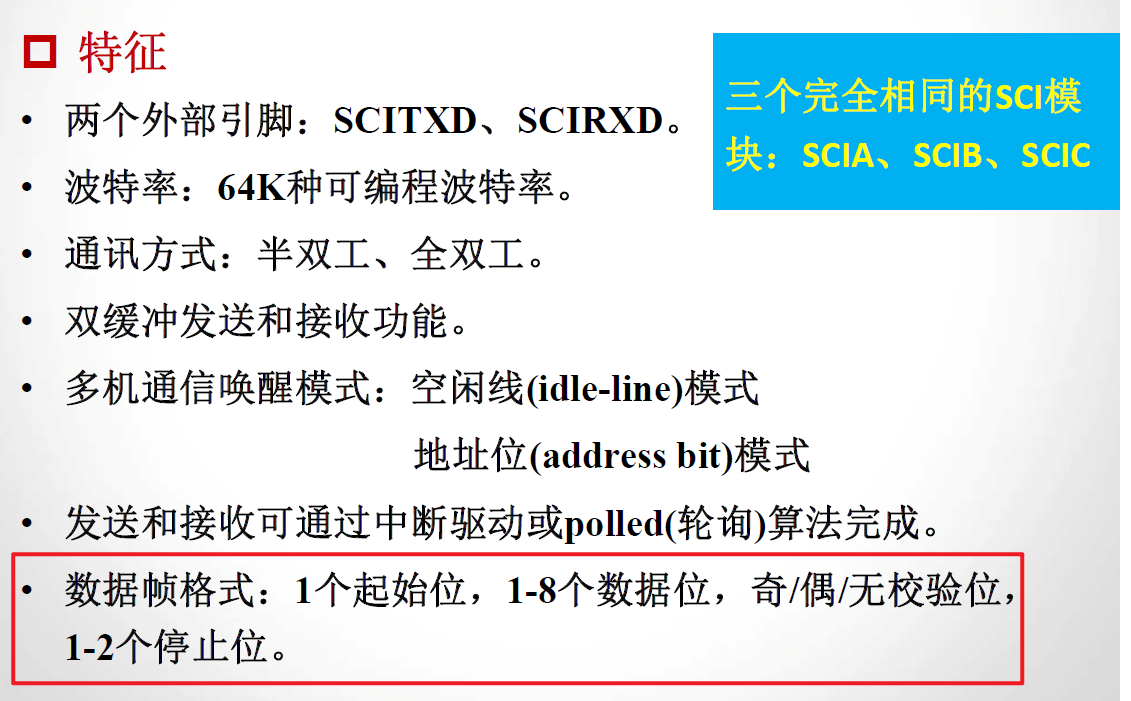

11.2 C28x 增强型SCI模块

F28335片上有三个完全相同的SCI模块:SCIA、SCIB、SCIC

12. 应用实例

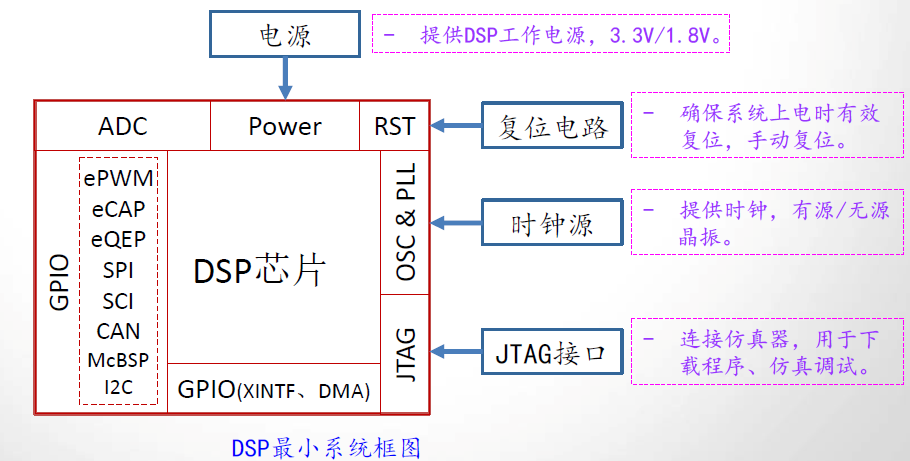

12.1 最小系统

确保DSP能正常工作的最小配置的系统

基本配置——DSP芯片、电源、复位电路、晶振、JTAG口

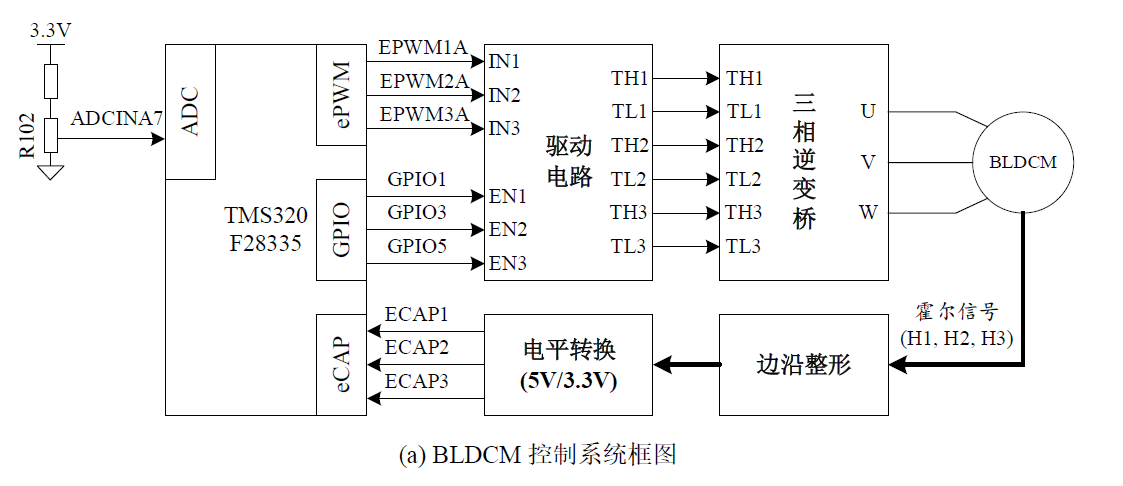

12.2 BLDCM实验

13. 简答题

- 数字信号处理算法有什么共性特点?为什么 DSP 具有强大的数字信号处理能力?

- 所需运算能力强

- DSP增强了运算能力,针对数字信号处理做了结构、指令优化和功能增强

- 冯诺依曼总线结构与哈佛结构相比,各自有什么样的优缺点?

- 哈佛结构:程序和数据总线分开,硬件结构复杂,价格高;优点:效率高

- 冯诺依曼结构:程序结构和数据结构合体,效率低 ;优点:简单便宜

- 定点型CPU 与浮点型 CPU 相比,各自有什么样的优缺点?

- 定点型CPU简单功耗低

- 当前TI C28系列DSP 常见的型号有哪些?其CPU 是定点型还是浮点型?其中,哪些型号的DSP 带有浮点协处理器(FPU)?

- F28335的编译调试环境是什么?汇编器、链接器、软件模拟器作用是什么?源程序文件、头文件、命令文件、运行支持库文件分别有哪些,有什么功能? Memory、Sections指令功能是什么?

- CCS

- 汇编器(Assembler):将汇编语言源文件转变为基于公用目标文件格式(COFF)的机器语言目标文件.obj;

- 链接器(Linker):将一个或多个由编译器或者汇编器生成的目标文件,外加库,链接为一个可执行文件,即目标代码(.out) .

- 软件模拟器(Simulator):脱离硬件的纯软件仿真工具。模拟运行DSP程序,同时对程序进行单步执行、设置断点,对寄存器/存储器进行观察、修改,以及统计某段程序的执行时间等。

- F28335的GPIO接口一共多少个?有哪些输入限制模式?配置步骤是什么?

- 88个

- 三种模式:SYSCLKOUT同步、采样窗限制、异步输入

- ①规划引脚功能 ②使能或禁止内部上拉功能③对输入引脚进行限制④配置引脚的功能.⑤对于通用数字IO口,配置引脚的方向⑥选择低功耗模式唤醒源⑦选择外部中断源

- 什么是中断?F28335的中断流程是什么?中断触发源有哪些?如何配置外设中断,使外设能向CPU发送中断请求且CPU能执行相应的中断服务子程序?

- 中断是CPU对系统发生某个事件作出的一种反应、中断事件发生时,CPU暂时中止正执行程序、保留现场,然后自动转去执行相应事件处理程序,处理完成后返回断点继续执行被打断的源程序;

- F28335中断流程是:中断请求→中断使能→CPU中断响应

- 中断触发源:软件中断、硬件中断、可屏蔽中断、不可屏蔽中断

- 关于增强型脉宽调制器(ePWM),有哪些计数事件?有哪些计数比较事件?有哪些动作限定(AQ)子模块的动作方式、触发事件?如何产生PWM波形?

- ①由TB子模块产生计数时基,CC子模块中的CMPA/CMPB与TBCTR 比较,产生计数事件.②由AQ子模块中的动作限定控制寄存器AQCTLA和AGCTLB独立配置EPWMXA输出和EPWMXB输出的触发事件.和动作形式.③PWM周期由TBPRD控制,占空比由CMPA/CMPB控制。

- 关于增强型捕获模块(eCAP),基本工作原理是?有哪些功能特点?连续、绝对时间戳捕获模式是什么?连续、差分时间戳捕获模式是什么?

- 关于ADC模块,有几个模拟通道、S/H采保器、转换核心、结果寄存器?A/D工作模式有哪些?如何配置采样率?

- SPI通信基本工作原理?一般包括几根总线?具有什么优势?有哪些时序配置?有哪些工作方式?增强特征是什么?

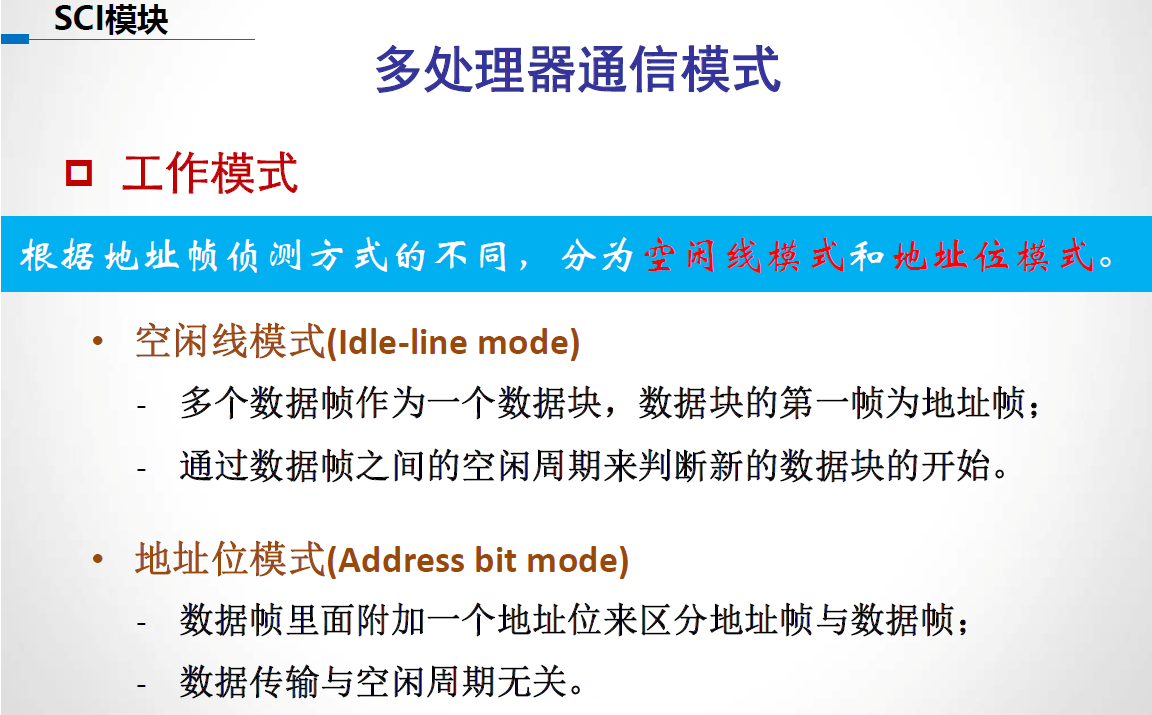

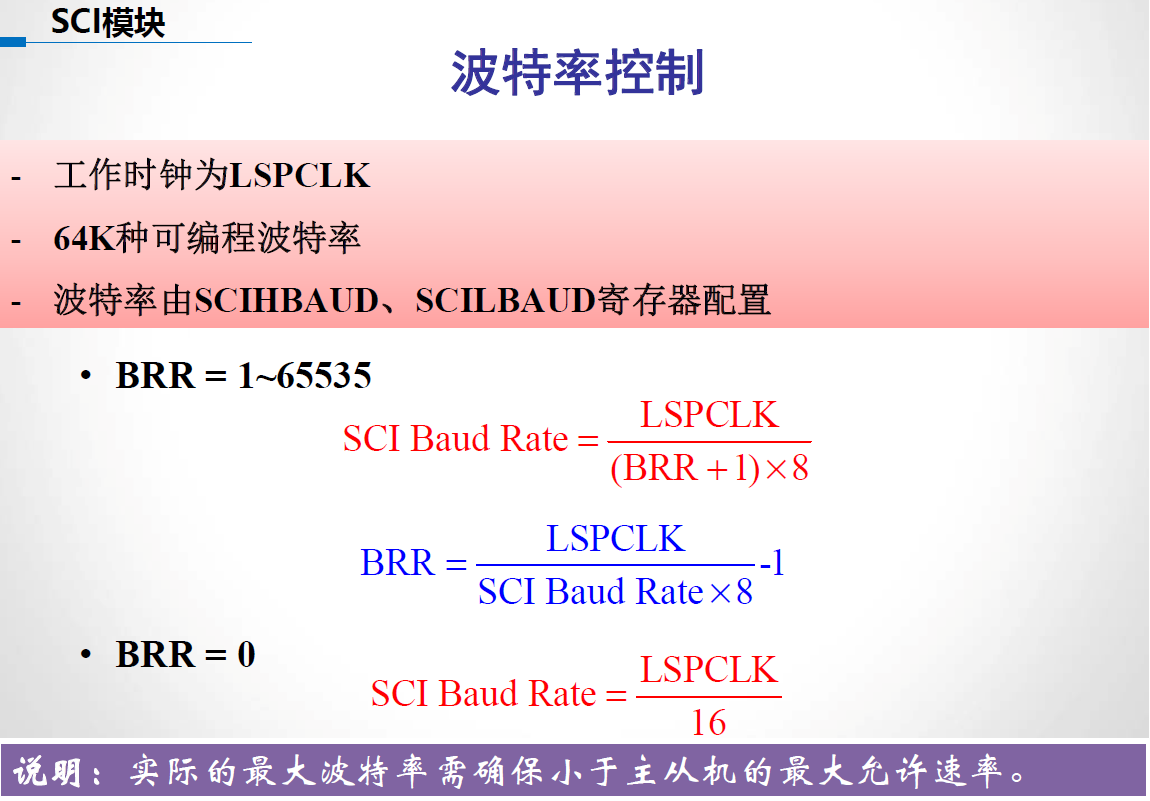

- 标准SCI模块结构是什么?数据帧格式是什么?空闲线模式和地址位模式是什么?

300

300

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?