这一部分,采用问答的方式来进行梳理;

- 什么是指令集体系?

指令集体系(Instruction Set Architecture,ISA)是规定处理器的外在行为的一系列内容的统称,它包括:

- 基本数据类型(data types)、

- 指令(instructions)、

- 寄存器(registers),

- 寻址基模式(addressing modes)、

- 存储体系(memory architecture)、

- 中断(interrupt)、

- 异常(exception)

- 外部 I/O(external I/O)等;

在这种情况下,一个软件可以运行在任何支持同一个指令集体系的不同处理器上面。

指令集体系是软件人员和处理器设计师之间的桥梁,软件人员可以不必关心处理器的硬件实现细节,只需要根据指令集体系就可以开发软件

而处理器设计人员则需要设计出符合指令集体系的处理器。

对于同一个指令集体系来说,有很多的实现方式,可以做得很简单但是速度很慢,也可以做得很复杂但是速度很快。

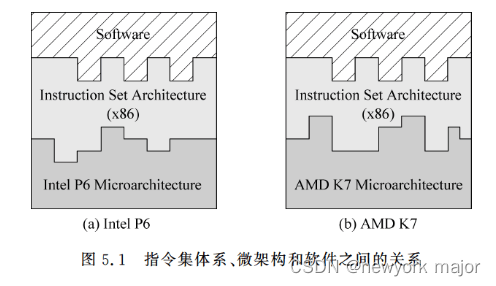

- 对一个指令集体系的硬件实现方式称为微架构(microarchitecture),

- 不同的设计师、不同的市场需求都会导致不同的微架构,

- 例如Intel的P6微架构[24](代表作品是Pentium 11处理器)和AMD的K7微架构(代表作品是Athlon处理器),两者都是基于x86指令集体系而设计的,但是它们在内部结构上并不相同,在性能表现上也是不同的,这可以用图 5. 1 来表示。

2. 指令集体系有哪些?

指令集从本质上可以分为复杂指令集(Complex Instruction Set Computer,CISC)和精简指令集(Reduced Instruction Set Computer,RISC)两种;

- 复杂指令集

特点是能够在一条指令内完成很多事情.

在计算机发展的早期,编译器技术并不发达,很多程序都需要使用汇编语言(甚至是机器语言)来编写,为了方便程序员编写汇编程序,处理器设计师设计出了越来越复杂的指令,这些指令可以使编程人员的工作得到简化。

在当时看来,硬件设计应该比编译器设计更容易一些,而且,在那个年代,内存的容量很有限,内存中的每一个字节都是宝贵的,于是业界就更倾向于使用高度编码、多操作数和长度不等的指令,能够使一条指令尽量做很多事情,并且减少内存的占用。

同时,寄存器是一种更昂贵的东西,当时的处理器中无法放入数量比较多的通用寄存器,而且,随着通用寄存器个数的增多,会使指令当中需要更多的位数来对其进行编码,这样也会导致指令占用更多的位数,也就占用了更多的内存(这些原因在现在看起来似乎是很滑稽的,但是在那个年代却是真实存在的),这些原因都是导致处理器设计师会让一条指令中完成尽可能多的任务的原因,

例如一条CISC指令“ADD[EAX],EBX”,可以完成从存储器中取数据,然后和寄存器中的数据进行运算,并将运算的结果写回存储器这样一系列的操作。

复杂指令集的这种设计方式在当时看起来是顺理成章的,只有在RISC的概念提出来之后,这种复杂的指令集才被人们称为CISC,当前统治桌面PC 领域的 x86指令集就是CISC指令集。

缺点:

- 尽管复杂指令集的很多特性让代码编写更加便捷,但是这些复杂特性的指令需要好几个周期才能够执行完;

- 而且大部分复杂的指令都没有被程序使用(80%的指令只在20%的时间被使用),

- 同时复杂指令集中通用寄存器的个数太少,导致处理器需要经常访问存储器,而随着处理器和存储器之间速度代沟的加大,经常访问存储器会导致处理器执行效率降低。

- 精简指令集

要克服这些缺点,就需要降低处理器设计的复杂度,以让出更多的硅片面积来放置寄存器,这就产生了精简指令集。

- 精简指令集使用了数量丰富的通用寄存器,所有的操作都是在通用寄存器之间完成的,要和存储器进行交互,就需要使用专门访问存储器的load/store指令,它们负责在寄存器和存储器之间交换数据。

- RISC指令的长度一般是等长的,这样大大简化了处理器中解码电路的设计,也便于流水线的实现;

- 但是相比复杂指令集,精简指令集需要更多的指令来实现同样的功能,导致其占用更多的程序存储器,虽然现在的存储器很廉价,但是这会导致Cache缺失率的上升,在一定程度上使RISC处理器的执行效率有所降低。

- 当前比较流行的精简指令集有ARM、MIPS 和PowerPC 等。

3. ARM/MIPS/RISC指令集体系,有什么区别?

- 指令集架构上,三者都是精简指令集架构(RISC)。相比CISC架构,RISC架构指令更为简单直观,一条指令只能完成一项操作,但处理速度更快。

- 指令集设计上:

- ARM和MIPS指令集的设计较为类似,都采用了寄存器作为数据操作的存储单元。寄存器是处理器内部的小型存储器,可以快速访问数据。因此,ARM和MIPS采用了寄存器理念,并且大量采用了寄存器操作。

- 而RISC-V则采用了寄存器和内存的组合。RISC-V中几乎所有的运算都是在寄存器之间完成的,但寄存器不够用的时候,它也支持内存操作。

- 指令集数量上,ARM和MIPS指令集包含的指令数量较多,可以完成更多的操作,但同时也会增加处理器的复杂度。RISC-V则遵循精简的设计理念,只包含了少量的指令集,主要是为了简化处理器的设计和处理速度。

- 指令集扩展性:

- RISC-V指令集设计时就考虑了拓展性,支持通过添加自定义指令和扩展来满足不同的应用需求。这是RISC-V与其他架构的一个重要区别。

- 相比之下,ARM和MIPS指令集的扩展性相对较差,需要通过硬件升级来支持新的指令集。

4. 什么是RISCV?

RISC-V 这个名字,代表了 UC Berkeley 大学设计的第五代RISC芯片。同时罗马数字"V"也暗示 了"变种(Variations)"和"向量(Vectors)",以支持各种体系结构研究,包括各种数据并行加速器,也是这个 ISA 设计的明确目标。

5. 什么是RISCV的模块化架构?

- 这些不同的模式之间虽然有很大的区别,但是通过共享的部分进行互相兼容,不管使用何种模式都能够获得优秀的性能表现;

5967

5967

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?